## Dynamic Load Balancing on Massively Parallel Computer Architectures

#### BACHELORARBEIT

zur Erlangung des akademischen Grades

Bachelor of Science (B.Sc.) im Fach Informatik

eingereicht am Institut für Informatik, Fachbereich Mathematik und Informatik Freie Universität Berlin

von

#### Florian Wende

geboren am 06.05.1985 in Dresden

Präsident der Freie Universität Berlin:

Prof. Dr. Peter-André Alt

Dekan des Fachbereich Mathematik und Informatik:

Prof. Dr. R. Klein

#### Gutachter:

1. Prof. Dr. H. Alt

2. Prof. Dr. A. Reinefeld

eingereicht am: 12.04.2013 Tag der mündlichen Prüfung:

#### **Abstract**

This thesis reports on using dynamic load balancing methods on massively parallel computers in the context of multithreaded computations. In particular we investigate the applicability of a randomized work stealing algorithm to ray tracing and breadth-first search as representatives of real-world applications with dynamic work creation. For our considerations we made use of current massively parallel hardware accelerators: Nvidia Tesla M2090, and Intel Xeon Phi. For both of the two we demonstrate the suitability of the work stealing scheme for the said real-world applications. Also the necessity of dynamic load balancing for irregular computations on such hardware is illustrated.

#### Keywords:

GPGPU, CUDA, MIC, Xeon Phi, Dynamic Load Balancing, Work Stealing, Ray Tracing, Breadth-First Search

#### Zusammenfassung

Vorliegende Bachelorarbeit befasst sich mit Methoden der dynamischen Lastbalancierung auf massiv parallelen Computern im Rahmen von mehrprozess gestützten Ausführungen von Programmen. Im einzelnen wird die Eignung eines randomisierten Work-Stealing Algorithmus für die Ausführung realer Anwendungen mit dynamischer Arbeitserzeugung, wie Ray-Tracing und Breitensuche, untersucht. Für die entsprechenden Betrachtungen werden aktuelle massiv parallele Hardwarebeschleuniger vom Typ Nvidia Tesla M2090 und Intel Xeon Phi verwendet. Für beide Beschleunigertypen konnte die Tauglichkeit des Work-Stealing Schemas für die genannten Anwendungen gezeigt werden. Ebenfalls wird die Notwendigkeit der Verwendung dynamischer Lastausgleichsmethoden für irregulare Berechnungen auf der genannten Hardware verdeutlicht.

#### Schlagwörter:

GPGPU, CUDA, MIC, Xeon Phi, Dynamische Lastbalancierung, Work-Stealing, Ray-Tracing, Breitensuche

## **Contents**

| 1. | Intro | oductio  | n                                                    | 1  |

|----|-------|----------|------------------------------------------------------|----|

|    | 1.1.  | Relate   | d Work                                               | 2  |

|    | 1.2.  | Contri   | bution of the Thesis                                 | 3  |

| 2. | Dyn   | amic T   | ask Parallelism in Multithreaded Computations        | 5  |

|    | 2.1.  | Multit   | hreaded Computations                                 | 5  |

|    | 2.2.  | Dynan    | nic Load Balancing                                   | 6  |

|    |       | 2.2.1.   | Dynamic Load Balancing Methods                       | 8  |

|    | 2.3.  | Greedy   | y-Scheduling of Multithreaded Computations           | 9  |

|    |       | 2.3.1.   | The Busy-Leaves Algorithm                            | 12 |

|    | 2.4.  | A Ran    | domized Work-Stealing Algorithm                      | 13 |

| 3. | Wor   | k Steal  | ing on GPU and Intel Xeon Phi                        | 17 |

|    | 3.1.  | Nvidia   | Fermi GPU Architecture                               | 17 |

|    | 3.2.  | Intel N  | Many Integrated Core (MIC) Architecture              | 19 |

|    | 3.3.  | Proble   | m Description                                        | 21 |

|    | 3.4.  | Multit   | hreaded Data Structures                              | 22 |

|    |       | 3.4.1.   | Blocking Dequeue                                     | 23 |

|    |       | 3.4.2.   | Non-Blocking Dequeue                                 | 24 |

|    |       | 3.4.3.   | Performance Evaluation                               | 27 |

|    | 3.5.  | Schedu   | uling Multithreaded Computations on GPU and Xeon Phi | 32 |

|    |       | 3.5.1.   | Dependency Resolution                                | 32 |

|    |       | 3.5.2.   | Evaluation of the Implementation                     | 35 |

| 4. | Арр   | lication | Scenarios                                            | 41 |

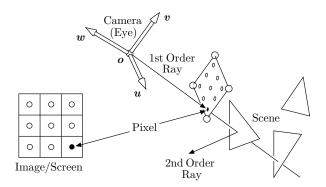

|    | 4.1.  | Ray T    | racing                                               | 41 |

|    |       | 4.1.1.   | The Ray Tracing Method                               | 41 |

|    |       | 4.1.2.   | Implementation Details                               | 43 |

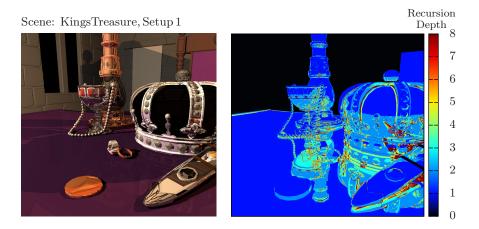

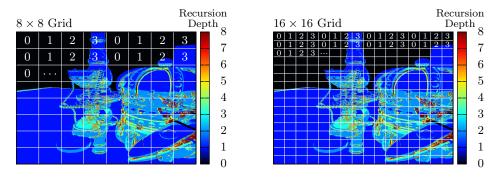

|    |       | 4.1.3.   | Ray Tracing and Load Balancing                       | 45 |

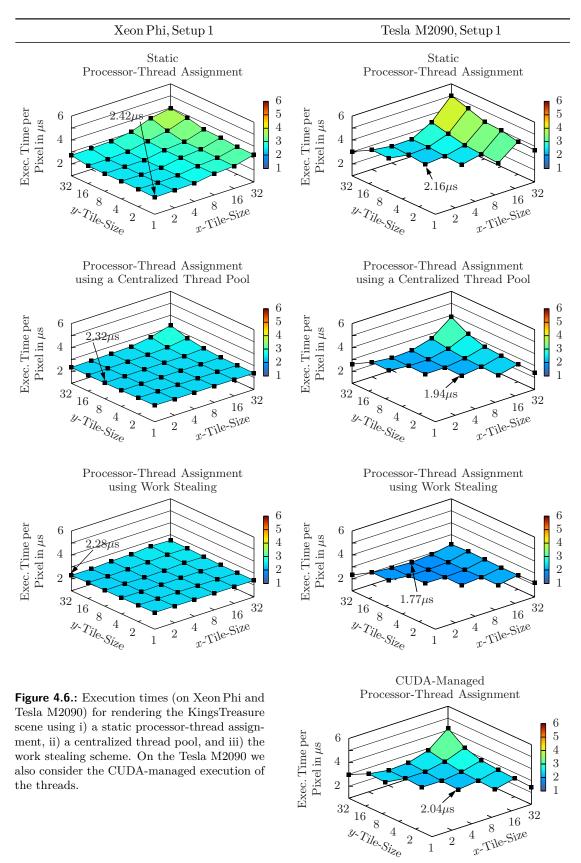

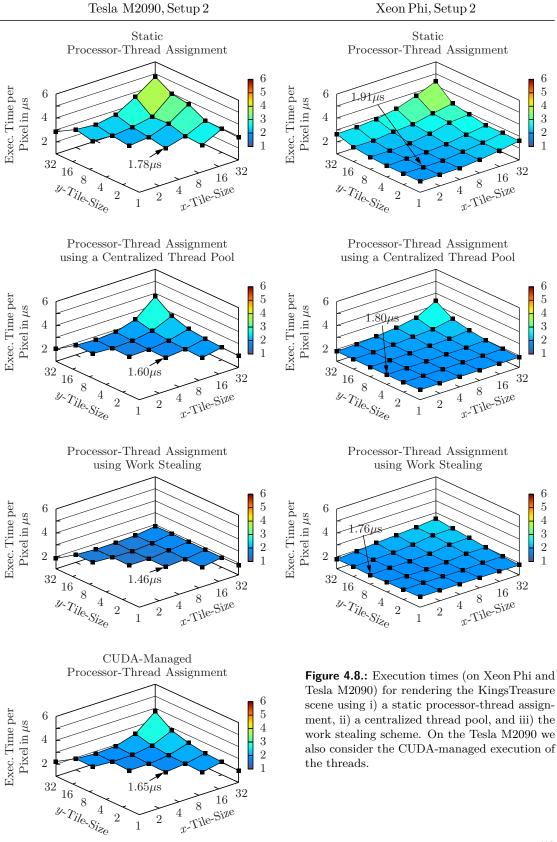

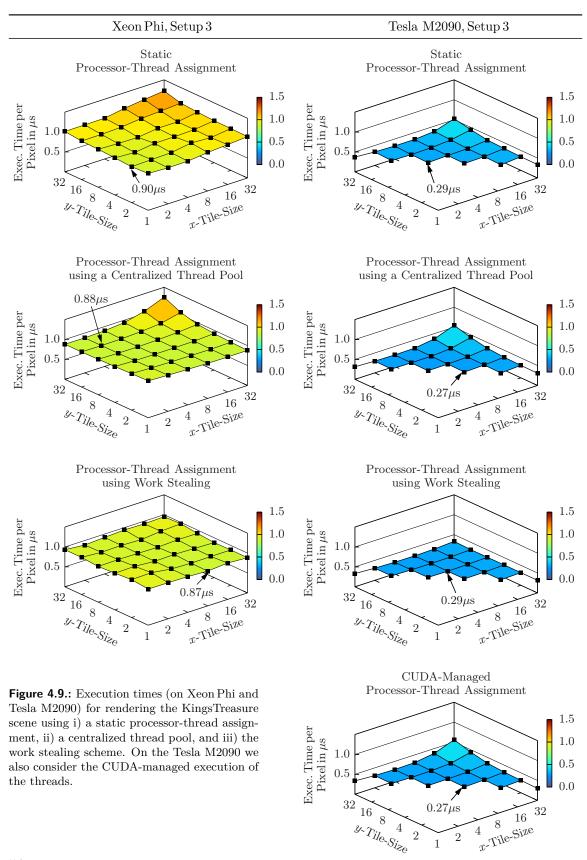

|    |       | 4.1.4.   | Performance Evaluation on GPU, Xeon Phi, and CPU     | 47 |

|    |       | 4.1.5.   | Validation of the Implementation                     | 55 |

#### Contents

|    | 4.2. | Bread   | th-First Search                                                         | 55 |

|----|------|---------|-------------------------------------------------------------------------|----|

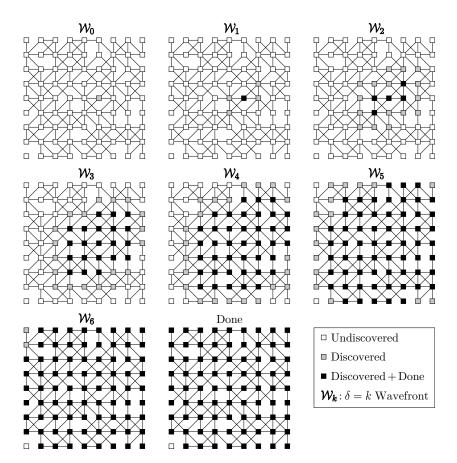

|    |      | 4.2.1.  | Parallel Implementation                                                 | 58 |

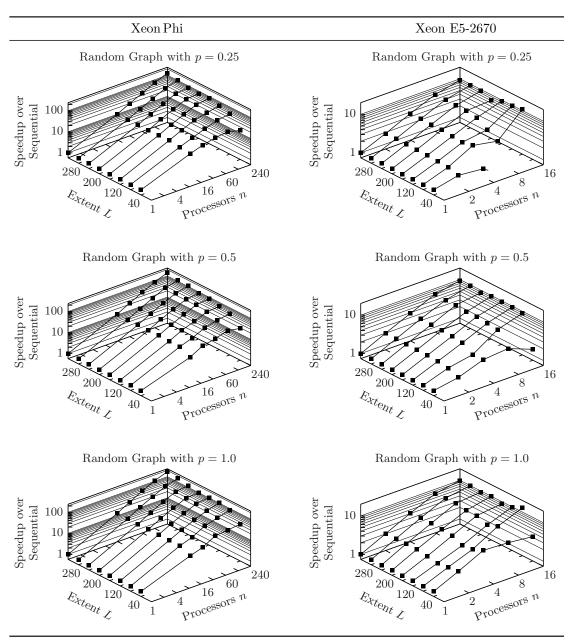

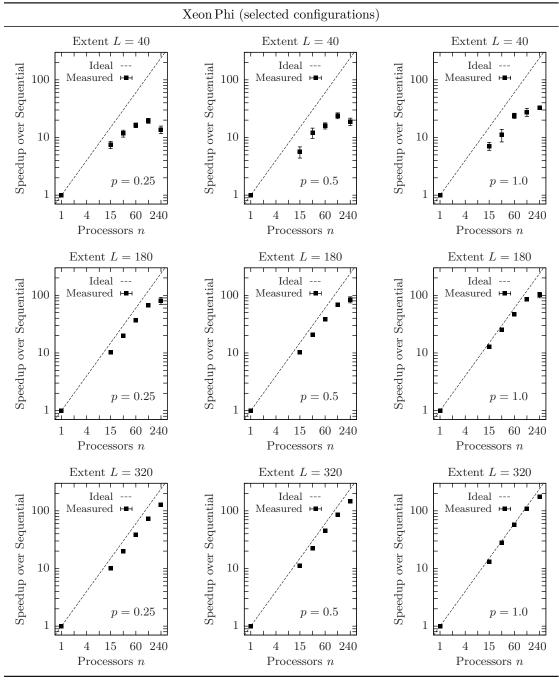

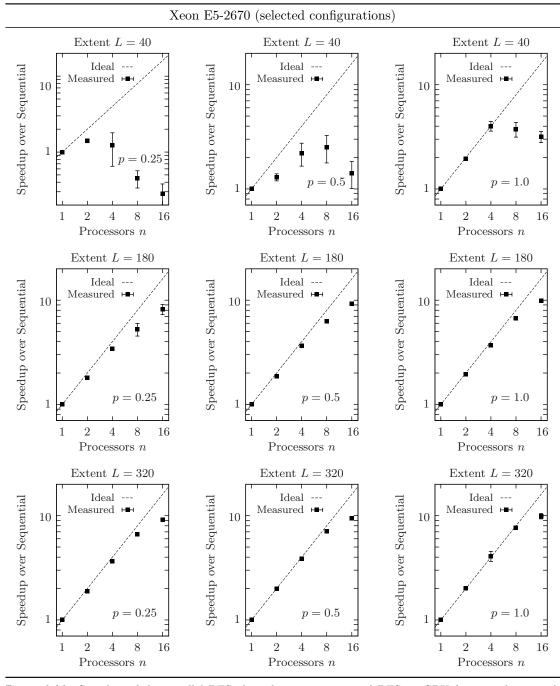

|    |      | 4.2.2.  | Performance Evaluation on Xeon Phi and CPU $\ \ldots \ \ldots \ \ldots$ | 60 |

|    |      | 4.2.3.  | Validation of the Implementation                                        | 66 |

|    |      | 4.2.4.  | Scalable Work Stealing & State of the Art                               | 66 |

| 5. | Sum  | ımary & | ն Conclusion                                                            | 67 |

| Α. | Bloc | king D  | equeue, Non-Blocking Dequeue, Load Balancing                            | 69 |

|    | A.1. | Blocki  | ng Dequeue (GPU)                                                        | 69 |

|    | A.2. | Non-B   | Blocking Dequeue (GPU)—Extended Version                                 | 71 |

|    | A.3. | Source  | e Codes                                                                 | 76 |

| В. | Ray  | Tracing | g                                                                       | 77 |

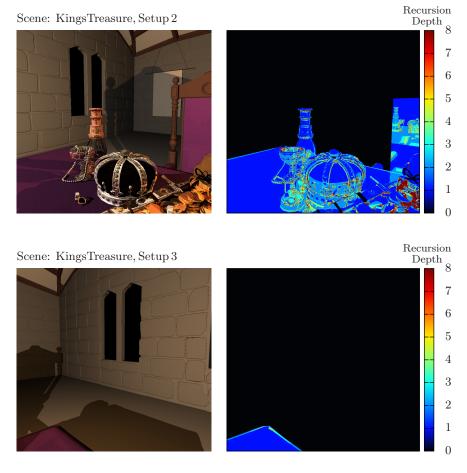

|    | B.1. | Work    | Distribution for Rendering the Kings<br>Treasure Scene, Setup $2/3$     | 77 |

|    | B.2. | Source  | e Codes                                                                 | 78 |

| C. | Brea | adth-Fi | rst Search: Source Codes                                                | 79 |

## 1. Introduction

The development of parallel computer systems and concepts of parallel programming both have their origin in the mid-1960s. Primarily driven by the strongly increasing demand for computational power in almost all kinds of scientific fields of research, single processor systems rapidly evolved to those containing multiple processors. Today we are faced with multi-core CPUs in standard consumer products, high-performance computer systems in data centers, and vector processors and hardware accelerators in special purpose computers. Currently, the use of massively parallel hardware accelerators drive the raw compute performance of the fastest systems towards several PetaFLOPS<sup>1</sup> and beyond.

For about 5 years, programmers from different fields of research report about significant performance gains when executing adapted programs on GPUs (GPU—Graphics Processing Unit) compared to executing them on a standard multi-core CPU. While GPUs are well suited for data parallel applications with known launch bounds, dynamic task parallelism is a discipline even current GPUs seem to be at a disadvantage to multi-core CPUs [TLO12]. The point why GPUs seem to be less suitable for such kind of applications is irregularities in program control flows and task execution times, and task (re)distribution at runtime when work is created dynamically. According to Burtscher et al. [BNP12], irregularities in control flow and memory access patterns do not necessarily result in bad performance of GPU programs. For almost all application domains considered by the authors—graph theory, satisfiability theory, computational geometry, to name a few—they found current GPUs be less sensitive to unfortunate memory access patterns due to the introduction of data caches on the latest models. The more interesting issue thus is dynamic task parallelism, which is more or less in contrast with the functioning of the GPU hardware.

Similar issues may also apply to hardware accelerators other than GPUs, and in particular to heterogeneous computer systems made up of different kinds of processors.

<sup>&</sup>lt;sup>1</sup>FLOPS—Floating Point Operations Per Second. 1 PetaFLOPS =  $1 \times 10^{15}$  FLOPS.

#### 1.1. Related Work

With respect to dynamic work creation, there is a broad class of algorithms that actually develop their parallelism just at runtime—divide and conquer algorithms, for instance. For such algorithms to execute on massively parallel computers, a mechanisms is needed that (re)distributes newly created work to processors that are non-busy at that time. Investigations on applying load balancing schemes, known to serve well on traditional multiprocessor systems, to the GPU can be found in [CT08, CGSS11, TLO12], for instance. While Cederman et al. [CT08] and Chatterjee et al. [CGSS11] obtain good results with a work stealing based load balancing scheme (the authors do not handle dependencies between tasks), Tzeng et al. [TLO12] have their focus on irregular workloads with dependencies. Unfortunately, the task parallel programming model for the GPU proposed by the authors was inferior to its CPU counterpart.

Besides using load balancing schemes on a particular kind of multiprocessor, distributing work amongst the components of a heterogeneous system is another challenging application domain of load balancing schemes. In this field several investigations have been done. Well known outcomes here are the StarPU [ATNW11] and the X-Kaapi [GLFR12] programming APIs. Both of the two aim for making the heterogeneous computer's compute units—CPU cores, GPUs, and maybe other hardware accelerators—execute a multithreaded computation in cooperative manner. For that purpose X-Kaapi implements a work stealing scheduler, whereas StarPU allows to dynamically switch between different scheduling schemes including work stealing. The key difference to using load balancing on the hardware accelerator itself is the abstraction of the underlying hardware. X-Kaapi and StarPU abstract accelerators like CPU cores. Large portions of the computation are scheduled to the accelerator in hope of fast execution (offload computation), while small portions are assigned to the CPU core(s). Load balancing on the accelerators is not addressed by these APIs (to our knowledge).

Other examples of using hardware accelerators for offload computations are MAGMA, and TBLAS [SYD09, SHT<sup>+</sup>12]. Both libraries focus on solving dense linear algebra problems. The approach is to replace BLAS (Basic Linear Algebra Subroutine) routines by so-called task-based linear algebra subroutines that are dynamically created during the execution of the computation, and then are distributed to available processors. The scheduling mechanism has to respect dependencies between the tasks.

At the core of all these APIs and libraries is the integration of massively parallel hardware accelerators. As vendors of such accelerators are going to provide their devices with increasingly more and more processors, further investigations on load balancing schemes seem to be crucial to make a wide range of applications, including those with irregular workloads, benefit from the massive compute performance of the hardware.

#### 1.2. Contribution of the Thesis

In this thesis we extend the aforementioned investigations on load balancing using a current Nvidia GPU and Intel's Xeon Phi hardware accelerator. We want to emphasize that our focus will be on load balancing on the hardware accelerator itself. A combination with StarPU or X-Kaapi might be the starting point of further investigations. Unlike in [CT08] and [CGSS11], we also compare the performance of our implementations against equivalent implementations on a standard x86 multi-core CPU—the functioning of the load balancing schemes on the GPU and the Xeon Phi does not mean that the overall performance of a respective application is superior to its CPU version, as experienced for applications with no irregular workloads. We mimic the task parallel Cilk programming model—implementing work stealing on x86 CPUs and the Xeon Phi—on both GPU and Xeon Phi, and evaluate its performance by directly comparing against Cilk (we also address dependencies between tasks). A downgraded version of this load balancing scheme will be applied to real-world problems, ray tracing and breadth-first search, namely.

Chapter 2 is concerned with multithreaded computations and dynamic load balancing. After briefly introducing the graph theoretical model of multithreaded computations, the focus will be on scheduling aspects. We will draw on the work of D. Cederman and P. Tsigas [CT08], and R. D. Blumofe and Ch. E. Leiserson [BL93, BL99].

In Chapter 3 we introduce the massively parallel computer hardware used in this thesis—Nvidia Fermi GPU, and Intel Xeon Phi, namely. We then are concerned with the implementation and the evaluation of concurrent data structures—'lock' and 'dequeue'. Further, we give an implementation of the work stealing load balancing scheme that puts the graph theoretical model of multithreaded computations into practice.

Chapter 4 applies the work stealing scheme to real-world applications, ray tracing and breadth-first search (BFS). We evaluate the performance of the ray tracer using a static work distribution scheme, a centralized work pool, and work stealing. For the BFS algorithm, we restrict our considerations to the Xeon Phi and the CPU.

Chapter 5 summarizes the results of this thesis. We also list some interesting issues that might serve as a basis for further investigations.

# 2. Dynamic Task Parallelism in Multithreaded Computations

This chapter is concerned with scheduling schemes in the context of multithreaded computations. After having briefly introduced the notion of a multithreaded computation and its graph theoretical representation, we list common approaches to handle such computations. In particular, we amplify greedy schedules, and introduce a randomized work stealing scheme. Throughout this chapter, we follow the work of D. Cederman and P. Tsigas [CT08], and R. D. Blumofe and Ch. E. Leiserson [BL93, BL99].

#### 2.1. Multithreaded Computations

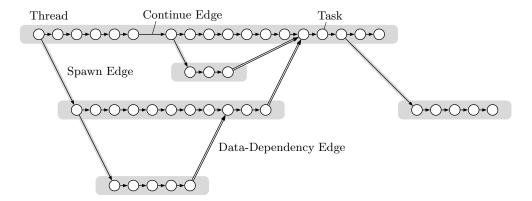

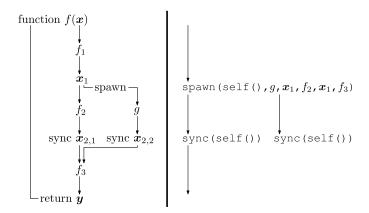

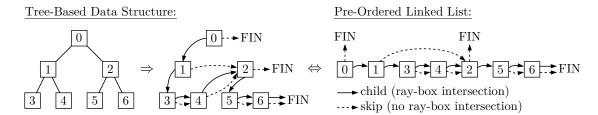

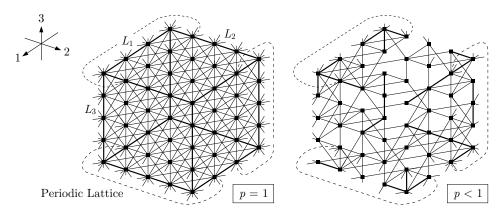

A multithreaded computation is a composition of threads, which are sequential orderings of tasks each. A task here refers to an abstract operation which in the context of the computation is atomic, that is, for the multithreaded computation it is not split up into subtasks. Tasks  $t_j$  within a thread  $\mathcal{T}$  are executed in a predefined order, with tasks that are direct successors being connected by continue edges going from a task  $t_j$  to its direct successor  $succ(t_j)$ . Threads may create new threads during their execution, called child threads. The thread which spawns the child thread acts as the parent of the child, and as an ancestor of the child's child(ren). In this way, threads are organized into an activation tree, with parent threads and child threads connected by spawn edges going from the parent to the child thread. If there is some kind of producer-consumer relation between threads, say, thread  $\mathcal{T}_0$  is the consumer and threads  $\mathcal{T}_{i:1 \leq i \leq n}$  are the producers, then there are n data-dependency edges going from any task  $t_j$  in  $\mathcal{T}_{i:1 \leq i \leq n}$  to a somehow distinguished task  $t_*$  in  $\mathcal{T}_0$ , where  $t_*$  consumes the data. A multithreaded computation can be represented by a directed graph with its nodes corresponding to tasks, and with the different types of edges introduced above (see Fig. 2.1).

An execution schedule for a multithreaded computation is a task-processor mapping which at each step of the schedule assigns a task to each processor of a parallel computer for execution. The schedule depends on the multithreaded computation itself, and on the number of processors of the parallel computer used for the execution. At every step of the schedule each processor is assigned at most one task. For an execution schedule

#### 2. Dynamic Task Parallelism in Multithreaded Computations

**Figure 2.1.:** Representation of a multithreaded computation by means of a directed graph. Threads are denoted by gray shaded boxes, and tasks correspond to open circles. Threads are connected by spawn edges and data-dependency edges (if there are any), whereas successive tasks within a thread are connected by continue edges. The image is based on similar drawing in [BL99].

to be valid, ordering constraints given by continue and data-dependency edges must be preserved, that is, tasks can be executed if and only if all its predecessor tasks, connected to it via continue or data-dependency edges, have been executed. The execution of the consuming thread thus cannot continue until the respective data dependencies (if there are any) are resolved—in the meantime the consuming thread *stalls*.

For subsequent considerations we assume that there is a valid execution schedule for the multithreaded computation of interest. Then the multithreaded computation can be represented by a directed acyclic graph (DAG).<sup>1</sup> We further assume that for each thread the number of data-dependency edges incident on it is bounded above, so that the computation can be performed within a finite amount of time, and with a finite amount of computer resources.

### 2.2. Dynamic Load Balancing

A general multithreaded computation consists of a certain number of threads with some of them created (spawned) by other threads during their execution (see Fig. 2.1). Since spawning threads from within a thread is somehow similar to a subroutine call, except that the spawned thread can be executed concurrently to the thread that did the spawn, a scheme is needed that presents one of the two threads to processors that are currently non-busy, and allows any of them to start executing this thread. In this way the amount of parallelism can be dynamically adapted to the resources provided by the computer system. This point is addressed by dynamic load balancing schemes.

<sup>&</sup>lt;sup>1</sup>If the graph would not be acyclic, the presence of cycles results in the computation will stall at any step due to data dependencies that cannot be resolved.

At the core of load balancing in the context of multithreaded computations are concurrent data structures that on the one hand allow several competing processors each to access the data atomically, that is, without being interrupted by other processors, and on the other hand assure high throughput and high availability. To meet these requirements, several popular load balancing schemes draw on atomic hardware primitives such as compare-and-swap and test-and-set. Whether these primitives are available or not depends on the hardware. However, all these load balancing schemes have in common that a shared data object—queue, dequeue, stack, or heap, for instance—is used to store all threads that are created before and during the execution of the application. When the data structure is 'not empty' processors that are ready for work repeatedly try to get a thread from it and start executing the respective thread's tasks until the computation is done. Processors which spawn threads 'add' them to the data structure to enable other processors to acquire these threads and so to leave their non-busy state.

At the core of accessing a shared data structure is *synchronization* in order to assure atomicity in the sense described above. Synchronization schemes can be divided into the following categories [CT08, TZ00]:

Blocking: Shared data objects are altered only within critical sections which are surrounded by a pair of 'locking' and 'unlocking' functions, traditionally based on mutexes or semaphores ('lock' for simplicity). A processor that enters the critical section is said to hold the lock associated with the data structure and the critical section, respectively. If the processor leaves the critical section the lock is released and other processors may acquire it. Processors that try to enter the critical section wait for the event 'lock was released and can be acquired' to occur. In this way all alterations with respect to the shared object are done mutual exclusive. Unfortunately, blocking access to shared objects suffers from contention (multiple processors repeatedly check if a lock has been released or not, causing expensive busy-waiting), convoying (the processor holding the lock is preempted and thus is unable to release the lock until it is brought back for execution, causing other processors to wait), and from the risk of deadlocks (the processor holding the lock crashes and the shared object is locked permanently, or two or more processors circularly wait for locks held by other processors).

Non-blocking (Optimistic Concurrency Control): Shared data objects can be accessed by multiple processors at the same time without enforcing mutual exclusion. The risk of deadlocks thus is eliminated. Atomicity with respect to altering the shared object in a consistent way is guaranteed by applying changes to the object using atomic hardware primitives only—just one processor, out of a set of concurrent processors accessing the data object, can finish its operation(s) successfully such

#### 2. Dynamic Task Parallelism in Multithreaded Computations

that the state of the object before and at the end of the operation is identical, that is, none of the other processors has altered the object in the meantime. All processors that failed altering the data object successfully may have a further try if necessary.

**Lock-free:** As multiple processors concurrently alter a shared data object, with just one of them achieving success while the other ones may repeatedly try again, there is the possibility for individual processors to starve, that is, some processors will never be successful. However, system-wide progress is guaranteed.

Wait-free: In addition to lock-freedom, wait-freedom guarantees for each processor to complete its altering of the shared object within a bounded number of steps. Wait-freedom thus guarantees starvation-freedom.

Which kind of synchronization scheme to use depends on the application and on the particular computer system used. While for massively parallel computer systems lock-free (and wait-free) synchronization mechanisms are the matter of choice, due to almost linear scaling with number of processors [TZ00], lock-based synchronization schemes might be suitable for systems with just a few processors.

Although lock- and wait-free synchronization methods are superior to blocking ones, they are usually harder to design.

#### 2.2.1. Dynamic Load Balancing Methods

In this subsection we summarize some load balancing methods described in [CT08]. Other than the authors we do not explicitly distinguish between thread list, thread queue, and thread dequeue, since concrete implementations are usually array-based, and 'list', 'queue', 'dequeue', etc. then are just different prescriptions of which elements of the array can be accessed next. We therefore want to refer to these data structures as thread pools hereafter.<sup>2</sup>

In the context of multithreaded computations, we distinguish between using a single centralized thread pool or multiple distributed thread pools, processors can get threads from. Further we may distinguish between thread pools that use blocking and those using non-blocking synchronization mechanisms. Also the question of whether our thread pool(s) should allow adding newly created threads at runtime or not might be reasonable.

<sup>&</sup>lt;sup>2</sup>In [CT08] the meaning of 'thread' and 'task' is different from what we have used so far. In the notation of the authors tasks map onto threads, and threads executing tasks map onto processors executing threads.

With respect to these issues, the following combinations are conceivable:

Blocking centralized thread pool: A simple thread pool protected by a lock. Since only one processor can access the pool at any time, there is huge potential for contention and convoying. If processors frequently access the pool, the available parallelism is limited by the thread pool itself, rendering it unsuitable for massively parallel computer systems. Threads created at runtime can be easily added to the pool unless its capacity is reached.

Non-blocking centralized thread pool: A pool which instead of a lock uses atomic hardware primitives to assure mutual exclusion. Although there is no contention, for a large number of processors trying to access the pool, the delay, due to just one of the competing processors successfully removes or adds a thread at any time, may become extremely large. Thus, the actual available parallelism is again limited by the thread pool itself when used for massively parallel computers.

**Blocking distributed thread pools:** Compared to the blocking centralized thread pool, the available parallelism should be measurably larger as processors may access different pools when trying to acquire new threads. For each processor selecting a pool for access can be done, for instance, in round robin fashion or at random.

**Non-blocking distributed thread pools:** Similar to the non-blocking centralized thread pool, but with processors selecting pools for access, for instance, in round robin fashion or at random.

For (massively) parallel computers the latter approach is the most promising. In fact, it is the data structure used for the work stealing algorithm, with each processor being the owner of a non-blocking (lock-free) thread pool. The owner can add and remove threads from its pool, whereas all other processors are just allowed to remove (or *steal*) threads, hence the name *work stealing*. Another scheduling paradigm which addresses scheduling multithreaded computations is *work sharing*, where dynamically created threads are migrated to other processors in hopes of distributing the work to underutilized processors. The work stealing scheme will be described in Sec. 2.4. Beforehand, we introduce some useful notation and amplify the greedy-scheduling theorem.

### 2.3. Greedy-Scheduling of Multithreaded Computations

Greedy schedules are those in which at each step of the execution  $p \leq P$  tasks execute on up to P processors if at the respective step p tasks are ready for execution. To get a deeper insight into greedy schedules of multithreaded computations, we need to introduce some notation. We again follow R. D. Blumofe and Ch. E. Leiserson [BL99, BL93].

#### 2. Dynamic Task Parallelism in Multithreaded Computations

According to Sec. 2.1, a multithreaded computation can be represented by a boundededge DAG, with nodes corresponding to tasks, and tasks being connected by continue, spawn, and data-dependency edges. Tasks that are connected by continue edges belong to the same thread, and the multithreaded computation consists of a finite number of threads with some of them created at runtime by other threads.

Since general multithreaded computations with arbitrary data dependencies cannot be scheduled efficiently, subsequent considerations are for the subclass of strict and fully-strict multithreaded computations. A multithreaded computation is said to be *strict* if for all threads all data-dependency edges from a thread go to an ancestor of the thread in the activation tree. It is said to be *fully-strict* if for all threads all data-dependency edges from a thread go to its parent thread. Strict and fully-strict computations correspond to those that can be executed in a depth-first manner on a single processor system.

To quantify the space and time bounds for an execution schedule  $\mathcal{X}$  of a multithreaded computation, we assume a computer system with P processors. For each thread  $\mathcal{T}_i$  that is executed, an activation frame  $\mathcal{F}_i$  is allocated, and the thread is said to be alive.  $|\mathcal{F}_i|$  refers to the amount of memory used to store all data needed for the execution of thread  $\mathcal{T}_i$ . The activation frame  $\mathcal{F}_i$  of a thread  $\mathcal{T}_i$  is deallocated if and only if  $\mathcal{T}_i$  is done and all its children's activation frames have been deallocated. The thread then dies. At a given step x of the execution schedule  $\mathcal{X}$ , the portion of the activation tree  $\mathcal{A}$  consisting of those threads that are alive at that step defines the activation subtree  $\mathcal{A}(x)$  at step x. The space S(x) required for the execution schedule at step x thus is the size of all activation frames used by all threads in the activation subtree A(x), that is,  $S(x) = \sum_{i:\mathcal{T}_i \in \bar{\mathcal{A}}(x)} |\mathcal{F}_i|$ . The space requirement  $S_P(\mathcal{X})$  for a P-processor execution schedule of a multithreaded computation  $\mathcal{X}$  is the maximum such value over the course of the execution, that is,  $S_P(\mathcal{X}) = \max\{S(x) : x \in \mathcal{X}\}$ . We define the activation depth of a thread to be the sum of the sizes of its own activation frame and the activation frames of all its ancestors. The activation depth of the multithreaded computation, referred to as  $S_1$ , then is the maximum activation depth of any of its threads. It is the minimum amount of space possible for a 1-processor execution of the computation in a depth-first manner. In particular we have  $S_1(\mathcal{X}) \leq S_P(\mathcal{X})$ .

For the time bound, we define the work of the computation  $T_1$  as the number of tasks the computation is made up of. If we assume all tasks be unit-time tasks, then  $T_1$  is the time it would take 1 processor to execute the computation, since 1 processor can execute only 1 task per time step. If we define the DAG depth of a task as the longest path in the DAG representation of the multithreaded computation that terminates at that task, the DAG depth of the computation is the maximum DAG depth of any task in the computation. It is denoted  $T_{\infty}$ , since even with an infinite number of processors progress can always be made along the critical path of the computation—the path in the

DAG with its length equal to the DAG depth. Let  $T_P(\mathcal{X})$  be the execution time of the computation with P processors using the execution schedule  $\mathcal{X}$ , then  $T_P(\mathcal{X}) \geq T_\infty(\mathcal{X})$ . Similarly, it should be clear that  $T_1/P \leq T_P(\mathcal{X})$ , since with P processors a maximum of P tasks can be executed at any time step. An upper bound on the execution time of a multithreaded computation using P processors can be obtained by greedy schedules.

**Theorem 1: (Greedy-Scheduling Theorem)** For any multithreaded computation with work  $T_1$ , DAG depth  $T_{\infty}$ , and for any number P of processors, any greedy execution schedule  $\mathcal{X}$  achieves  $T_P(\mathcal{X}) \leq T_1/P + T_{\infty}$ .

PROOF: We draw on the work of R. P. Brent [Bre74]. Suppose that  $s_i$  unit-time tasks are executed at step  $i=1,\ldots,T_{\infty}$  of a multithreaded computation using sufficiently many processors. Let  $T_1=\sum_{i=1}^{T_{\infty}}s_i$  be the total number of tasks to be executed. Using P processors, step i can be simulated in  $\lceil s_i/P \rceil$  steps. Since  $s_i=a_iP+b_i$  with  $a_i=\lfloor s_i/P \rfloor$  and  $b_i=(s_i-a_iP)\in\{0,1,\ldots,P-1\}$ , we obtain:

$$T_{P} = \sum_{i=1}^{T_{\infty}} \left\lceil \frac{s_{i}}{P} \right\rceil = \sum_{i=1}^{T_{\infty}} \left\lceil \frac{a_{i}P + b_{i}}{P} \right\rceil = \sum_{i=1}^{T_{\infty}} \left\lceil \frac{a_{i}P + P + b_{i} - P}{P} \right\rceil$$

$$= \sum_{i=1}^{T_{\infty}} \frac{a_{i}P + P}{P} + \sum_{i=1}^{T_{\infty}} \left\lceil \frac{b_{i} - P}{P} \right\rceil = \sum_{n=1}^{T_{\infty}} 1 + \frac{1}{P} \sum_{n=1}^{T_{\infty}} a_{i}P + \sum_{i=1}^{T_{\infty}} \left\lceil \frac{b_{i} - P}{P} \right\rceil$$

$$= T_{\infty} + \frac{1}{P} \sum_{i=1}^{T_{\infty}} a_{i}P + \sum_{i=1}^{T_{\infty}} \left\lceil \frac{b_{i} - P}{P} \right\rceil \leq T_{\infty} + \frac{1}{P} \sum_{i=1}^{T_{\infty}} s_{i} + \sum_{i=1}^{T_{\infty}} \left\lceil \frac{b_{i} - P}{P} \right\rceil.$$

From  $b_i \in \{0, 1, \dots, P-1\}$  it follows that  $\lceil (b_i - P)/P \rceil \leq 0$ . Using  $\sum_{i=1}^{T_{\infty}} s_i = T_1$ , we arrive at  $T_P = \sum_{i=1}^{T_{\infty}} \lceil s_i/P \rceil \leq T_1/P + T_{\infty}$ .

From Theorem 1, the following two corollaries can be deduced:

**Corollary 1:** The execution time  $T_P(\mathcal{X})$  for any P-processor greedy execution schedule  $\mathcal{X}$  of a multithreaded computation is optimal within a factor of 2.

PROOF: According to Theorem 1, for any P-processor greedy execution schedule  $\mathcal{X}$  of a multithreaded computation, the execution time  $T_P(\mathcal{X})$  is bounded above by  $T_P(\mathcal{X}) \leq T_1/P + T_{\infty}$ . Then inequality  $T_P(\mathcal{X}) \leq 2 \max\{T_1/P, T_{\infty}\}$  also holds.  $T_P(\mathcal{X}) \geq T_1/P$  and  $T_P(\mathcal{X}) \geq T_{\infty}$  imply  $T_P(\mathcal{X}) \geq \max\{T_1/P, T_{\infty}\}$ , so that finally  $\max\{T_1/P, T_{\infty}\} \leq T_P(\mathcal{X}) \leq 2 \max\{T_1/P, T_{\infty}\}$ .

**Corollary 2:** For any P-processor greedy execution schedule  $\mathcal{X}$  of a multithreaded computation, linear parallel speedup is achieved when the number P of processors is no more than the average available parallelism  $T_1/T_{\infty}$ .

PROOF: According to Corollary 1, for any P-processor greedy execution schedule  $\mathcal{X}$  of a multithreaded computation, the execution time  $T_P(\mathcal{X})$  is optimal within a factor of 2. Let the number P of processors be no more than the average available parallelism  $T_1/T_{\infty}$ , that is,  $P \leq T_1/T_{\infty}$  or equivalently  $T_{\infty} \leq T_1/P$ . Now consider the proof of Corollary 1 and insert  $T_{\infty} \leq T_1/P$  into  $\max\{T_1/P, T_{\infty}\} \leq T_P(\mathcal{X}) \leq 2\max\{T_1/P, T_{\infty}\}$ . Then  $T_1/P \leq T_P(\mathcal{X}) \leq 2T_1/P$ , that is,  $T_P(\mathcal{X}) = \Theta(T_1/P)$ , and linear parallel speedup is achieved.

#### 2.3.1. The Busy-Leaves Algorithm

In this subsection we consider the busy-leaves algorithm ('BL' for short) [BL99], the work stealing algorithm in Sec. 2.4 is based on—making its study be worthwhile in its own right.

#### Algorithm BL:

All living threads created before and during the execution of a strict multithreaded computation are maintained in a centralized thread pool that is uniformly available to all processors. Whenever a processor needs work it removes a ready thread, say, A from the pool, if there is any, and starts executing A's tasks until A either spawns, stalls, or dies.

- 1. If thread A spawns a child thread B, then A is returned to the thread pool, and its processor starts executing B.

- 2. If A stalls, then A is returned to the pool and its processor removes another ready thread from the pool and starts executing it.

- 3. If thread A dies, its processor checks whether A's parent thread, say, B has any living children. If not so, and if no other processor is executing B at that time step, then the processor takes B from the pool and starts executing it. Otherwise, the processor takes any ready thread from the pool.

If, for the sake of simplicity, we assume that processors do not contend with each other when accessing the pool, and if we further assume that threads can be added and removed from the pool in unit time, then the following theorem holds [BL99]:

**Theorem 2:** For any strict multithreaded computation with work  $T_1$ , DAG depth  $T_{\infty}$ , and activation depth  $S_1$ , and for any number P of processors, algorithm BL computes a P-processor execution schedule  $\mathcal{X}$  with its execution time  $T_P(\mathcal{X})$  satisfying  $T_P(\mathcal{X}) \leq T_1/P + T_{\infty}$ , and with space requirement  $S_P(\mathcal{X}) \leq S_1 P$ .

PROOF: The bound on the execution time of the schedule  $\mathcal{X}$  directly follows from the fact that algorithm BL computes a greedy execution schedule. Thus, Theorem 1 can be applied, and  $T_P(\mathcal{X}) \leq T_1/P + T_{\infty}$ . The space bound is a consequence of the fact that for strict computations, at any time during the execution, every leaf in the activation subtree has a processor working on it—busy-leaves property. By implication, the activation subtree has at most P leaves at any time during the execution. For every leaf, the space used by it and its ancestors is at most  $S_1$ . For the space requirement  $S_P(\mathcal{X})$  of the computation we then get  $S_P(\mathcal{X}) \leq S_1 P$ .

Theorem 2 states that algorithm BL can compute a strict multithreaded computation with linear expansion of space and linear parallel speedup, provided that the average available parallelism  $T_1/T_{\infty}$  is bounded below by the number P of processors.

## 2.4. A Randomized Work-Stealing Algorithm for Fully-Strict Multithreaded Computations

In this section we describe a randomized work stealing algorithm for fully-strict multithreaded computations ('WS' for short) with space requirements linear in the number P of processors and execution time linear in 1/P [BL99].

In algorithm WS the centralized thread pool used in algorithm BL is replaced by P ready thread dequeues distributed to the P processors of a parallel computer. Each processor is assigned exactly one dequeue containing threads that are ready for execution. Each dequeue has two ends, referred to as head and tail. For each dequeue only the processor it is assigned to (the owner) is allowed to add threads on the tail-end of the dequeue. The owner also takes threads from the dequeue's tail-end, using the dequeue in a LIFO manner. Threads that are migrated to other processors are taken (or stolen) from the head-end of the dequeue, making the dequeue appear as a FIFO for all other processors (called thieves in this context).

#### **Algorithm WS:**

Each processor maintains a dequeue of threads it is the owner of. A processor obtains work by removing a thread from the tail-end of its dequeue. If the dequeue contains any thread, say, A, it starts executing A until A either reenables a stalled thread, spawns, dies, or stalls. The processor then proceeds as follows:

1. If thread A re-enables a stalled thread, say, B (A's parent), the now-ready thread B is added to A's processor's (empty) dequeue—why the dequeue is

- empty at this time step is explained below—and the processor commences executing A. If thread A simultaneously re-enables a stalled thread, say, B and dies, its processor continues executing B and then A dies.

- 2. If A spawns a child thread B, its processor returns A on the tail-end of its dequeue and starts executing B.

- 3. If A stalls or dies, its processor checks its ready dequeue. If the dequeue is not empty the processor takes the thread on the tail-end and starts executing it. If the dequeue is empty, the processor becomes a thief and steals the thread on the head-end of the dequeue of another processor (called *victim* in this context) chosen uniformly at random—if the victim's dequeue is empty, the thief repeatedly chooses a new victim and tries again until either it successfully acquired a thread, or the computation has finished.

Remark: Subitem 1 states that for thread A re-enabling a stalled thread B, A's processor's dequeue is empty at the respective time step.

First, thread B is A's parent due to the structure of a fully-strict multithreaded computation, and due to the busy-leaves property (see algorithm BL), which according to subitem 2 also applies to algorithm WS. All dependency-edges from A thus go to its parent, which then might be re-enabled by A.

Second, since thread B is found be stalled, and A's processor uses its dequeue in a LIFO manner, B must have been stolen by another processor that has executed B until it stalled. Also due to the structure of a fully-strict multithreaded computation, re-enabling B after the stall can only be done by B's child thread, which here is A. According to subitem B is placed in the dequeue of another processor, as it was stolen, so that A's processor's dequeue must be empty at the respective time step.

**Theorem 3:** For any fully-strict multithreaded computation with activation depth  $S_1$ , and for any number P of processors, algorithm WS computes an execution schedule  $\mathcal{X}$  which uses at most  $S_P(\mathcal{X}) \leq S_1 P$  space.

PROOF: For the space bound we note that algorithm WS maintains the busy-leaves property. Thus,  $S_P(\mathcal{X}) \leq S_1 P$  for any P-processor execution schedule of a fully-strict multithreaded computation.

**Theorem 4:** For any fully-strict multithreaded computation with work  $T_1$ , DAG depth  $T_{\infty}$ , and for any number P of processors, algorithm WS computes a P-processor execution schedule  $\mathcal{X}$  with execution time  $T_P(\mathcal{X}) = \mathrm{O}(T_1/P + T_{\infty})$  including scheduling overhead.

PROOF IDEA: Since algorithm WS computes a greedy schedule  $\mathcal{X}$ , the proof of Theorem 4 is somehow similar to the proof of Theorem 2 except for the overhead explicitly addressed by Theorem 4—due to contention and communication. The latter point makes the proof of Theorem 4 a little more complicated. We therefore just give a proof idea based on [BL99], with some simplifications.

For the time bound we use an accounting argument: At each step of algorithm WS (execution schedule  $\mathcal{X}$ ), we collect P dollars, one from each processor. If the processor executes a task at the respective step, the dollar goes to a 'work bucket'. If the processor initiates a steal attempt, the dollar goes to a 'steal bucket', and if the processor waits for a queued steal, then the dollar goes into a 'wait bucket'—it is assumed that a third party serially queues the work stealing requests. The running time bound is derived by bounding the number of dollars in each bucket at the end of the execution, summing these values up, and then dividing by P. Since the multithreaded computation consists of  $T_1$  tasks, the work bucket contains  $T_1$ dollars at the end of the computation. An upper bound for the number of dollars in the steal bucket follows from there are  $O(PT_{\infty})$  stealing attempts over the course of the execution—along the critical path, which has length  $T_{\infty}$ , at each step O(P) stealing attempts may occur, so that the total number of stealing attempts is  $O(PT_{\infty})$ . In [BL99] it is shown that the expected number of dollars in the wait bucket is at most the number of dollars in the steal bucket. Adding up the dollars in the three buckets and dividing by the number P of processors gives  $T_P(\mathcal{X}) = (1/P) O(T_1 + PT_{\infty}) = O(T_1/P + T_{\infty}).$ Δ

#### Cilk

The work stealing algorithm as presented in this section is at the core of the Cilk programming language [BJK<sup>+</sup>95]—from 2006 onwards advanced by Intel. Additional keywords like cilk\_spawn and cilk\_sync, to name the maybe most important ones, extend the C/C++ programming language and allow the programmer to express potential parallelism in its application. The Cilk runtime system then decides about how the respective portions of the code (threads) are mapped onto the underlying computer hardware, using the here considered work stealing scheme for work distribution.

Just for illustration purposes, Listing 2.1 illustrates the usage of Cilk for the recursive computation of the n-th Fibonacci number (pseudo-code). If for the thread fib(n) the predicate n<2 evaluates to false, a new child thread fib(n-1) is spawned, and the respective processor commences with the execution of thread fib(n-1), possibly

<sup>&</sup>lt;sup>3</sup>In [BL99], the authors replace the DAG D describing the multithreaded computation by an augmented DAG D' which has DAG depth  $T'_{\infty} \leq 2T_{\infty}$ , where  $T_{\infty}$  is the DAG depth of D. The proof of Theorem 4 then is based on D'. However, our simplified argumentation stays the same.

#### 2. Dynamic Task Parallelism in Multithreaded Computations

```

function int fib(int n)

if n<0 then return (-1) |n|+1 fib(|n|)

if n==0 then return 0;

if n==1 then return 1;

int x=cilk_spawn fib(n-1);

int y=fib(n-2);

cilk_sync;

return x+y;</pre>

```

**Listing 2.1:** Computation of the n-th Fibonacci number using Cilk (pseudo-code)

concurrently to the execution of thread fib (n-2) by another processor. At cilk\_sync the two threads converge back to the execution of thread fib (n).

In Chapter 3 we mimic this model for the execution of multithreaded computations (with dependencies) on the GPU and on Intel's Xeon Phi.

## 3. Work Stealing on GPU and Intel Xeon Phi

In this chapter we are concerned with the implementation and the evaluation of the work stealing scheme described in Chapter 2 on a current Nvidia GPU, and on Intel's Xeon Phi—for comparison with a standard x86 multi-core CPU, we also implement the scheme on the CPU. Beforehand, we need to introduce the hardware used hereafter, as its functioning imposes some constraints and limits on the implementation of the work stealing scheme as well as on the applications which later should use the scheme.

#### 3.1. Nvidia Fermi GPU Architecture

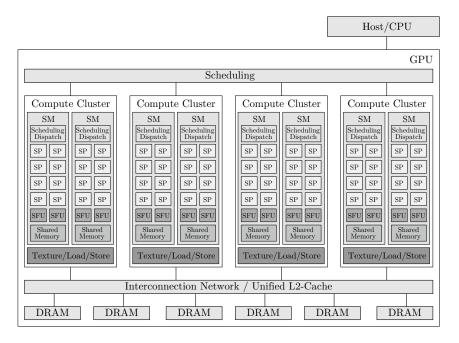

The Fermi architecture is Nvidia's second unified shader<sup>1</sup> GPU architecture [Nvi12, Nvi09]. Fermi-based GPUs consist of up 16 processors (referred to as SMs), each of which equipped with 32 unified shader processors (referred to as SPs) which execute GPU programs, or portions of a GPU program, in SIMD (Same-Instruction Multiple-Data) manner. Hence, there is a total of up to 512 physical execution units. On the level of its SMs, the GPU can be thought of as MIMD machine with 16 cores and a per-core vector unit of width 32, similar to multi-core CPUs with SSE/AVX. Each SM is further equipped with 4 special function units for transcendentals, up to 48kB on-chip low latency shared memory, 16 load/store units for memory transfers between the GPU and its main memory, and 2 scheduling/dispatch units. SMs are organized into compute clusters containing 2 SMs each. On top of these compute clusters is a thread scheduling unit that is responsible for the creation of threads and the distribution of these threads to the compute clusters and SMs, respectively. Also there is a unified 768kB L2 cache that is shared by all SMs, and which is between the SMs L1 cache and the up to 6GB main memory. The entire memory subsystem has support for Error-Correcting Code—ECC. Figure 3.1 schematically illustrates such a GPU device.

From the programmers point of view the GPU appears as a co-processor that can

<sup>&</sup>lt;sup>1</sup>A shader is an execution unit that executes shader programs written in an appropriate shader language. Today's GPUs are equipped with so-called unified shaders, which, by means of a unified instruction set, accumulate the functioning of the vertex-, pixel-, and geometry-shader along the graphs rendering pipeline in legacy GPUs.

Figure 3.1.: Illustration of an Nvidia GPU based on the Fermi unified shader architecture (schematically). The image is based on illustrations found in [Nvi12, Nvi09].

be assigned work to from within adapted CPU programs (running on the host system the GPU is connected to via PCI-Express) using, for instance, Nvidia's CUDA API.<sup>2</sup> The programmer is responsible for explicitly initiating data transfers between the host system and the GPU—the host and the GPU have different physical address spaces—, and the invocation of GPU programs, called *kernels*. Kernels execute asynchronously to the host program. For an introduction to GPU computing using CUDA, the interested reader is referred to [Nvi12].

For this thesis, the most interesting point is how the GPU schedulers create and distribute threads to SMs and SPs, respectively. At the core of thread scheduling on Nvidia GPUs is a hierarchy of threads, organized into an up to three-dimensional grid of thread blocks, and up to three-dimensional thread blocks the grid is made up of. Thread blocks contain up to 1024 threads, organized into groups of 32 threads each, called warps. On Fermi GPUs each SM is capable of scheduling up to 1536 threads, that is, 48 warps, where the actual number of warps that concurrently reside on an SM depends on the resource consumption of each thread within a warp.<sup>3</sup> These up to 48 warps are distributed over up to 8 thread blocks.

<sup>&</sup>lt;sup>2</sup>CUDA (Compute Unified Device Architecture) is an Nvidia proprietary programming model for Nvidia GPUs based on the unified shader architecture.

<sup>&</sup>lt;sup>3</sup>There are 32768 registers per SM, and up to 48kB shared memory. For a total of 1536 threads to reside on an SM at the same time, each thread is restricted to use no more than 21 registers and 32 bytes of shared memory. If threads use more resources, the number of concurrent threads per SM goes down.

For each kernel launch the programmer defines the number of threads that should execute the kernel using an appropriate grid-block geometry. The GPU thread schedulers then successively create threads in units of thread blocks, and distribute these blocks to the GPU's SMs—if assigned to an SM, a thread block is not migrated to another SM. On the SMs the schedulers partition the blocks into warps and execute these warps on the SM's 32 SPs in SIMD manner (wavefront execution). The execution of the up to 48 warps per SM is done by means of interleaved multithreading. Switching between warps that are ready for execution is done by almost zero overhead according to some scheduling policy, which unfortunately is not made public by Nvidia. The idea is to hide (memory access) latencies—that may occur during thread program executions—by switching between warps that are ready for execution. If all warps within a thread block have finished their execution, the block as a whole is finished. For each finished thread block, the vacated SM is assigned a new thread block, if there is any. It should be clear that, due to the fact that usually it is not possible to schedule all threads defined by the programmer at the same time, threads each need to execute independently of each other, except for intra-thread-block communication and cooperation. Otherwise the behavior of a GPU program may depend on the execution order of the thread blocks.

### 3.2. Intel Many Integrated Core (MIC) Architecture

With the Larrabee project, Intel started the development of a many-core computer architecture [HKB12] that with the Xeon Phi [Int12] was officially announced very recently. While the original Larrabee architecture was designed for both graphics processing and HPC (High-Performance Computing), the current Xeon Phi MIC architecture is placed in the HPC sector only.

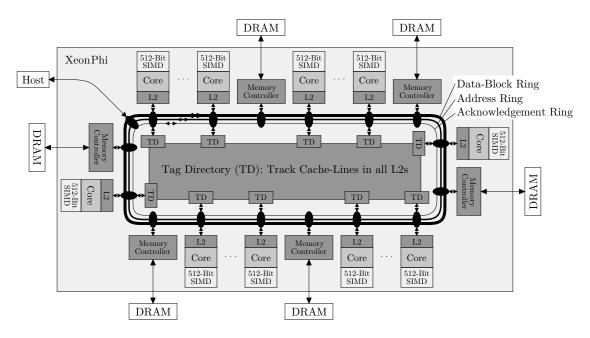

The Xeon Phi consists of an array of more than 50 Pentium-P5-based cores [Chr12], each of which augmented with 64-bit support, on-chip low latency L1 and coherent L2 cache, 32 512-bit vector registers, and 4-way interleaved multithreading. Using its vector unit, each core is capable of processing 16 32-bit words or 8 64-bit words per clock cycle. The cores, 16 memory controllers, and the PCI-Express client logic are connected by a bidirectional ring bus. Each direction of the ring consist of 5 independent rings: the data-block ring (64 bytes wide) for data transfers, 2 address rings which are used to send read/write commands and memory addresses, and 2 acknowledgment rings used to send flow control and coherence messages. Memory accesses first go through a tag directory (TD) which checks the L2 caches of all cores for the word requested, and forwards the request to the memory controllers only if the word is not present in any L2 cache.

Similar to the GPU, the Xeon Phi is connected to the host system via PCI-Express. Communication with the outside world is done using TCP/IP. The Xeon Phi runs a full

#### 3. Work Stealing on GPU and Intel Xeon Phi

**Figure 3.2.:** Illustration of the XeonPhi based on the Intel many integrated core (MIC) architecture (schematically). The image is based on illustrations found in [Chr12].

service Linux operating system which allows the programmer to use it as a (super-) computer in a computer. Within an application it can be used the same way as the GPU, but the Xeon Phi can also execute parallel applications natively without the need of a host program for kernel invocation. As it uses an x86 instruction set, the Xeon Phi is capable of executing (parallel) programs written for x86 CPUs, using OpenMP, pThreads, and Cilk, for instance. When writing programs/kernels for the 'Phi, almost all developer tools and programming languages known from x86 programming can be used. Applications that execute on the Xeon Phi are scheduled by its Linux operating system.

Table. 3.1 summarizes some properties of the hardware that is used in this thesis. All Information are either from the vendors' product database or from [Nvi09, Int12].

|                     | Tesla M2090            | Xeon E5-2670         | Xeon Phi (Test-sample) |

|---------------------|------------------------|----------------------|------------------------|

| Processor Count $P$ | 16 (up to 768 logical) | 8 (16 logical)       | 61 (244 logical)       |

| SIMD Width          | 32                     | 8                    | 16                     |

| Clock Frequency     | $1.3 \mathrm{GHz}$     | $2.6\mathrm{GHz}$    | $1.1 \mathrm{GHz}$     |

| Memory Size         | 6GB                    | -                    | 8GB                    |

| Memory Bandwidth    | $177 \mathrm{GB/s}$    | $51.2 \mathrm{GB/s}$ | $352 \mathrm{GB/s}$    |

| Power Consumption   | $<225~\mathrm{W}$      | < 115 W              | <300W                  |

Table 3.1.: Properties of Nvidia Tesla M2090, Intel Xeon E5-2670 and Intel Xeon Phi.

#### 3.3. Problem Description

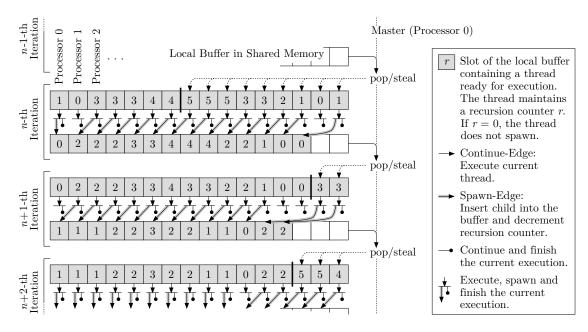

For both the GPU and the Xeon Phi the common approach for executing parallel applications is to partition the problem to be solved into subproblems that for the most part can be executed independently of each other. These subproblems then are expressed as thread programs which are mapped onto the processors according to some scheme. On the GPU dedicated scheduling units take on the mapping, whereas on the Xeon Phi (and the CPU) it is usually left to the programmer—iterating over the threads in chunks of the number of processors, for instance.

For multithreaded computations with dynamic thread creation, only few information about the work distribution at runtime are known beforehand. An obvious approach is to statically assign the portion of the threads that are created before the computation to the processors, and then at runtime to (re)distribute (newly created) threads to the processors in order to achieve an even load.

The GPU's scheduling units already implement some kind of load balancing on the level of the thread blocks. Since thread blocks are dynamically created at runtime, and then are assigned to available processors, even for applications with irregular workloads the scheduling should be balanced if the problem size in terms of thread blocks exceeds the processor count. As for a GPU program it is assumed that all work is known beforehand, dynamic thread creation cannot be handled by the GPU scheduler(s). Further it is assumed that on average threads behave identical so that all thread blocks created during the execution occupy the GPU's SMs for almost the same time. For SIMD applications this assumption applies. If threads dynamically create new threads, individual threads may require more time for their execution than others. The time the respective thread block resides on the SM then is possibly dominated by only a few warps in it. As the maximum number of thread blocks per SM is restricted to 8, a performance decrease might be observed when the thread scheduler(s) run out of warps they can switch between in the context of interleaved multithreading.

A viable solution to that issue is making thread blocks as small as possible, maybe containing just 1 or 2 warps. Unfortunately, the maximum number of concurrent threads per SM then is significantly below the maximum of 1536. Another approach is dynamic load balancing. For that to work a certain number of persistent threads is created so that hardware limitations are met (no more than  $16 \times 1536 = 24576$  persistent threads on Fermi GPUs). Persistent threads that belong to the same thread group are represented by a master thread. Each group maintains its own work pool that is filled up with the statically assigned threads at the beginning of the computation. Persistent threads each execute a super thread that keeps them alive until the computation is done. The master thread executes the work stealing scheme in order to acquire work for its thread group.

#### 3. Work Stealing on GPU and Intel Xeon Phi

With respect to the GPUs built-in load balancing strategy, performance improvements are to be expected, but the amount of the performance gain will strongly depend on the particular application. The overall performance of the application will also depend on the overhead introduced by the work stealing scheme.

On the Xeon Phi the static thread-processor assignment at the beginning of the computation may also result in some processors finish their threads significantly before other processors. The approach to handle these irregularities by means of dynamic load balancing is almost the same as for the GPU. The performance gain in so doing should be significantly above the one obtained on the GPU. The key difference to the GPU is that on the Xeon Phi there is no implicit load balancing by the hardware itself.

#### 3.4. Multithreaded Data Structures

In this section we describe the data structures used for work stealing—blocking and non-blocking dequeue, in particular. We also evaluate the performance of the data structures and estimate the overhead for accessing the data.

**Lock:** Our implementation of a lock uses the atomic compare-and-swap (CAS) hardware primitive (all operations between << and >> are atomic, meaning they are executed without interruption):

```

function bool atomicCAS(address, expectedValue, newValue)

bool success=false

<< if *address==expectedValue then *address=newValue, success=true >>

return success

```

Listing 3.1: Atomic compare-and-swap (pseudo-code). \*address is the value pointed to by address.

The atomicCAS() function compares the value pointed to by address with the value of expectedValue. If both are equal, the value pointed to by address is replaced by the value of newValue and the function returns true (success). Otherwise, it returns false (no success). On both Nvidia Fermi GPUs and x86-based processors an atomic compare-and-swap primitive is available. The lock itself is implemented as follows:

```

function void lock(address)

while atomicCAS(address,0,1) == false do

// spin around

function bool tryLock(address)

return atomicCAS(address,0,1)

function void unlock(address)

atomicEXCH(address,0) // Perform *address=0 without interruption

```

**Listing 3.2:** Lock based on atomic compare-and-swap (pseudo-code).

For the lock to work properly, the value pointed to by address (the value of the lock-variable) needs to be initialized to 0. The lock() function repeatedly compares the value of the lock-variable against 0, using the atomicCAS() primitive, until the lock has been acquired successfully—the value of the lock-variable then is 1. The tryLock() function tries to acquire the lock just once. The unlock() function sets the value of the lock-variable to 0—the lock is released.

#### 3.4.1. Blocking Dequeue

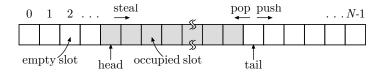

The blocking dequeue (double-ended queue) enforces mutual exclusive access to its data elements by means of a lock. It provides the following operations: push(), pop(), and steal(). We assume the dequeue be array-based with array size N. Then the status of the dequeue can be derived from its head-end index and its tail-end index (see Fig. 3.3). The head-end index points to the next element in the dequeue that can be stolen, whereas the tail-end index points to the next empty slot a new element can be pushed to. The dequeue is empty if its head-end index and its tail-end index are equal. We define the dequeue be full, if its tail-end index is equal to the array size N, and if its head-end index is lower than its tail-end index—for the sake of simplicity, we do not allow the head- and tail-end index to swap around, that is, the dequeue is not cyclic.

Figure 3.3.: Illustration of a dequeue for work stealing.

The steal() operation moves the head-end index one step towards the tail-end index, whereas the pop() operation moves the tail-end index one step towards the head-end index. Both of the two operations return one data element unless the dequeue is empty. If the dequeue is not full, the push() operation places a new data element into the dequeue at the position given by the tail-end index, and the tail-end index is moved one step towards the end of the array.

An implementation (in pseudo-code) of the blocking dequeue can be found in Listing 3.3. Appendix A.1 gives a concrete implementation for Nvidia GPUs. All functions start with acquiring a lock using either lock() or tryLock(). If the lock has been acquired, all operations until calling unlock() are done mutual exclusive. Thus, the dequeue is transferred from a consistent state to another one. We also list the function stealChunk(), which differs from the steal() function in that multiple elements can be stolen. By using stealChunk() instead of steal(), the effect of contention can be (partially) compensated.

```

struct dequeue<T> // T is a dummy for an actual data type

T dq[0..N-1]

int head, tail, lockVar=0 // The dequeue initially is unlocked

function bool push (T t)

bool success=false

lock(&lockVar) // &lockVar is the address of lockVar in main memory

if tail<N then</pre>

dq[tail]=t

tail=tail+1

success=true

unlock (&lockVar)

return success

function T pop()

T t=NULL

lock(&lockVar)

if head<tail then</pre>

tail=tail-1

t=dq[tail]

if tail==head then // Reset the dequeue. There is no ABA problem (see Sec. 3.4.2)

head=0

tail=0

unlock (&lockVar)

return t

function T steal()

function T[] stealChunk(int n)

T t=NULL

T[] t=NULL

if tryLock(&lockVar) == true then

if tryLock(&lockVar) == true then

if head<tail then</pre>

if head<tail then</pre>

t=dq[head]

n=n>(tail-head)?(tail-head):n

head=head+1

for i=0 to n-1 do

unlock(&lockVar)

t[i]=dq[head+i]

return t

head=head+n;

unlock (&lockVar)

return t

```

**Listing 3.3:** Blocking dequeue (pseudo-code). The notation c=predicate?a:b is a short form of if predicate==true then a else b.

The correctness of the implementation follows from only one processor can hold the lock at any time, and only this processor possibly changes the state of the dequeue. The implementation also guarantees deadlock-freedom as the lock is released eventually, with no side-effects affecting it.

#### 3.4.2. Non-Blocking Dequeue

The non-blocking dequeue differs from the blocking one in that mutual exclusion is realized by means of atomic hardware primitives instead of a lock. The implementation given in Listing 3.4 is based on [ABP98].

```

union dqIndex

// Both i16[] and i32 refer to the same location in memory:

int16 i16[2]

// i16[0] is the head-end index, and i16[1] addresses the ABA problem

int32 i32

struct dequeue<T> // T is a dummy for an actual data type

T dq[0..N-1]

dqIndex head=0

int tail=0

function bool push(T t)

if tail<N then</pre>

dq[tail]=t

tail=tail+1

return true

return false

function T pop()

Τt

dqIndex oldHead, newHead

int oldTail

if tail==0 then

return NULL

①tail=tail-1

t=dq[tail]

oldHead=head

if tail>oldHead.i16[0] then

return t

oldTail=tail

tail=0

newHead.i16[0]=0

// Reset the dequeue

② newHead.i16[1]=oldHead.i16[1]+1

// ABA problem!

if oldTail==oldHead.i16[0] then

if atomicCAS(&head.i32,oldHead.i32,newHead.i32) == true then

return t

(4) head=newHead

return NULL

function T steal()

T t

dqIndex oldHead, newHead

⑤ oldHead=head

6 if tail==oldHead.i16[0] then

return NULL

t=dq[oldHead.i16[0]]

newHead.i16[0]=oldHead.i16[0]+1

newHead.i16[1]=oldHead.i16[1]

(7) if atomicCAS(&head.i32,oldHead.i32,newHead.i32) == true then

return t

return NULL

```

**Listing 3.4:** Non-blocking dequeue (pseudo-code). The dequeue index head is of type dqIndex which is defined as a **union**. The reason for this is twofold: 1.) We need to address the ABA problem (see below), and 2.) on Nvidia GPUs the atomicCAS() primitive works on 32-bit and 64-bit words only.

#### 3. Work Stealing on GPU and Intel Xeon Phi

A concrete implementation for Nvidia GPUs is given in Appendix A.2. We extended the non-blocking dequeue implementation in Listing 3.4 so that it also allows to acquire sets of elements of the warp size (32 on the Tesla M2090). Further, the implementation is not restricted to contain at most 65535 elements, but it allows for  $2^{24} - 1$  elements.

#### Correctness

First, the value of the tail-end index tail is altered by the owner of the dequeue only. Since the owner either executes the push() function or the pop() function at any time, the push() function is not critical. It might occur that the value of tail is incremented by the owner concurrently to the execution of the steal() function by any of the thieves, but the worst thing that may happen is that the thieves evaluate the predicate tail==oldHead.il6[0] to true and return from steal(), even though the predicate becomes true at this point in time.

Second, as long as there is more than one element in the dequeue, the owner of the dequeue may execute the pop() function without using atomic primitives for the update of the dequeue state. The reason for that is the functioning of the atomic compare-andswap primitive. Suppose there are n thieves that concurrently try to steal the head-end element of the dequeue. Each of these thieves takes a 'snapshot' of the dequeue's headend index at the beginning of the steal() function (marker (5) in Listing 3.4). The thieves then remove the head-end element, determine the new state, and try to update the dequeue using the atomic compare-and-swap primitive (marker ?). The point is that for only one thief the head-end index of the dequeue has not changed in the meantime, and only for this thief the update is successful. After the atomic update of the dequeue, all other n-1 thieves will find the dequeue with the updated head-end index, which then does not match the snapshot taken at the beginning of the steal () function. As a consequence, if n thieves concurrently try to steal the head-end element of the dequeue, the head-end index of the dequeue is moved just one step towards the tail-end index of the dequeue. Thus, if there is more than one element in the dequeue, and n this ves and the owner concurrently execute steal() and pop(), respectively, the owner does not contend with the thieves for the tail-end element of the dequeue, and therefore the owner can update the dequeue state without using atomic primitives.

Third, if the dequeue contains only one element then the owner of the dequeue and the thieves contend for this element. Before removing the element from the dequeue, the owner decrements the value of tail (marker ①). Suppose there are  $n' \leq n$  thieves who evaluate the predicate ⑥ to true. These thieves return from steal() without success. The remaining n - n' thieves compete with the owner, and due to the atomic update of the dequeue state (marker ③ and ⑦) only one of them achieves success. Since the dequeue then is empty, it is reset by the owner, either at ③ or ④.

#### The ABA Problem (Non-Blocking Dequeue only)

Suppose that any of the thieves executing the steal() function takes its snapshot of the dequeue's head-end index and then is preempted. If this thief comes back for execution the dequeue's head-end index may has changed, but there is the possibility that the thief's snapshot still matches with the current the head-end index. If the respective thief then has success with updating the dequeue's head-end index, it returns an element which previously was already returned by either the owner or another thief (in the meantime the dequeue might be reset multiple times). This so-called ABA problem is addressed by the introduction of a counter which is incremented each time the dequeue is reset by the owner (marker ②)—if head is a 32-bit word, the counter is represented by the upper 16 bits (see the union definition of dqIndex in Listing 3.4).

#### 3.4.3. Performance Evaluation

In this subsection we evaluate the performance of the dequeue implementations on the GPU, the Xeon Phi, and a standard x86 multi-core CPU—see Tab. 3.1 for details on the hardware used. On the one hand we obtain information about the time it costs to access the dequeue's data elements, and on the other hand we can figure out what is the right choice for the respective compute device: blocking or non-blocking dequeue.

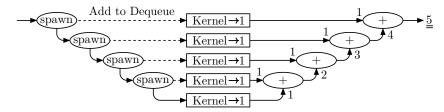

The way of proceeding is as follows: We use the GPU, the Xeon Phi, and the CPU in MIMD manner. For the GPU this means that thread groups (warps) each are represented and led by a master thread, and we just consider this master thread here (subsequently thread, for short). The benchmarking program creates n persistent threads that are executed by n processors. The number n will be varied over a meaningful range that is compatible with the number P of processors provided by the hardware. Each thread maintains a dequeue. Threads execute super threads in which they repeatedly acquire elements i) from their own dequeue only, and ii) from other thread's dequeues after they have finished their own dequeue. In setup iii) master threads also add new elements to their dequeue. That is, in setup i) they repeatedly execute the pop () operation, in setup ii) they execute the pop() and steal() operation, and in setup iii) all operations of the dequeue (pop(), steal(), push()) are executed. At the beginning of each iteration within the benchmark program, all dequeues are filled up with 32000 elements. In setup iii) every thread adds additional 32000 elements to its dequeue over the course of each iteration. When to execute push () and pop () is decided at runtime at random, with both operations be equiprobable.<sup>4</sup> An iteration completes when all elements from all dequeues have been acquired by the threads. The benchmarking program stops after a certain number of iterations.

<sup>&</sup>lt;sup>4</sup>Each thread has its own linear congruential random number generator for that purpose.

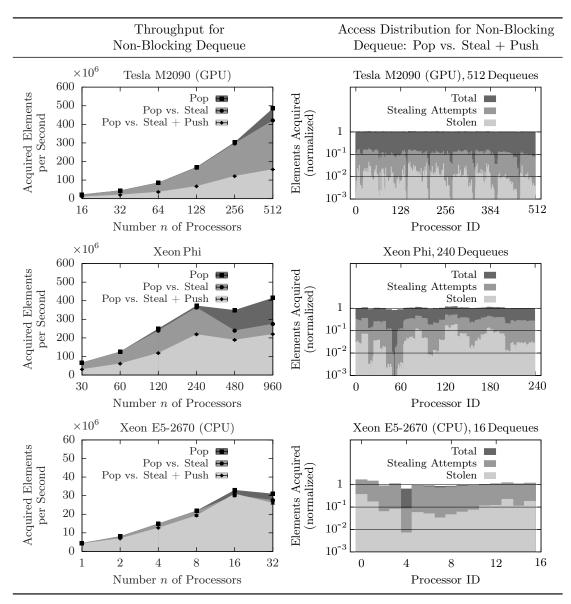

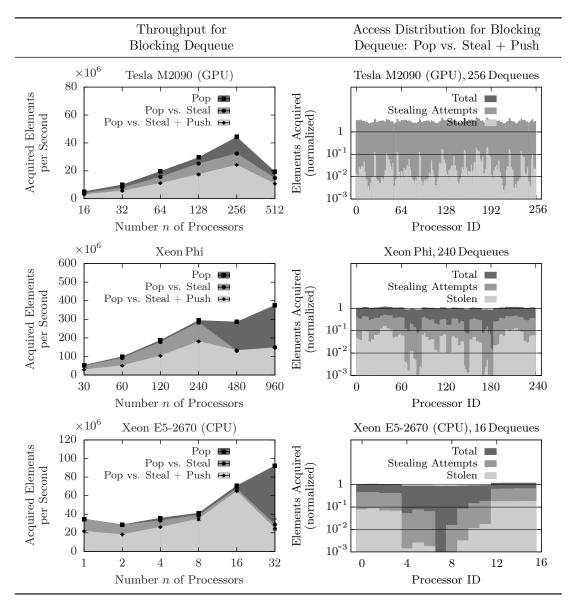

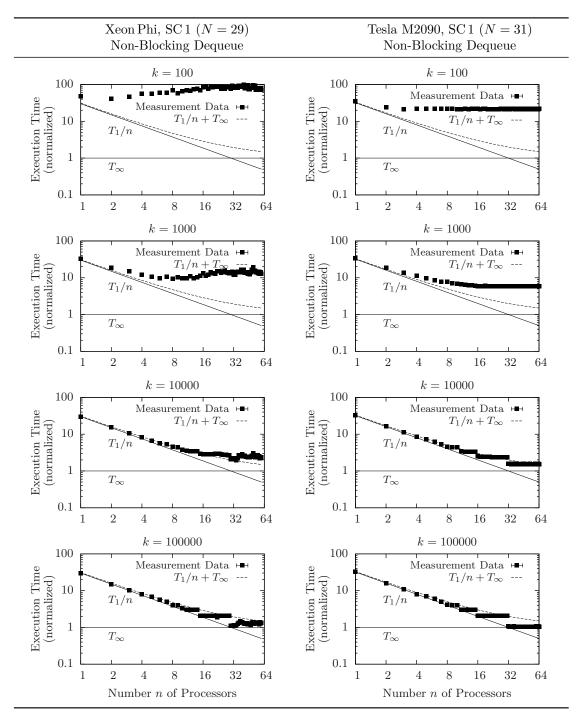

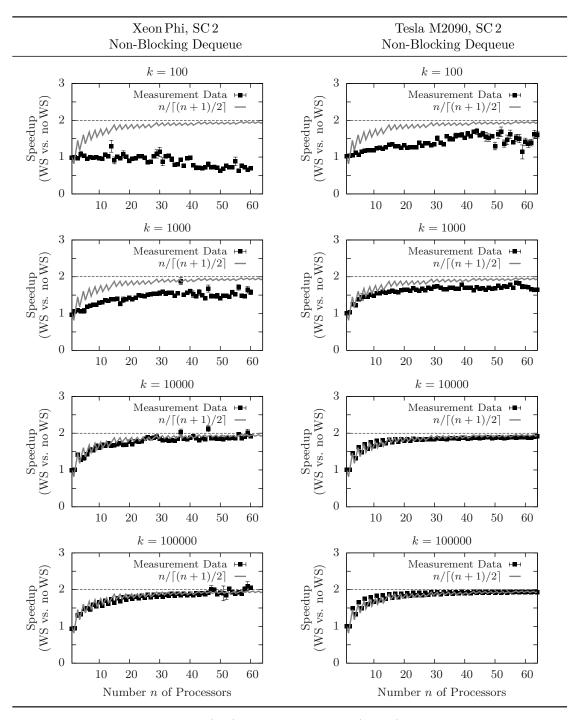

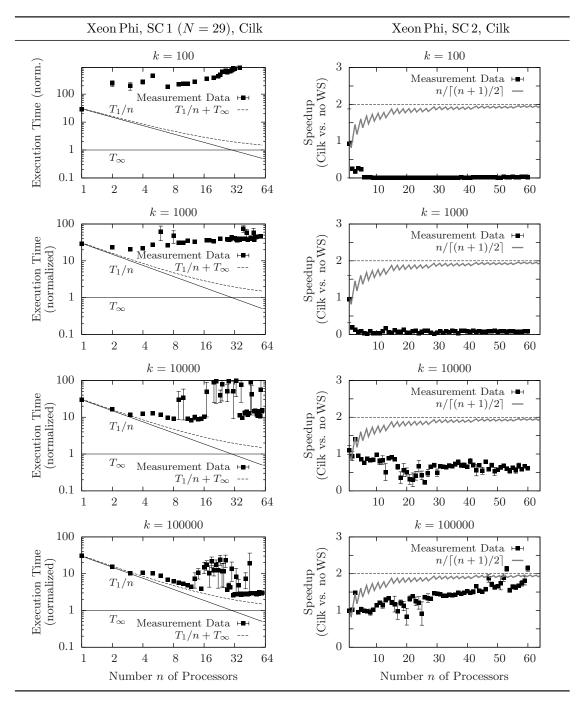

**Figure 3.4.:** Benchmarking results for the non-blocking dequeue implementation on GPU, Xeon Phi, and CPU. Values illustrated are averaged over 50 iterations within the benchmarking program. Values given in the right-hand side images are normalized to the expected number of elements per thread  $(50 \times 64000)$ .

Over the course of the benchmark we determine the overall throughput of the n dequeues, the number of acquired elements, the number of stealing attempts, and the number of actually stolen elements (the latter three, each per processor). Since the benchmarking program addresses the dequeue operations only, elements taken from any of the dequeues do not result in the execution of an associated thread. However, in a certain sense, the incrementation of the counters for the acquired/stolen elements and the stealing attempts can be understood as some kind of 'unit-time' tasks.

Figure 3.5.: Benchmarking results for the blocking dequeue implementation on GPU, Xeon Phi, and CPU. Values illustrated are averaged over 50 iterations within the benchmarking program. Values given in the right-hand side images are normalized to the expected number of elements per thread  $(50 \times 64000)$ .

We define the throughput of the n dequeues as the ratio of the overall acquired elements per iteration and the runtime of the respective iteration. The averaged throughput per dequeue then is the throughput divided by n. The inverse of this value gives an estimate of the averaged latency for accessing the dequeue's elements for each of the three setups. Figure 3.4 and 3.5 illustrate the benchmarking results averaged over 50 iterations for each setup and for each value of n. Error bars are included but almost always they are not visible—for almost all measurements taken the statistical error is below 1%.

#### 3. Work Stealing on GPU and Intel Xeon Phi

The right-hand side images illustrate the number of elements acquired by each processor throughout 50 iterations of the benchmarking program. The values are normalized to the expected number of elements per processor, which here is  $50 \times 64000$ . From these images it can be also seen that, due to the 'indeterminism' in the processors' push-and-pop behavior, some processors empty their dequeue before other processors—this models the execution of an actual computation with dynamic thread/task creation. These processors then become thieves and start stealing elements from the dequeues of other processors.

On the CPU, on average about 15% of the stealing attempts are successful, independently of whether the dequeue is blocking or non-blocking. On the Xeon Phi it is also about 15%. On the GPU only the non-blocking dequeue seems to work well. Here, on average about 10% of the stealing attempts are successful. Due to the stealing, thief threads acquire more elements than expected, whereas for threads from which elements are stolen the reverse is true. The normalized number of acquired elements thus varies around 1 for all threads.

An interesting point in this respect is that seemingly almost always the same threads are the ones elements are stolen from. On the GPU we assume that the internal scheduling of the threads (the warps) is not fair, so that some threads are preferred over others.

On the Xeon Phi this argument should not apply as here the hardware performs a strict per clock cycle round-robin switching between threads that run on the same physical execution unit. Rather, we assume that if there is heavy traffic on the ring bus, situations may occur where requests send over the ring bus stall. As memory is allocated at the beginning of the benchmark program, it might be possible that a stall affects always the same threads when trying to update their data structures concurrently to other threads. Maybe there are also NUMA (Non-Uniform Memory Access) effects. Also consider that the use of atomic primitives for synchronization methods results in memory bus locking and cache invalidation, both possibly affecting individual threads more than others.

The left-hand side images confirm non-blocking synchronization be more suitable for massively parallel computers than blocking synchronization. While on the GPU this statement is quiet obvious, on the XeonPhi both the non-blocking and the blocking dequeue implementation seem to work well. On the CPU the blocking dequeue is even superior to the non-blocking dequeue. However, for all three compute devices, the overall throughput of the dequeues scales almost linearly with number n of processors as long as n is below or equal to the device's processor count P (see Tab. 3.1).

<sup>&</sup>lt;sup>5</sup>During the execution of the benchmarks, we checked the correct functioning of the implementations of the dequeue: the number of elements put into the dequeues was exactly the number of elements that were concurrently removed from the dequeues by the processors.

When comparing the throughput for the three different setups, the highest throughput is obtained if there is no stealing and no pushing (setup i)). In setup ii), where a certain number of pop() operations is executed concurrently to steal() operations, the throughput decreases. In the case of the non-blocking dequeue, the reason for that is the use of atomic primitives in the steal() operation—atomic operations enforce memory bus locking while the operation is performed, and cache invalidation afterwards. In the case of the blocking dequeue, steal() operations make the owner of the respective dequeue contend with thief threads for the dequeue's lock. In both cases the throughput goes down. In setup iii) the decrease in the throughput is due to half of the pop() and steal() operations require the push() operation has been executed previously—elements taken from the dequeues must have been added to them previously. The effective costs of a pop() operation and a steal() operation, respectively, then increase by the costs of a push() operation. Again the throughput goes down.

Table 3.2 summarizes some characteristic (averaged) per-dequeue values extracted

| Characteristics for Dequeue: |                                 |           | Non-Blocking | Blocking         |

|------------------------------|---------------------------------|-----------|--------------|------------------|

| Setup i)                     | Throughput in                   | GPU:      | 0.95         | $0.17^{\dagger}$ |

|                              | 10 <sup>6</sup> Elements/Second | Xeon Phi: | 1.55         | 1.22             |

|                              |                                 | CPU:      | 2.06         | 4.42             |

|                              | Latency in                      | GPU:      | 1.05         | $5.88^{\dagger}$ |