# Ermittlung von Programmlaufzeiten anhand von Speicherzugriffen, Microbenchmarks und Simulation von Speicherhierarchien

Florian Schintke

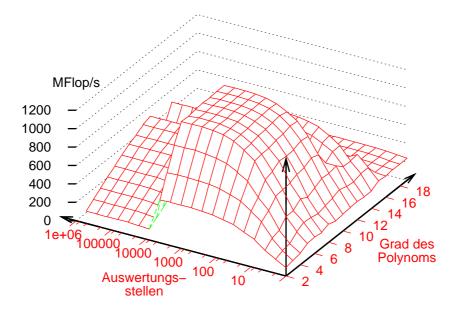

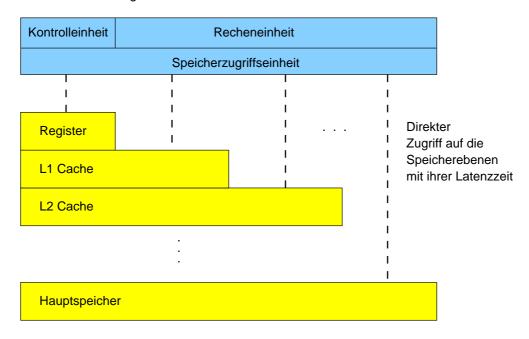

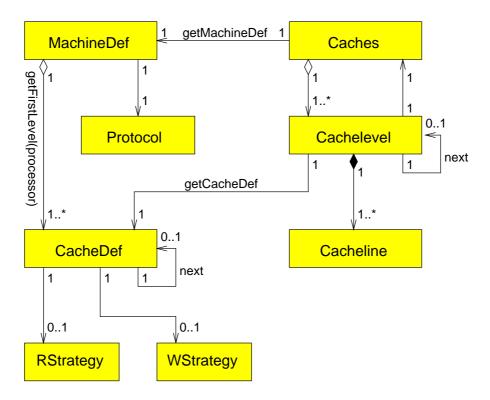

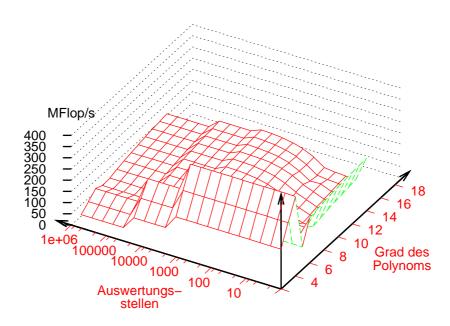

Das Titelbild ist größtenteils aus Grafiken, die für diese Arbeit entstanden sind, zusammengesetzt. Die Uhr stellt die Ermittlung von Programmlaufzeiten dar und das Drahtgittermodell ist die Visualisierung der Ergebnisse des Horner-Schema-Benchmarks (siehe Abbildung 4.5) von Seite 23 und repräsentiert die Microbenchmarks. Als dritte Komponente ist symbolisch eine Speicherhierarchie (siehe Abbildung 2.1 auf Seite 4) dargestellt. Den Hintergrund bildet ein Fragment des Quelltextes des im Rahmen dieser Arbeit entstandenen Simulators für Speicherhierarchien.

## Diplomarbeit

# Ermittlung von Programmlaufzeiten anhand von Speicherzugriffen, Microbenchmarks und Simulation von Speicherhierarchien

vorgelegt von

Florian Schintke

am Fachbereich Informatik der Technischen Universität Berlin

betreut durch

Prof. Dr. Bernd Mahr Prof. Dr. Alexander Reinefeld

August 2000

#### Erklärung:

Hiermit versichere ich, die vorliegende Arbeit selbständig und nur unter Verwendung der angegebenen Hilfsmittel angefertigt zu haben.

| Berlin, den 17 | . August 2000 |  |

|----------------|---------------|--|

|                |               |  |

|                |               |  |

| Unterschrift   |               |  |

## Danksagung:

Mein Dank gilt Prof. Dr. Alexander Reinefeld, Leiter des Bereichs Computer Science am Konrad-Zuse-Zentrum für Informationstechnik Berlin und Prof. Dr. Bernd Mahr vom Institut für Formale Modelle und Logik an der TU Berlin. Schließlich danke ich meinem Betreuer Dr. Jens Simon vom Konrad-Zuse-Zentrum für Informationstechnik Berlin für seine Unterstützung, sowie meinen Eltern, die mich während meines gesamten Studiums unterstützt haben.

Außerdem danke ich Donald E. Knuth und Leslie Lamport für die Entwicklung von TEX und Lamport für die Arbeit in dieser Form präsentiert werden kann.

#### Kurzfassung

Kostenmodelle dienen der Ermittlung von Programmlaufzeiten, zum Vergleich der Effizienz von Algorithmen und zur Analyse des Verhaltens von Speicherhierarchien. Ein neuartiges Kostenmodell ist das Latency-of-Data-Access (LDA) Modell, das mehrere hierarchische Speicherebenen mit unterschiedlichen Latenzzeiten berücksichtigt. In dieser Diplomarbeit wird ein Simulator für Speicherhierarchien präsentiert, der die Berechnung von Programmausführungszeiten nach dem LDA-Modell erlaubt. Mit Hilfe des Simulators wird die These geprüft, daß mit diesem Modell die Ausführungszeit eines Programms adäquat abgeschätzt werden kann. Mit dem Simulator ist es erstmals praktikabel möglich, Programmausführungszeiten nach dem LDA-Modell zu bestimmen. Der Simulator kann für Systeme mit unterschiedlichen Speicherarchitekturen konfiguriert werden und unterstützt Mehrprozessorsysteme mit gemeinsamem Speicher (SMP-Systeme) mit verschiedenen Kohärenzprotokollen. Der Simulator kann mit den Ergebnissen von Microbenchmarks konfiguriert werden, die die Architekturparameter einer Speicherhierarchie messen. Die Ergebnisse bestätigen die These nicht nur für Einzelprozessorsysteme, sondern auch für SMP-Systeme, wo gleichzeitig interagierende Prozessoren gegenseitig ihre Zugriffssequenz auf Zwischenspeicher beeinflussen. Zusätzlich wurde eine neue Einsatzmöglichkeit des LDA-Modells entwickelt, um die Ausführungszeit von Programmteilen zu bestimmen. Einzelne Zugriffskosten können einem mehrerer parallel laufender Modelle zugeordnet werden. Dadurch können Kosten, die Zugriffe auf einzelne Speicherbereiche verursachen, separat bestimmt werden. Diese Profiling-Technik erlaubt Optimierungen an Datenstrukturen und Speicherzugriffsmustern durch präzise und gezielte Informationsproduktion.

#### **Abstract**

Cost models are used to determine the execution time of programs, to compare the efficiency of algorithms, and to analyse the behaviour of memory hierarchies. The Latency-of-Data-Access (LDA) model that takes into account multiple hierarchical memory levels with different latencies, is a newly proposed, innovative cost model. In this diploma-thesis, a simulator for memory hierarchies is presented that allows the calculation of execution times using the LDA model. The simulator is used to prove the claim that the execution time of a program can be accurately estimated with the LDA model. With the simulator, it is for the first time possible to determine the execution time of programs with this model in a practical way. The simulator can be configured for systems with various cache architectures and supports shared memory (SMP) multiprocessor systems with different cache coherence protocols. The simulator can be configured with the results from Microbenchmarks which measure the architectural properties of a memory hierarchy.

The results confirm the claim not only for single processor systems, but also for SMP systems, where concurrently interacting processors influence each others cache access sequence. Additionally, a new field of usage of the LDA model was developed to determine execution times of program parts. Single access costs can be assigned to one of several parallel running models. As an example the costs of accesses to different memory areas can be split and determined separately. This profiling technique allows to optimise data structures and memory access patterns of sequential and parallel SMP programs by precise production of information.

## Inhaltsverzeichnis

| Einleit | ung                                                                   | 1  |

|---------|-----------------------------------------------------------------------|----|

| 1.1     | Thema dieser Arbeit                                                   | 1  |

| 1.2     | Struktur dieser Arbeit                                                | 2  |

| Speich  | erhierarchien von Einzelprozessorsystemen                             | 3  |

| 2.1     | Zweck von Speicherhierarchien                                         | 3  |

| 2.2     | Aufbau eines Caches                                                   | 5  |

| 2.3     | Neuartige Strategien für die Nutzung von Zwischenspeichern            | 8  |

| Speich  | erhierarchien von symmetrischen Multiprozessorsystemen                | 9  |

| 3.1     | Symmetrische Multiprozessorsysteme (SMP-Systeme)                      | 9  |

| 3.2     | Zweck und Arten von Kohärenzprotokollen                               | 10 |

| 3.3     | Kohärenzprotokoll MSI                                                 | 10 |

| 3.4     | Kohärenzprotokoll MESI                                                | 11 |

| Microb  | enchmarks                                                             | 14 |

| 4.1     | Zweck von Microbenchmarks                                             | 14 |

| 4.2     | Genauigkeit der Zeitmessung                                           | 15 |

| 4.3     | Bestimmung des Prozessortaktes                                        | 15 |

| 4.4     | Latenzzeiten von Speicherebenen                                       | 16 |

| 4.5     | Speicherbandbreiten                                                   | 20 |

| 4.6     | Speicheroperationen im Verhältnis zu Rechenoperationen: Horner-Schema | 21 |

| Simula  | tion von Speicherhierarchien                                          | 26 |

| 5.1     | Zweck und Arten von Simulatoren für Speicherhierarchien               | 26 |

| 5.2     | Instrumentierung von Programmen                                       | 27 |

| 5.3     | Funktionsweise von Simulatoren für Speicherhierarchien                | 28 |

| 5.4     | Beispiele für Simulatoren von Speicherhierarchien                     | 28 |

| Auf de  | m LDA-Modell basierender Simulator                                    | 31 |

| 6.1     | Das RAM-Modell                                                        | 31 |

| 6.2     | Das Latency-of-Data-Access Modell (LDA-Modell)                        | 32 |

| 6.3     | Das LDA-Modell für SMP-Systeme                                        | 33 |

| 6.4     | LDA-Modell basierter Simulator für Speicherhierarchien                | 33 |

| 6.5     | Konfigurationsmöglichkeiten                                           | 34 |

| 6.6     | Schnittstelle und Implementation des Simulators                       | 35 |

| 6.7     | Checkpointing                                                         | 35 |

| 6.8     | Getrennte Teilkostenermittlung                                        | 38 |

| 6.9     | Instrumentierung                                                      | 38 |

iv Inhaltsverzeichnis

| Ermittlu | ung von Programmlaufzeiten mit dem Simulator               | 40 |

|----------|------------------------------------------------------------|----|

| 7.1      | Simulation der Messung von Latenzzeiten                    | 40 |

| 7.2      | Simulation des Horner-Schema-Benchmarks                    | 41 |

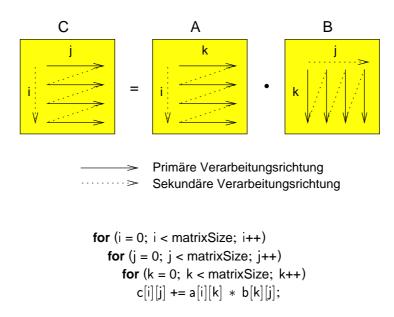

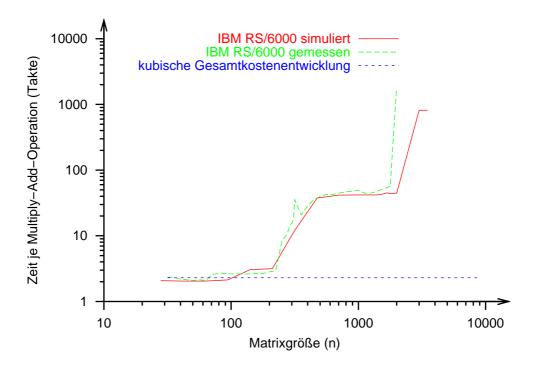

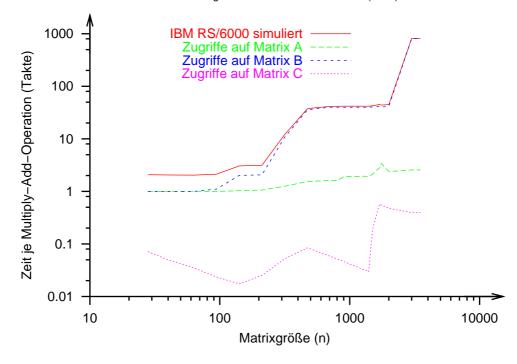

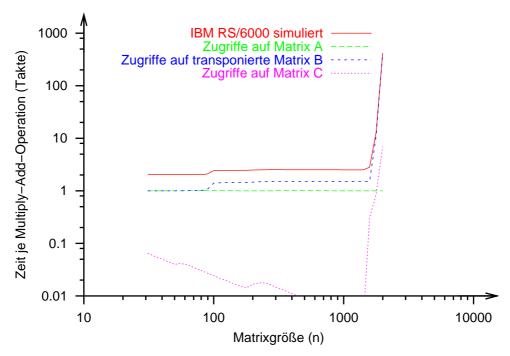

| 7.3      | Sequentielle Matrix-Matrix-Multiplikation                  | 42 |

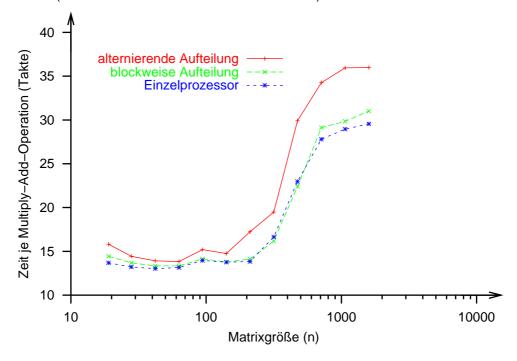

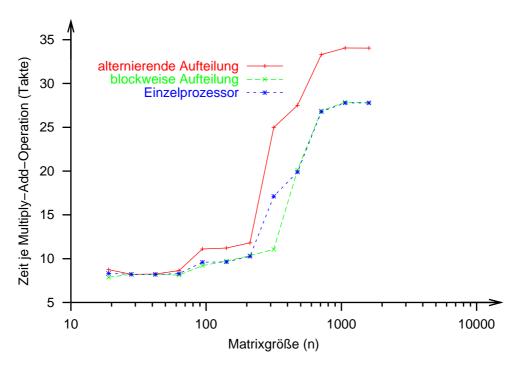

| 7.4      | Messung parallelisierter Matrix-Matrix-Multiplikationen    | 46 |

| 7.5      | Simulation parallelisierter Matrix-Matrix-Multiplikationen | 47 |

| Zusamı   | menfassung                                                 | 49 |

| 8.1      | Ergebnisse                                                 | 49 |

| 8.2      | Realisierung der Untersuchung                              | 50 |

| 8.3      | Ausblick                                                   | 50 |

| Literatu | ırverzeichnis                                              | 51 |

| Index    |                                                            | 55 |

# **Einleitung**

La perfection est atteinte non quand il ne reste rien à ajouter, mais quand il ne reste rien à enlever.

- ANTOINE-MARIE-ROGER DE SAINT EXUPÉRY

#### 1.1 Thema dieser Arbeit

Die Ausführungszeit von Programmen ist in der Informatik eines der grundlegenden Kostenmaße für Berechnungen. Durch sie werden verschiedene Algorithmen, verschiedene Speicherhierarchien und verschiedene Prozessoren im Bezug auf ihre Effizienz miteinander verglichen. Mit Hilfe von Modellen oder Kalkülen wird versucht, die Ausführungszeit von Programmen zu beschreiben und abzuschätzen. Am bekanntesten ist das Modell der "Random Access Machine" (RAM-Modell) des von Neumann Rechners, beziehungsweise die "Parallel Random Access Machine" (PRAM-Modell).

Ein neuartiges Modell, das unterschiedliche Zugriffszeiten auf Speicherzellen in einer Speicherhierarchie berücksichtigt, ist das "Latency-of-Data-Access Modell" (LDA-Modell). Für eine Analyse der Ausführungszeit nach dem LDA-Modell muß die Anzahl der Zugriffe auf die verschiedenen Ebenen einer Speicherhierarchie bekannt sein. Mit einem im Rahmen dieser Arbeit entwickelten Simulator für Speicherhierarchien ist eine Gewinnung dieser Daten möglich.

Der entwickelte Simulator für Speicherhierarchien ist flexibel für die Speicherhierarchien von Einzelprozessorsystemen und symmetrischen Mehrprozessorsystemen (SMP-Systemen) konfigurierbar. Er unterstützt beliebig viele hierarchisch angeordnete Speicherebenen, verschiedene Ersetzungs- und Schreibstrategien und verschiedene Kohärenzprotokolle für SMP-Systeme. Für seine Konfiguration müssen architekturspezifische Daten der Speicherhierarchie, die simuliert werden soll, bekannt sein. Diese Daten können technischen Dokumentationen von Computern entnommen oder durch Microbenchmarks ermittelt werden. Microbenchmarks können auch zur Kontrolle der technischen Daten oder zur Ermittlung der aktuellen Einstellungen (bei Konfigurierbarkeit der Hardware) genutzt werden.

Es wird untersucht, ob mit den drei Hilfsmitteln Microbenchmarks, Informationen über Speicherzugriffe und Simulation von Speicherhierarchien Ausführungszeiten von Programmen unter Verwendung des LDA-Modells akkurat bestimmt werden können. Mit dem im Rahmen dieser Arbeit entwickelten Simulator für Speicherhierarchien ist es zusätzlich möglich, nicht nur die Gesamtkosten eines Programms oder eines Programmabschnitts, sondern auch die Kosten von Speicherzugriffen auf einzelne Speicherbereiche zu ermitteln, wodurch Informationen für mögliche Optimierungen der Nutzung von Zwischenspeichern durch Änderungen der Datenstrukturen des simulierten Programms zur Verfügung gestellt werden.

2 Kapitel 1: Einleitung

#### 1.2 Struktur dieser Arbeit

Zuerst werden in Kapitel 2 die Konzepte von Speicherhierarchien dargestellt. Dabei wird erklärt, weshalb man Speicherhierarchien einsetzt, erläutert, wie Speicherhierarchien aufgebaut sind und wie einzelne Speicherebenen verwaltet und organisiert werden. Begriffe wie Blockgröße, Assoziativität, Ersetzungs- und Schreibstrategie werden eingeführt.

Kapitel 3 beschreibt zusätzliche Konzepte von Speicherhierarchien bei SMP-Systemen. Hierbei wird erläutert, weswegen Kohärenzprotokolle für die Speicherhierarchien dieser Systeme notwendig sind, und zwei Kohärenzprotokolle (MSI und MESI) werden vorgestellt.

In Kapitel 4 wird zunächst der Zweck von Microbenchmarks erläutert und es werden nützliche Einsatzmöglichkeiten diskutiert. Dann werden Microbenchmarks, die zur Ermittlung von architekturellen Daten einer Speicherhierarchie dienen, vorgestellt und untersucht. Die Ergebnisse der Microbenchmarks werden später teilweise dazu genutzt, einen flexiblen Simulator für Speicherhierarchien zu konfigurieren. Außerdem wird gezeigt, daß Microbenchmarks, die in höheren Programmiersprachen implementiert sind, Vorund Nachteile haben, da die genutzten Compiler die Ergebnisse von Microbenchmarks stark beeinflussen können (siehe Abschnitt 4.6).

Verschiedene Arten von Simulatoren von Speicherhierarchien, zwischen denen man anhand ihrer Funktionsweise unterscheidet, sowie das Konzept der Instrumentierung und verschiedene Methoden der Instrumentierung werden in Kapitel 5 vorgestellt. Zusätzlich werden einige Simulatoren für Speicherhierarchien beschrieben.

In Kapitel 6 wird der entwickelte Simulator für Speicherhierarchien vorgestellt, nachdem das LDA-Modell, das dem Simulator zugrunde liegt, beschrieben wurde. Die Konfigurationsmöglichkeiten, die Schnittstellen und eine beispielhafte Instrumentierung eines Programms gehören unter anderem zu der Beschreibung des Simulators.

Daß mit Hilfe des LDA-Modells in Kombination mit einer Analyse der Speicherzugriffe, die mit einem über Ergebnisse von Microbenchmarks konfigurierten Simulator für Speicherhierarchien möglich wird, eine akkurate Bestimmung von Programmlaufzeiten möglich ist, wird anhand von Beispielen im Kapitel 7 gezeigt. Die auf realen Systemen gemessenen Programmlaufzeiten werden dafür mit simulierten Programmlaufzeiten verglichen. In Kapitel 7 wird auch die Möglichkeit des Simulators genutzt, die Kosten, die Zugriffe auf verschiedene Speicherbereiche verursachen, getrennt zu betrachten. Die Kosten der Speicherzugriffe einzelner Matrizen bei einer Matrix-Matrix-Multiplikation werden beobachtet und dann, durch Optimierung des Speicherformats einer Matrix, die Gesamtkosten auch für größere Matrizen reduziert.

Es bestehen im Prinzip zwei Haupteinsatzgebiete der in dieser Arbeit vorgestellten Methode zur Ermittlung von Programmlaufzeiten: Einerseits kann die Methode zur Analyse und Optimierung von Programmen für eine Speicherhierarchie oder zur Wahl eines geeigneten Algorithmus dienen, andererseits können, bei der Entwicklung einer neuen Speicherhierarchie, Programmlaufzeiten ermittelt werden, ohne Prozessor oder Speicherhierarchie in Hardware implementieren zu müssen. Eine Optimierung der Speicherhierarchie ist auf diese Art möglich, indem die Leistungen verschiedener Konfigurationen der Speicherhierarchie analysiert und miteinander verglichen werden.

# Speicherhierarchien von Einzelprozessorsystemen

A memory hierarchy is a natural reaction to locality and technology.

– JOHN L. HENNESSY und DAVID A. PATTERSON, Computer Architecture – A Quantitative Approach

Speicherhierarchien werden benutzt, um die durchschnittliche Zeit, die für einen Speicherzugriff in einem Computer benötigt wird, zu reduzieren und so die Ausführungszeit von Programmen zu verkürzen. Speicherhierarchien umfassen mehrere Ebenen von Zwischenspeichern verschiedener Größe und Geschwindigkeit, die sich gegenseitig nutzen. Für diese Zwischenspeicher existieren verschiedene Realisierungsmöglichkeiten, die sich in Nutzbarkeit, dem Verwaltungsaufwand, der Geschwindigkeit und der benötigten Schaltung unterscheiden. Blockgröße, Zeilenanzahl, Assoziativität und Ersetzungs- und Schreibstrategie sind hierbei die zentralen Parameter, die das Verhalten eines Zwischenspeichers beeinflussen.

#### 2.1 Zweck von Speicherhierarchien

Eine Speicherhierarchie besteht aus Speicherebenen, die verschiedene Geschwindigkeiten und Größen haben. In einer Speicherhierarchie werden von kleineren schnelleren Speichern, die im Bezug auf Kommunikationswege näher am Prozessor liegen, größere langsamere Speicher genutzt, die weiter entfernt vom Prozessor liegen. Eine Speicherhierarchie wird von einem oder mehreren Prozessoren genutzt, um sowohl das auszuführende Programm als auch seine Daten zu lesen und zu speichern.

Eine Speicherhierarchie soll die Ausführungszeiten von Programmen gegenüber einer Ausführung ohne Speicherhierarchie (nur Hauptspeicher) verkürzen. In vielen Programmen gibt es Bereiche, die in einem kleinen Abschnitt des Programms wiederholt auf die gleichen Speicherzellen und/oder auf benachbarte Speicherzellen zugreifen, also eine Lokalität der Daten aufweisen. Man spricht von räumlicher Lokalität (spatial locality), wenn nahe beieinanderliegender Adressen benötigt werden, und von zeitlicher oder temporaler Lokalität (temporal locality), wenn auf eine Adresse in einem Zeitintervall häufig zugegriffen wird. Ein wiederholtes Ausführen desselben, kleinen Programmteils führt zu einer Lokalität des Programmcodes. Der Ablauf solcher Programme kann beschleunigt werden, indem die in einem Teilabschnitt des Programms benötigten Daten in einem kleineren, aber dafür schnelleren Speicher (Cache) zwischengespeichert werden, weil sich dadurch die

Lokalität

durchschnittliche Wartezeit (auch Latenzzeit genannt) des Prozessors auf angeforderte Daten reduzieren läßt. Wartezeiten können in einigen Fällen mit Rechenoperationen, die nur Daten benötigen, die bereits in Registern des Prozessors gespeichert sind, überbrückt werden. Je länger der Prozessor warten muß, ohne die Wartezeit mit Rechenoperationen überbrücken zu können, desto schlechter ist er ausgelastet. Um einen Prozessor gut auszulasten, sind also Speicher nötig, die schnell genug sind, dem Prozessor die benötigten Daten zu liefern. Hennessy und Patterson (1996) haben statistische Analysen über die Lokalität von Daten in Programmen durchgeführt und beschrieben.

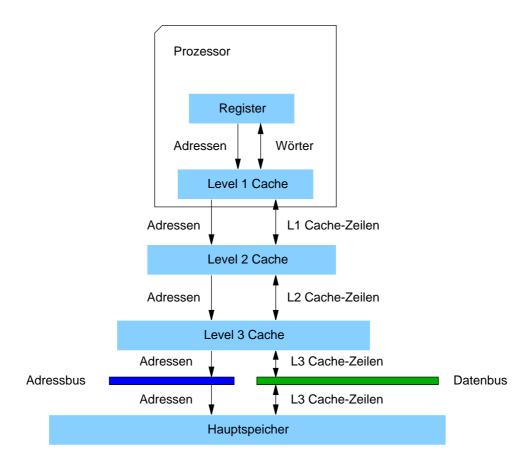

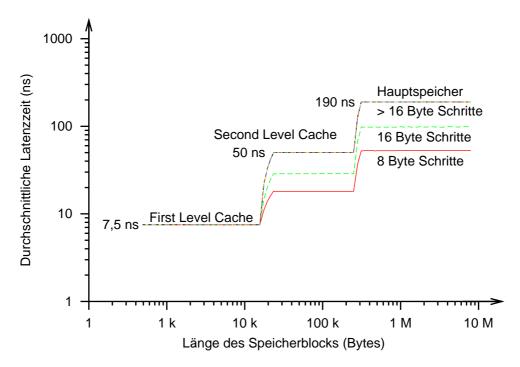

Abbildung 2.1: Je weiter oben in einer Speicherhierarchie eine Speicherebene angesiedelt ist, desto schneller sind Datenzugriffe, und desto kleiner ist ihre Kapazität.

Abbildung 2.1 zeigt den grundsätzlichen Aufbau einer Speicherhierarchie. Die kleinste Speicherebene, die nicht die Register des Prozessors sind, nennt man "Level 1 Cache" oder "First Level Cache" (im folgenden nur noch L1 Cache). Die weiteren Speicherebenen werden aufsteigend durchnumeriert, bis der Hauptspeicher erreicht ist (im folgenden als L2, L3, ..., Ln–1, Ln, Ln+1 Cache und so weiter bezeichnet). Üblich sind zwei bis drei Zwischenspeicher. Eine konkrete Speicherhierarchie nennt man auch Speicherarchitektur oder, wenn aus dem Zusammenhang klar ist, daß es um eine Speicherarchitektur geht, auch einfach nur Architektur. Die Caches sind miteinander verbunden und tauschen Adressen und Daten über ihre Verbindungen aus.

2.2 Aufbau eines Caches

Fordert ein Prozessor Daten an, durchläuft diese Anfrage nacheinander die Zwischenspeicher, bis einer die Anfrage beantworten kann (die Daten gerade gespeichert hat). Sind die Daten nicht zwischengespeichert, beantwortet der Hauptspeicher die Anfrage.

Die Lösung kleinere Zwischenspeicher einzusetzen, um schnelle Speicherhierarchien zu realisieren und nicht einen großen, schnellen Speicher zu benutzen hat zwei Hauptgründe: Zum einen sind Kostengründe und unterschiedliche Technologien, zum anderen aber auch physikalische Gesetze dafür ausschlaggebend. Zuerst werden im folgenden die physikalischen Gründe betrachtet.

Physikalisch bedingt werden Speicher im Durchschnitt immer langsamer, je größer sie werden. Je mehr Daten ein Speicher speichern kann, desto größer ist auch seine räumliche Ausdehnung gegenüber einem kleineren Speicher unter Verwendung der gleichen Technologie. Daten, die ein Prozessor vom Speicher anfordert, müssen zur Schnittstelle des Speichers transportiert werden, um zum Prozessor oder auf den Datenbus zu gelangen. Da Information maximal mit Lichtgeschwindigkeit transportiert werden kann, ist bei räumlich ausgedehnteren Speichern die durchschnittliche Zeit bis die Daten an der Schnittstelle anliegen höher als bei kleineren Speichern, weil die Information im Durchschnitt längere Wege zurücklegen muß. Deshalb sind größere Speicher langsamer.

Große Speicher sind langsamer

5

Geschwindigkeitsunterschiede zwischen verschiedenen Speichern einer Speicherhierarchie kommen jedoch nicht nur durch geringere Entfernungen für Datentransporte in kleineren Speichern zustande, sondern auch durch den Einsatz besserer und teurerer Technik für kleinere Speicher (schnellere Schalter, kleinere physikalische Kapazitäten) ohne einen proportionalen Anstieg der Gesamtkosten für eine Speicherhierarchie zu verursachen.

Es wurden mit der Zeit verschiedene Methoden erdacht, Zwischenspeicher zu organisieren und zu verwalten, die jeweils unterschiedlich viel Verwaltungsinformation benötigen und den Zwischenspeicher verschieden gut ausnutzen. Zwischenspeicher, die sich von vielen Programmen gut nutzen lassen, haben meist einen höheren Verwaltungsaufwand als solche, deren Nutzung etwas eingeschränkter ist. Diese Aspekte werden detailliert im nächsten Abschnitt betrachtet. Bei der Konstruktion einer Speicherhierarchie muß abgewogen werden, welcher Kompromiß zwischen Nutzbarkeit und Verwaltungsaufwand sinnvoll ist.

#### 2.2 Aufbau eines Caches

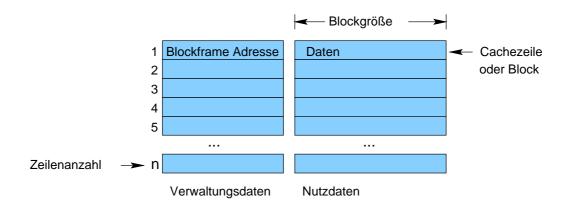

Der Aufbau eines Caches beeinflußt die Komplexität, den Platzverbrauch, die Nutzbarkeit und die Geschwindigkeit des Caches. Caches mit hoher Assoziativität (siehe unten) sind aufwendiger, aber im allgemeinen auch effektiver nutzbar als Caches mit niedriger Assoziativität. Ein Cache ist, wie in Abbildung 2.2 dargestellt, in Blöcke (auch Cache-Zeilen oder Cachelines genannt) aufgeteilt. Aus der Blockgröße und der Blockanzahl ergibt sich die Speicherkapazität des Caches. Für die Verwaltung der Daten im Cache wird eine Blockframe Adresse gespeichert, durch die eindeutig wird, welche Adressen in der entsprechenden Cache-Zeile gerade zwischengespeichert sind. Dafür werden die letzten Bits der Adresse weggelassen und so die Blockframe Adresse bestimmt. Die letzten Bits einer Adresse bestimmen die genaue Position der Daten innerhalb einer Cache-Zeile.

Abbildung 2.2: Ein Cache speichert Daten in Einheiten der Blockgröße. Damit die Daten ihrer Adresse zugeordnet werden können, muß Verwaltungsinformation gespeichert werden (Blockframe Adresse), bei der die letzten Bits der Adresse weggelassen werden. Die letzten Bits einer Adresse bestimmen die genaue Position der Daten innerhalb einer Cache-Zeile. Die Kapazität des Caches ergibt sich aus der Blockgröße und der Zeilenanzahl.

#### **Ereignisse in einem Cache**

Während der Nutzung eines Caches können verschiedene Ereignisse eintreten. Von einem "Cache-Hit" spricht man, wenn angeforderte Daten im Cache zwischengespeichert sind. Müssen Daten erst aus einer größeren Speicherebene in den Cache kopiert werden, spricht man von einem "Cache-Miss". Die Phrase "Zugriff auf eine Speicherebene" soll heißen, daß diese Speicherebene einen Cache-Hit hat.

#### Assoziativität

Als Assoziativität eines Caches bezeichnet man die Anzahl der verschiedenen Cache-Zeilen, in denen das Datum einer gegebenen Adresse zwischengespeichert werden kann. Die Assoziativität wird als ganze positive Zahl angegeben.

Bei Assoziativität 1 steht mit der Adresse auch fest, in welcher Cache-Zeile sie zwischengespeichert wird. Caches mit Assoziativität 1 werden auch "Direct-Mapped-Caches" genannt. Bei höherer Assoziativität wird der Cache in "Sets" eingeteilt, die jeweils wie ein Direct-Mapped-Cache arbeiten. Einen Cache mit einer Assoziativität, die der Cache-Zeilenanzahl entspricht, nennt man "vollassoziativ". Bei einem vollassiziativen Cache kann jede Adresse in jeder Cache-Zeile zwischengespeichert werden.

Einfluß der Assoziativität Caches mit niedriger Assoziativität sind gut von Programmen nutzbar, die eine hohe Lokalität der benötigten Speicherzellen aufweisen (benachbarte Speicherzellen werden häufig gemeinsam benötigt). Je höher die Assoziativität eines Caches ist, desto besser kann er auch von Programmen, deren räumliche Datenlokalität nicht so hoch ist, durch temporäre Lokalität genutzt werden. Bei solchen Programmen entstehen bei Caches niedrigerer Assoziativität Verdrängungseffekte, obwohl andere Teile des Zwischenspeichers Daten speichern, die das Programm gerade nicht benötigt. Allerdings bedeutet eine höhere Assoziativität eine aufwendigere Schaltung und mehr administrative Daten und damit

2.2 Aufbau eines Caches 7

einen insgesamt höheren Verwaltungsaufwand. Auch die Zeit für das Testen auf einen Cache-Hit wird mit größerer Assoziativität höher, da eine Adresse an mehreren Stellen im Cache zwischengespeichert sein kann.

#### Ersetzungsstrategien

Wenn vom Prozessor eine Speicherzelle angefordert wird, die bisher nicht im Cache zwischengespeichert ist, und keine passenden freien Cache-Zeilen mehr im Cache vorhanden sind, muß entschieden werden, welche Cache-Zeile im Cache ersetzt wird. Eine Ersetzungsstrategie ist nur erforderlich, wenn der Cache eine Assoziativität größer als 1 hat (nicht Direct-Mapped), weil sonst ohnehin nur eine Cache-Zeile zur Speicherung der angeforderten Adresse in Frage kommt. Die Assoziativität des Caches gibt die Anzahl von möglichen Cache-Zeilen an, aus denen ausgewählt werden muß. Folgende Verfahren sind üblich:

**FIFO:** First in First out; Die Cache-Zeile, die sich zeitlich am längsten im Cache befindet, wird ersetzt.

LRU: Least Recently Used; Die Cache-Zeile, die am längsten nicht benutzt wurde, wird ersetzt.

Round Robin: Die Cachzeilen werden reihum ersetzt.

Random: Die zu ersetzende Cachzeile wird zufällig ausgewählt.

Je nach benutzter Ersetzungsstrategie werden unterschiedliche Verwaltungsinformationen im Cache benötigt: Bei LRU muß bekannt sein, welche Cache-Zeile am längsten nicht benutzt wurde, bei Round Robin, welche Cache-Zeile als nächste zu ersetzen ist, und bei Random muß eine Zufallszahl generiert werden.

#### Schreibstrategien

Schreibt der Prozessor Daten, wird dies je nach Schreibstrategie der Zwischenspeicher unterschiedlich behandelt. Es gibt folgende Schreibstrategien:

Write Back: Die Daten werden zunächst nur in den Cache geschrieben und erst in eine höhere Speicherebene, wenn die Cache-Zeile ersetzt werden soll. Diese Strategie führt zu etwas längeren Latenzzeiten bei einer Ersetzung einer Cache-Zeile, da eventuell noch die zwischengespeicherten Daten in die nächste Speicherebene geschrieben werden müssen. Zur Verwaltung wird je Cache-Zeile ein Bit benötigt, das speichert, ob die Daten in dieser Cache-Zeile modifiziert wurden (dirty-bit).

Write Through: Die Daten werden in die nächste Speicherebene und in den Cache geschrieben. Diese Variante ist einfacher als Write Back zu realisieren. Der Nachteil ist eine stärkere Speicherbusbelastung, da bei jeder Änderung die Daten in die nächste Speicherebene geschrieben werden. Die Latenzzeit zum Schreiben in den Hauptspeicher wird dabei vor dem Prozessor verborgen.

#### Lesestrategien

Ein Cache ersetzt immer eine ganze Cache-Zeile. Es gibt aber Architekturen, bei denen der Speicherbus wegen der Busbreite nicht eine komplette Cache-Zeile in einem Stück liefert, so daß bestimmte Daten eher ankommen. In diesem Fall arbeitet der Cache mit einer der folgenden Lesestrategien. Entweder die Cache-Zeile wird konsekutiv vom Anfang bis zum Ende gefüllt und die benötigten Daten an den Prozessor geschickt oder die vom Prozessor benötigten Daten werden zuerst angefordert, direkt an den Prozessor weitergeleitet und danach der Rest der Cache-Zeile gefüllt, wodurch die Latenzzeit für den Prozessor reduziert werden kann.

#### 2.3 Neuartige Strategien für die Nutzung von Zwischenspeichern

Für eine bessere Ausnutzung der temporalen und räumlichen Lokalität von Daten schlagen PRVULOVIĆ et al. (1999a,b) eine statische Aufspaltung des Caches in zwei Teile vor. Der eine Teil soll für temporal lokale Daten genutzt werden und dementsprechend eine kleine Blockgröße und hohe Assoziativität aufweisen. Der andere Teil soll räumlich nahe beieinander liegende Speicherzugriffe optimieren und deshalb eine große Blockgröße aufweisen und zusätzlich mit einer Erkennung für Zugriffe mit gleicher Schrittweite ausgestattet werden, um Daten schon vor ihrem Zugriff in den Cache zu laden. Meßergebnisse zeigen, daß die durchschnittliche Latenzzeit der Caches durch diese Architektur in vielen Anwendungen verringert werden kann. Gemessen wurden die Ausführungszeiten von Programmen aus der SPEC95 Benchmark Suite (DIXIT und REILLY, 1995).

Eine noch höhere Flexibilität der Nutzung der Caches bieten RANGANATHAN et al. (2000) mit einer neuartigen Strategie für die Nutzung von Zwischenspeichern. Ihren rekonfigurierbaren Caches liegt die Idee zugrunde, einen Cache während der Ausführungszeit dynamisch in Bereiche zu unterteilen, die nach unterschiedlichen Strategien arbeiten. Bei einer Anfrage wird in allen Bereichen gleichzeitig geprüft, ob sie die angefragten Daten liefern können. Angedacht ist zum Beispiel auch, daß ein Bereich des Zwischenspeichers so konfiguriert werden kann, daß er durch den vom Compiler generierten Code kontrolliert wird und als schneller temporärer Speicher genutzt wird. RANGANATHAN et al. versprechen sich dadurch die Beschleunigung von Prozessen, die auf großen Datenmengen arbeiten (sogenanntes "Media Processing"), indem nur wiederverwendbare Daten zwischengespeichert werden, die bei einer normalen Ersetzungsstrategie eines Zwischenspeichers immer wieder durch die zu bearbeitenden Daten aus dem Zwischenspeicher verdrängt würden.

# Speicherhierarchien von symmetrischen Multiprozessorsystemen

Der Kern des Lebens ist asymmetrisch.

- DOMINIK BENDER

In diesem Kapitel werden die zusätzlichen Konzepte für Speicherhierarchien von symmetrischen Multiprozessorsystemen (SMP-Systemen) eingeführt. Das wichtigste Konzept hierbei ist das Kohärenzprotokoll für Zwischenspeicher. Nach einer Erläuterung, weshalb Kohärenzprotokolle benötigt werden, und einer Unterteilung der möglichen Kohärenzprotokolle in zwei Gruppen (aktualisierende und invalidierende) werden zwei Protokolle (MSI und MESI) vorgestellt.

#### 3.1 Symmetrische Multiprozessorsysteme (SMP-Systeme)

Symmetrische Multiprozessorsysteme (SMP-Systeme) sind Systeme, in denen sich mehrere Prozessoren einen gemeinsamen Hauptspeicher teilen und alle Prozessoren auf die gleiche Weise auf den Hauptspeicher zugreifen können. Jeder Prozessor hat seine eigenen Caches und der gemeinsame Speicher wird meist über einen gemeinsamen Speicherbus angesteuert. Diese Architektur ist für eine kleine bis mittlere Anzahl von Prozessoren geeignet. Bei einer größeren Anzahl von Prozessoren würde der Speicherbus zum Engpaß werden, und die Anwendungen würden nicht mehr gut skalieren.

Die Zugriffe auf den gemeinsamen Speicher finden aufgrund der Busarchitektur in SMP-Systemen sequentialisiert statt. Eine SMP-Architektur sorgt mit Hilfe von Kohärenzprotokollen dafür, daß auch durch die Nutzung der Caches für lesende und schreibende Zugriffe eine sequentialisierte Zugriffsweise auf Speicheradressen für alle Prozessoren als Modell der Speicherhierarchie gültig bleibt. Dadurch eignet sich diese Architektur gut zur parallelen Programmierung, da das Speichermodell aus Sicht der einzelnen Prozessoren sehr einfach ist und alle Speicherzugriffe die gleiche Semantik wie Hauptspeicherzugriffe haben. Der Datenaustausch zwischen Prozessoren geschieht über Zugriffe auf gemeinsame Adressen und verursacht keinen weiteren Protokollaufwand wie etwa das Kopieren der Daten in Zwischenpuffer, Einteilung in Pakete, Erstellen von Protokollpaketen und Kontrolle über die korrekte Übertragung, bei nachrichtengekoppelten Systemen. Welche Probleme durch prozessorlokale Caches auftreten können, und warum Kohärenzprotokolle notwendig sind, um für alle Prozessoren das Modell der sequentialisierten Speicherzugriffe aufrecht zu erhalten, soll der folgende Abschnitt klären.

#### 3.2 Zweck und Arten von Kohärenzprotokollen

Sollen zwischen Prozessoren in einem SMP-System Daten ausgetauscht werden, geschieht dies über gemeinsam genutzte Adressbereiche der Prozessoren: Ein Prozessor schreibt Daten und ein anderer liest sie anschließend. Bei einem Arbeitsspeicher, der die Speicherzugriffe sequentialisiert abarbeitet, verhält sich alles so, wie der Programmierer es erwarten würde. Wird eine Adresse (egal von welchem Prozessor) gelesen, nachdem ein anderer dort Daten geschrieben hat, bekommt er die zuletzt geschriebenen Daten. Haben die Prozessoren eigene Zwischenspeicher, kann es passieren, daß ein Prozessor Daten nur in seine Zwischenspeicher schreibt (bei der Write Back Strategie) und ein anderer Prozessor veraltete Daten aus seinen Zwischenspeichern liest, so daß ein Datenaustausch fehlschlägt.

Um dieses Problem zu lösen, gibt es zwei Möglichkeiten. Entweder man überläßt den Prozessoren (und somit den Compilern) das Problem und gibt ihnen über einen geeigneten Instruktionssatz die Möglichkeit, zu wählen, ob Speicherzugriffe auf den Hauptspeicher oder die Zwischenspeicher erfolgen, und ob diese die Inhalte von Zwischenspeichern anderer Prozessoren beeinflussen, oder man sorgt mit Hilfe eines Kohärenzprotokolls dafür, daß die Zwischenspeicher für die Prozessoren transparent genutzt werden. Ein Kohärenzprotokoll hat die Aufgabe, die getrennten Zwischenspeicher der Prozessoren so zu verwalten, daß keine Inkonsistenzen gegenüber dem Verhalten eines Systems ohne Zwischenspeicher entstehen. Um diese Aufgabe zu erfüllen, wurden verschiedene Protokolle entwickelt, die sich in zwei Klassen einteilen lassen:

**Update based:** Protokolle, die nach diesem Verfahren arbeiten, aktualisieren bei Bedarf Zwischenspeicher anderer Prozessoren mit aktuell geschriebenen Daten, so daß diese Zwischenspeicher weiter genutzt werden können. Ein Protokoll dieser Art ist zum Beispiel das Dragon-Kohärenzprotokoll.

Invalidation based: Protokolle, die nach diesem Verfahren arbeiten, markieren bei Bedarf Inhalte von Zwischenspeichern anderer Prozessoren als ungültig, so daß ein Zugriff auf die betroffenen Adressen einen Zugriff auf den Speicherbus bewirkt. Beispiele für diese Art von Protokollen sind das MSI- und das MESI-Protokoll.

Für beide Arten von Protokollen gibt es verschiedene Möglichkeiten diese zu realisieren. Kohärenzprotokolle sind detailliert in CULLER und SINGH (1999) beschrieben. Folgend sollen zwei weit verbreitete Kohärenzprotokolle vorgestellt werden, da sie im weiteren Verlauf der Arbeit zur Simulation der Speicherhierarchie eines SMP-Systems mit zwei Pentium III Prozessoren genutzt werden (siehe Kapitel 7 ab Seite 46).

#### 3.3 Kohärenzprotokoll MSI

Das MSI-Protokoll ist ein auf Invalidation beruhendes Kohärenzprotokoll, das auf drei Zuständen basiert, die jede Cache-Zeile einnehmen kann. Die drei Zustände, aus deren Anfangsbuchstaben der Name des Protokolls gebildet ist, sind:

**Modified:** In diesem Zustand befinden sich Cache-Zeilen, die nach dem Laden modifiziert wurden. Nur jeweils ein Prozessor kann für Adressen einer Cache-Zeile eine Cache-Zeile in diesem Zustand haben. Andere Prozessoren haben diese Adresse nicht gültig in ihren Zwischenspeichern. Lese- und Schreiboperationen können ohne Benachrichtigung anderer Prozessoren ausgeführt werden.

**Shared:** In diesem Zustand befinden sich Cache-Zeilen, auf die bisher nur lesend zugegriffen wurde. Es können mehrere Prozessoren die gleiche Adresse gleichzeitig in ihren Zwischenspeichern haben.

Invalid: In diesem Zustand befinden sich Cache-Zeilen, die keine gültigen Inhalte mehr enthalten. In diesen Zustand werden alle Cache-Zeilen anderer Prozessoren gesetzt, die vorher im Zustand Shared waren, wenn ein Prozessor eine Adresse in seinen Cache schreibt (seine Cache-Zeile auf Modified setzt).

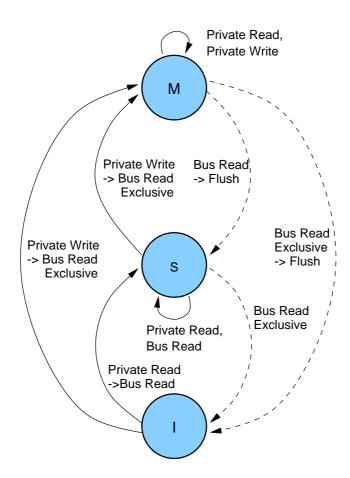

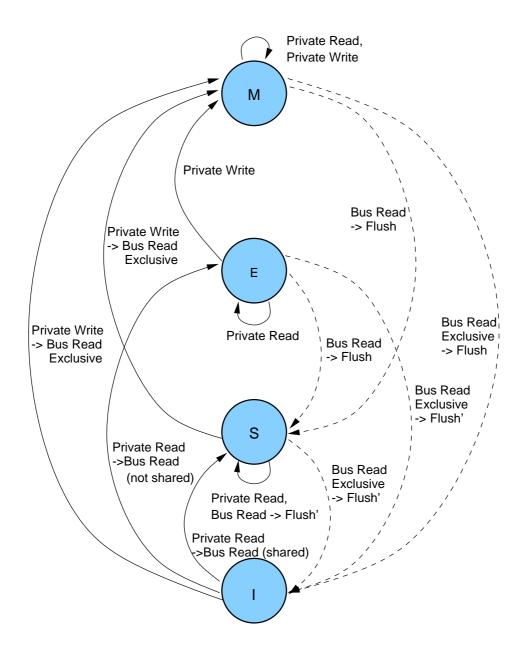

Je nach Ausgangszustand und Ereignis wechseln die Cache-Zeilen zwischen diesen drei Zuständen, von denen auch abhängig ist, wie die Cache-Controller sich verhalten. Der Zustandsgraph in Abbildung 3.1 stellt die genauen Zustandsübergänge dar. Ist zum Beispiel eine Cache-Zeile A im Zustand *Modified* und ein anderer Cache B liest diese Adresse, wird das Bus-Ereignis "Bus Read" oder "Bus Read Exclusive" ausgelöst. Dadurch wird der Zustand der Cache-Zeile A auf *Shared* gesetzt und deren Inhalt auf den Bus geschrieben ("Flush"), so daß der aktuelle Inhalt von Cache B übernommen werden kann. Modifizieren mehrere Prozessoren nahe beieinanderliegende oder gleiche Adressen, invalidieren sie sich gegenseitig die Zwischenspeicher, wodurch Daten häufiger aus dem Hauptspeicher gelesen werden müssen.

#### 3.4 Kohärenzprotokoll MESI

Das MESI-Protokoll ist eine Erweiterung des MSI-Protokolls und wird in modernen Mehrprozessorsystemen wie zum Beispiel Systemen der Intel Pentium Reihe (MINDSHARE, INC. und SHANLEY, 1999) eingesetzt. Zusätzlich zu den drei Zuständen des MSI-Protokolls kommt ein weiterer Zustand Exclusive hinzu. In diesem Zustand befindet sich eine Cache-Zeile, deren Adressen kein anderer Prozessor in seinen Zwischenspeichern hat, so daß bei schreibenden Zugriffen keine anderen Cache-Zeilen auf Invalid gesetzt werden müssen. Es ist nicht zwingend, daß eine Cache-Zeile, die in keinem Zwischenspeicher anderer Prozessoren gespeichert ist, in diesem Zustand ist. Eine solche Cache-Zeile könnte auch im Zustand Shared sein. Nur beim Laden einer Cache-Zeile wird überprüft, ob andere Caches diese bereits zwischenspeichern. Ist dies nicht der Fall, wird die neue Cache-Zeile auf den Zustand Exclusive gesetzt. Bei einer Schreiboperation wechselt der Zustand dann ohne Bus-Ereignis auf Modified. Der zusätzliche Zustand Exclusive hilft Bandbreite auf dem Speicherbus bei sequentiellen Programmen zu sparen, die keine gemeinsamen Daten von Prozessoren nutzen.

Abbildung 3.2 zeigt den für das MESI-Protokoll modifizierten Zustandsgraphen. Je weiter oben in dieser Abbildung ein Zustand angeordnet ist, desto mehr sind Daten einer Cache-

Abbildung 3.1: Der Zustandsgraph des MSI-Protokolls nach Culler und Singh (1999). Die Zustände M, S, I stehen für *Modified*, *Shared* und *Invalid*. Es werden Ereignisse, die vom Prozessor ausgehen, und Bus-Ereignisse, die von Cache-Controllern ausgehen, unterschieden. Gestrichelte Pfeile stellen Zustandsübergänge dar, die durch Bus-Ereignisse hervorgerufen werden. Eine Aktion kann weitere Bus-Ereignisse verursachen. Dies wird durch einen Pfeil A -> B dargestellt und bedeutet, daß durch Ereignis A das Bus-Ereignis B verursacht wird. Das Ereignis "Flush" bedeutet dabei, daß der Inhalt der Cache-Zeile auf den Bus geschrieben wird.

Zeile in diesem Zustand einem Prozessor zugeordnet und können schlechter von Caches verschiedener Prozessoren gleichzeitig zwischengespeichert werden.

Das Bus-Ereignis "Bus Read" liefert beim MESI-Protokoll zunächst ein Resultat zurück, ob der Inhalt in anderen Caches gefunden wurde. Anschließend werden die Daten übertragen und ein Zustandsübergang vom Zustand *Invalid* in den Zustand *Shared* oder *Exclusive* durchgeführt. Das Bus-Ereignis "Flush" bedeutet, daß potenziell mehrere Prozessoren oder Caches die aktuellen Daten auf den Bus schreiben könnten, aber nur einer ausgewählt wird, der dies tut.

Auch beim MESI-Protokoll invalidieren sich Prozessoren gegenseitig ihre Caches, wenn sie gleichzeitig nahe beieinanderliegende Adressen modifizieren, was zu Leistungseinbußen führen kann. In Abschnitt 7.4 ab Seite 46 wird dies an einem Beispiel gezeigt.

Abbildung 3.2: Der Zustandsgraph des MESI-Protokolls nach Culler und Singh (1999). Die Zustände M, E, S, I stehen für *Modified, Exclusive, Shared* und *Invalid.* Wie in Abbildung 3.1 werden Ereignisse, die vom Prozessor ausgehen, und Bus-Ereignisse, die von Cache-Controllern ausgehen, unterschieden. Gestrichelte Pfeile stellen Zustandsübergänge dar, die durch Bus-Ereignisse hervorgerufen werden.

## **Microbenchmarks**

Durch das Einfache geht der Eingang zur Wahrheit.

- GEORG CHRISTOPH LICHTENBERG (1742 - 1799)

Microbenchmarks sind kleine, einfache Benchmarks, die spezielle Systemparameter wie Prozessortakt oder Speicherlatenzzeiten messen. Für diese Messungen ist es wichtig, die Genauigkeit der Zeitmeßroutinen zu bestimmen, damit Messungen so lange ausgeführt werden, daß zuverlässige Resultate ermittelt werden können. Hierfür wird ein Microbenchmark zum Messen der Meßgenauigkeit vorgestellt. Wie man unabhängig von der Prozessorarchitektur den Prozessortakt bestimmen kann, wird in Abschnitt 4.3 erläutert.

Mit Microbenchmarks können außerdem wichtige Parameter einer Speicherhierarchie, wie die Anzahl der Speicherebenen, die Größe, die Blockgröße und die Latenzzeitsen von Speicherebenen, durch Messen ermittelt werden. Diese Daten können dann für die Konfiguration eines Simulators für Speicherhierarchien genutzt werden. Daß die Speicherhierarchie, zu der auch die Register eines Prozessors gehören, sehr wichtig für die Leistung ist, die ein Prozessor Anwendungen zur Verfügung stellt, wird am Beispiel des Horner-Schema-Benchmarks ab Seite 21 gezeigt.

#### 4.1 Zweck von Microbenchmarks

Nach CULLER und SINGH (1999) dienen Microbenchmarks dazu, die Leistung einer bestimmten Teilfunktion eines Systems zu messen. Dabei versucht man, andere Einflußfaktoren auszuschließen, so daß die Ergebnisse einfach zu interpretieren sind und mit der Leistung der korrespondierenden Hardware verglichen werden können. Typische Microbenchmarks messen beispielsweise Latenzzeiten von Speichern, Speicherbandbreiten, Taktraten von Prozessoren, Rechengeschwindigkeit von Prozessoren oder den Aufwand für einen Unterprogrammaufruf.

Diese Daten, die Microbenchmarks ermitteln, sind oft auch schon in Beschreibungen der Hardwarehersteller vorhanden. Der Einsatz von Microbenchmarks ist trotzdem gerechtfertigt, um einerseits die Daten der Hardwarehersteller zu überprüfen, und andererseits die Daten unter realen Bedingungen zu messen. Benutzt man verschiedene Compiler, um einen Microbenchmark zu übersetzen, kann man den generierten Code vergleichen und Hochsprachen auf Leistungsunterschiede untersuchen (siehe Abschnitt 4.6). Ein aus einer Hochsprache mit einem Compiler übersetzter Microbenchmark wird Leistungswerte, die eine reale Applikation erreichen kann, besser widerspiegeln, als ein direkt in Maschinensprache implementierter und optimierter Microbenchmark.

In den folgenden Abschnitten sollen verschiedene Microbenchmarks vorgestellt werden. Da Benchmarking und Leistungsanalyse zentrale Gebiete als Voraussetzung für Optimierungen sind, gibt es mittlerweile sehr viele Microbenchmarks, so daß ein Anspruch auf eine vollständige Betrachtung hier nicht erhoben werden kann. Vielmehr soll eine kleine Auswahl getroffen werden, an der man erkennen kann, wie unterschiedliche Microbenchmarks funktionieren und welche Daten man mit Microbenchmarks über eine Rechner- und Speicherarchitektur ermitteln kann.

#### 4.2 Genauigkeit der Zeitmessung

Dadurch, daß die Geschwindigkeit von Prozessoren zur Zeit immer weiter steigt, ist es schwierig, Benchmarks zu schreiben, die für mehrere Prozessorgenerationen zuverlässige Ergebnisse liefern. Kann ein Benchmark von schnellen Prozessoren zu schnell abgearbeitet werden, gelangt man an die Grenze der Meßgenauigkeit der Zeitmeßfunktionen. Gestaltet man andererseits den Benchmark aufwendiger, benötigt eine Messung auf einem langsameren Prozessor unnötig viel Zeit.

Durch das Messen der Genauigkeit der Zeitmessung kann eine Mindestausführungszeit für einen Microbenchmark festgelegt und die Anzahl der Wiederholungen des Benchmarks variabel gestaltet werden. Beispielsweise benutzen McVoy und Staelin (1996) für die Ermittlung der Genauigkeit der Funktion gettimeofday() ein Verfahren, bei dem sie einen Block von Anweisungen solange vergrößern, bis eine geringe Änderung der Anzahl der wiederholten Ausführungen dieses Blocks eine entsprechend kleine Änderung der dafür benötigten Zeit ergibt. Würde sich zum Beispiel die gemessene Zeit gar nicht ändern, egal ob man den Anweisungsblock einmal oder zweimal ausführt, ist der Block und die Zeit, die für seine Ausführung benötigt wird, zu klein, um aussagekräftige Ergebnisse zu erhalten. Der Anweisungsblock wird inkrementell soweit vergrößert, daß die Ungenauigkeit höchstens 1% beträgt. Dieses Verfahren ist üblich und wird auch in anderen Benchmarksammlungen wie PARKBENCH (HOCKNEY und BERRY, 1993) eingesetzt, um die Genauigkeit von Zeitmeßroutinen zu bestimmen.

#### 4.3 Bestimmung des Prozessortaktes

Der Prozessortakt eines Prozessors läßt sich einfach bestimmen, wenn von einer Instruktion des Prozessors bekannt ist, wieviele Takte sie benötigt. In diesem Fall führt man diese Funktion so häufig aus, daß die Meßgenauigkeit ausreicht und kann sich so den Prozessortakt ausrechnen. Diese Methode funktioniert nur für bekannte Prozessortypen zuverlässig. Außerdem wird dadurch der Microbenchmark in der Portabilität eingeschränkt. Diese Methode wurde noch in Imbench 1.0 (1996), einer Benchmarksammlung von McVoy und STAELIN (1996), eingesetzt.

McVoy und Staelin haben für Imbench 2.0 (1998) ihren Microbenchmark *mhz* in ANSI-C implementiert und eine portable Methode gefunden, den Prozessortakt zu bestimmen. Zunächst werden die Ausführungszeiten für neun verschiedene Anweisungsfolgen gemessen, die so ausgesucht sind, daß sie sich möglichst geringfügig in der Anzahl der benötigten Takte unterscheiden. Die Berechnung des größten gemeinsamen Teilers dieser Zeiten

ergibt dann die Zeit, die ein Takt des Prozessors benötigt, wenn mindestens zwei der Anweisungsfolgen eine zueinander prime Taktanzahl (kein gleicher Primfaktor) benötigen. Um wegen der Meßgenauigkeit lange genug zu rechnen, wird die gleiche Anweisungsfolge (zum Beispiel die 5. Anweisungsfolge) wiederholt, bis die Ausführungszeit lang genug ist. Damit der Prozessor mindestens einen Takt je Anweisung benötigt und nicht zwei Anweisungen in einem Takt bearbeiten kann, sind die Anweisungen so gestaltet, daß für die Ausführung einer Anweisung das Ergebnis der vorherigen benötigt wird (streng sequentiell).

Die neun verschiedenen ANSI-C Anweisungsfolgen sind:

```

1. p = *p;

2. a ^ = a + a;

3. a ^ = a + a + a;

4. a » = b;

5. a » = a + a;

6. a ^ = a « b;

7. a ^ = a + b;

8. a += (a + b) & 07;

9. a ++; a ^ = 1; a «= 1;

```

Angenommen die 4. Anweisungsfolge benötigt 12 ns und die 5. Anweisungsfolge benötigt 18 ns, dann kann über den größten gemeinsamen Teiler (in diesem Fall 6) die Zeit für einen Takt errechnet werden (maximal 6 ns). Wenn die Anzahl der tatsächlich benötigten Takte zweier Anweisungsfolgen zueinander prim ist, ist die wirkliche Taktdauer des Prozessors bestimmt (6 ns), weil kein gemeinsamer Faktor das Ergebnis verfälschen kann (sonst zum Beispiel auch 3 ns Taktdauer bei 2 als gemeinsamem Faktor oder 2 ns Taktdauer bei 3 als gemeinsamem Faktor). Da die Anweisungsfolgen aber extra so gewählt sind, daß sie sich möglichst wenig in der Anzahl der Takte, die für die Bearbeitung benötigt werden, unterscheiden, ist die Wahrscheinlichkeit, daß es nicht zwei Anweisungsfolgen gibt, die eine zueinander relativ prime Taktanzahl benötigen, gering.

Daß dieses Verfahren tatsächlich funktioniert, haben McVoY und STAELIN dadurch gezeigt, daß sie es an vielen Prozessorarchitekturen erfolgreich ausprobiert haben. Zu ihnen gehören PA-RISC (PA-7000, PA-7200, PA-8000), Intel (486, Pentium, PentiumPro, Pentium II), DEC Alpha, PowerPC (PPC-603, PPC-604, PPC-604e), AMD (K5, K6), Sun (MicroSPARC, SuperSPARC, Ultra-I, Ultra-II), MIPS (R4000, R5000, R6000), Cyrix und Motorola 68020. Außerdem wurden für die Tests verschiedene Betriebssysteme genutzt.

McVoy und Staelin erwarten, daß mit diesen Anweisungen aufgrund der sequentiellen VLIW Abhängigkeit der Anweisungen auch auf Prozessoren mit "Very Large Instruction Word" (VLIW) Architektur, wie der IA-64 Architektur, richtige Ergebnisse ermittelt werden können.

#### 4.4 Latenzzeiten von Speicherebenen

Mit einem Microbenchmark, der die Latenzzeiten der verschiedenen Speicherebenen bei Lesezugriffen mißt, kann man herausfinden, wie lange der Prozessor auf angeforderte Daten warten muß, ehe sie in einem Register vorliegen. Das Messen der Latenzzeiten für das Schreiben von Daten ist schwieriger, da man nicht so leicht erkennen kann, wann ein Schreibvorgang beendet ist. Verschiedene Schreibstrategien, siehe Abschnitt 2.2 auf Seite 7, verbergen tatsächliche Latenzzeiten beim Schreiben vor dem Prozessor.

Mit genauer Kenntnis über Speicherlatenzzeiten kann ein Programmierer oder Compilerbauer versuchen, die Wartezeiten mit sinnvollen Instruktionen zu füllen, indem Anweisungen umgeordnet werden.

Wartezeiten nutzen

Im Rahmen dieser Arbeit wurde ein nach dem im folgenden beschriebenen Verfahren arbeitender Microbenchmark zum Messen von Latenzzeiten implementiert und angewandt.

#### Messen von Speicherlatenzzeiten

Um die Latenzzeiten des L1 Caches, L2 Caches und Hauptspeichers zu messen, werden Ladeoperationen, mit verschiedenen Abständen der geladenen Adressen zueinander, durchgeführt. Ladeoperationen über verschieden große Speicherbereiche hinweg können Kapazitätsgrenzen von Zwischenspeichern anhand steigender Latenzzeiten deutlich machen, weil größere Zwischenspeicher üblicherweise auch längere Latenzzeiten haben.

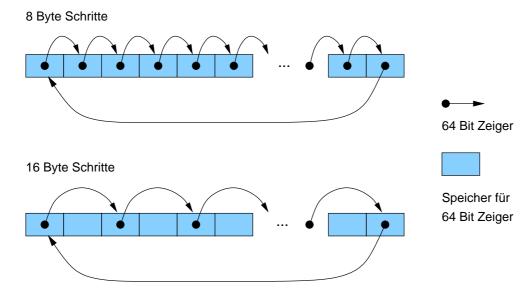

Abbildung 4.1: Die obige Datenstruktur, mit der Ladeoperationen sukzessive gezielt auf Adressen zugreifen, kann zum Messen von Speicherlatenzzeiten genutzt werden. Um verschiedene Speicherebenen zu erreichen, wird der Abstand zwischen aufeinanderfolgend geladenen Adressen und der zu durchlaufende Speicherbereich immer weiter vergrößert. Irgendwann sind Blockgröße und Schrittweite so groß, daß der Ln Cache komplett überschrieben wird und jeder Speicherzugriff ein Laden aus dem Ln+1 Cache bewirkt.

Dazu werden Speicherbereiche, wie in Abbildung 4.1 dargestellt, benutzt. Der Benchmark lädt entlang der Referenzen immer den Inhalt der nächste Zelle und benutzt diesen Inhalt als Referenz auf die nächste Zelle. Der Prozessor kann nicht mehrere Ladeoperationen gleichzeitig verarbeiten, da die Ladeoperationen streng sequentiell voneinander abhängen. Der Benchmark benötigt außer der Ladeoperation und ein paar Operationen zur Schleifenverwaltung keine anderen Operationen. Die durchschnittliche Latenzzeit ergibt sich aus der gemessenen Gesamtausführungszeit geteilt durch die Anzahl der durchgeführten Ladeoperationen. Um die Messung zu verbessern, kann jede Ladeoperation mit einem Verwaltungsaufwand von einem Prozessortakt angenommen werden und zusätzlich

| Architektur:            | Alpha 21164 | Pentium II/III | IBM RS/6000   |

|-------------------------|-------------|----------------|---------------|

| Prozessor               |             |                |               |

| MHz                     | 600         | 400/500        | 25            |

| Gleitkommazahl Register | 32          | 8              | 32            |

| L1 Cache                |             |                |               |

| Gesamtgröße             | 8 kB        | 16 kB          | 128 kB        |

| Blockgröße              | 32 Bytes    | 32 Bytes       | 1024 Bytes    |

| Cache-Zeilen            | 256         | 512            | 128           |

| Assoziativität          | 1           | 2              | 4             |

| Ersetzungsstrategie     | entfällt    | lru            | random        |

| Latenzzeit              | 2 Takte     | 3 Takte        | 1 Takt        |

|                         |             |                |               |

| L2 Cache                |             |                | Hauptspeicher |

| Gesamtgröße             | 96 kB       | 256 kB         | 48 MB         |

| Blockgröße              | 64 Bytes    | 32 Bytes       | 4096 Bytes    |

| Cache-Zeilen            | 1536        | 8192           | 12288         |

| Assoziativität          | 3           | 4              | _             |

| Ersetzungsstrategie     | random      | lru            | random        |

| Latenzzeit              | 8 Takte     | 20 Takte       | 40 Takte      |

Tabelle 4.1: Die Parameter verschiedener Speicherhierarchien beeinflussen deren Ausnutzung. Angegeben sind die Daten eines Alpha 21164 in einer Cray T3E, eines Pentium II Prozessors in einem PC mit 100 MHz Frontsidebus und einer IBM RS/6000.

zum Schleifenverwaltungsaufwand vom gemessenen Ergebnis subtrahiert werden. Die Speicherbereiche werden für jede Messung mehrmals durchlaufen. Die Größe des zu durchlaufenden Speicherblocks wird für verschiedene Messungen variiert, um die Kapazitätsgrenzen der einzelnen Zwischenspeicher zu ermitteln. Bei kleinen zu durchlaufenden Blöcken passen alle Daten komplett in einen Zwischenspeicher. Ist der zu durchlaufende Block größer als der Zwischenspeicher, müssen die Daten aus dem Ln+1 Cache geladen werden, der längere Latenzzeiten hat.

Wenn Daten noch nicht im Zwischenspeicher enthalten sind, wird immer eine ganze Cache-Zeile in den Zwischenspeicher kopiert. Zugriffe auf folgende, benachbarte Adressen sind dann solange schneller, bis die Cache-Zeile diese Daten wegen ihrer begrenzten Länge nicht mehr bereitstellt und erneut Daten in den Cache kopiert werden müssen. Wenn die Cache-Zeilenlänge zu gering ist, können schrittweise Speicherzugriffe dazu führen, daß jeder Zugriff das Kopieren einer Cache-Zeile in den Cache erfordert.

An den Latenzzeitdiagrammen, die mit dem Latenzzeit-Microbenchmark erstellt werden, kann man die Latenzzeiten der verschiedenen Speicherebenen, deren Gesamtgröße und die jeweilige Blockgröße ablesen, wie die folgenden Abschnitte an zwei Beispielen zeigen werden. Aus der Blockgröße und der Gesamtgröße läßt sich dann einfach die Cache-Zeilenanzahl berechnen. Die tatsächlichen Daten der Speicherhierarchien der beiden im folgenden betrachteten Systeme sind in Tabelle 4.1 dargestellt.

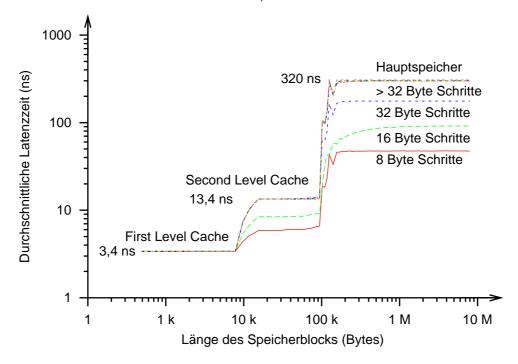

#### Speicherlatenzzeiten auf einer Cray T3E

Die Cray T3E benutzt einen DEC Alpha 21164 Prozessor mit L1 und L2 Cache. Außerdem hat die Cray T3E sogenannte "Stream Buffers" (ANDERSON et al. 1997; OED 1996), die konsekutive Zugriffe auf den Hauptspeicher beschleunigen können. Für die Messungen wurden diese Stream Buffers jedoch abgeschaltet, um die Ergebnisse besser mit denen anderer Speicherhierarchien vergleichen zu können. Die Resultate des Benchmarks zum Messen von Latenzzeiten sind in Abbildung 4.2 abgebildet. Es sind hauptsächlich drei verschiedene Latenzzeiten erkennbar. Für kleine Speicherblöcke bis zu 8 kB passen alle Daten in den L1 Cache, der eine Latenzzeit von 3,4 ns hat (übrigens: Licht legt im Vakuum in dieser Zeit eine Strecke von etwa 1 m zurück).

Abbildung 4.2: Speicherlatenzzeiten auf einem 600 MHz Alpha 21164 Prozessor in einer Cray T3E bei aufeinanderfolgenden Ladeoperationen. Die Schrittweite zwischen zwei Ladeoperationen variiert von Kurve zu Kurve.

Für Speichergrößen zwischen 8 und 96 kB sind die Daten im L2 Cache zwischengespeichert, der eine Latenzzeit von 13,4 ns hat. Speicherblöcke, die mit einer Schrittweite von 8 oder 16 Bytes durchlaufen werden, haben im Durchschnitt kürzere Latenzzeiten, weil ein Teil der Speicherzugriffe aus dem L1 Cache beantwortet werden kann. Bei Speicherzugriffen in 8 Byte Schritten kann jeder vierte Speicherzugriff *nicht* vom L1 Cache erfüllt werden (durchschnittliche Latenzzeit ist (3 L1-Latenzzeit + 1 L2-Latenzzeit) / 4). Bei einer Schrittweite von 16 Bytes kann jeder zweite Speicherzugriff nicht vom L1 Cache erledigt werden (durchschnittliche Latenzzeit ist (1 L1-Latenzzeit + 1 L2-Latenzzeit) / 2). Daraus kann man folgern, daß der L1 Cache Cache-Zeilen mit 32 Bytes hat, da bei 16 Byte Schritten, jedoch nicht mehr bei 32 Byte Schritten, noch ein Teil der Ladeoperationen vom L1 Cache beantwortet werden können.

Im Bereich zwischen 100 kB und 10 MB der Abbildung 4.2 kann man die Latenzzeiten des Hauptspeichers (320 ns) ablesen. Wie schon beim L2 Cache können auch beim Hauptspeicher bei kleiner Schrittgröße noch einige Anfragen vom L1 oder L2 Cache beantwortet werden. Entsprechend läßt sich folgern, daß der L2 Cache eine Blockgröße von 64 Bytes hat, weil dies die erste Schrittweite ist, bei der jeder Zugriff zu einem Cache-Miss im L1 und L2 Cache führt.

Speicher-

Allgemein steigt beim Erreichen der Kapazitätsgrenze eines Caches (Ln Cache) und Wechsel der dem Wechsel in den nächsten Cache (Ln+1 Cache) die Latenzzeit nicht direkt auf die Latenzzeit des Ln+1 Caches an, sondern nähert sich dieser langsam. Dies liegt daran, ebene daß der durchlaufene Speicherblock beim Übergang Größen erreicht, bei denen bei einem Durchlaufen des Blocks der Ln Cache nicht komplett überschrieben wird. Dadurch beantwortet der Ln Cache bei einem weiteren Durchlaufen des Speicherblocks noch einen Teil der Speicherzugriffe mit seiner Latenzzeit.

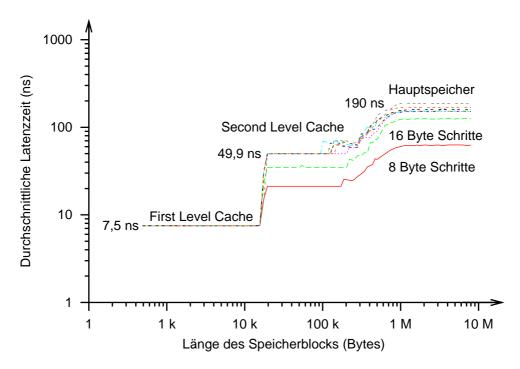

#### Speicherlatenzzeiten eines Pentium II Prozessors

Abbildung 4.3 zeigt die Ergebnisse des Benchmarks zum Messen von Speicherlatenzzeiten für einen Intel Pentium II Prozessor. An dem Diagramm läßt sich ablesen, daß die Latenzzeit des L1 Cache 7,5 ns, die des L2 Cache 49,9 ns und die des Hauptspeichers maximal 190 ns beträgt. Außerdem zeigt die Abbildung, daß der L1 Cache eine Größe von 16 kB und der L2 Cache eine Größe von 256 kB hat. L1 und L2 Cache haben die gleiche Blockgröße von je 32 Bytes.

Im Gegensatz zu einem Alpha 21164 in einer Cray T3E sind die Latenzzeiten für einen Pentium II Prozessor für den L1 und L2 Cache größer, die Anbindung zum Hauptspeicher ist aber mit geringeren Latenzzeiten verbunden, wie Abbildung 4.3 zeigt. Kleine Abweichungen beim Wechsel zum L2 Caches werden dadurch hervorgerufen, daß es beim Pentium II zwar für Programmcodes und Daten getrennte L1 Caches gibt, der L2 Cache aber für das Zwischenspeichern von Programm und Daten genutzt wird. Das Zwischenspeichern des Programmcodes verhindert also die optimale Nutzung des L2 Caches.

Im Bereich des Hauptspeichers entstehen mehr Abweichungen als erwartet, weil die Latenzzeiten der Speicherchips je nach Zugriffsmuster variieren können (WINDECK, 2000). Speicher sind so gebaut, daß sie Zugriffe auf nahe beieinander liegende Adressen schnell bearbeiten können. Bei weiter auseinanderliegenden Adressen muß speicherintern auf andere Bereiche umgeschaltet werden, so daß Schalt- und Latenzzeiten ansteigen. Außerdem muß der Inhalt der Speicher regelmäßig aufgefrischt werden. Wie oft dies geschieht hängt von den Speicherbausteinen ab. Üblich sind Auffrischungen (Refreshrate) im Abstand von 64 ms bei dynamischen Speichern (WINDECK, 2000).

#### 4.5 Speicherbandbreiten

STRICKER und GROSS (1995) beschreiben ein Modell zur Abschätzung von Speicherbandbreiten mittels ihrer "Extended Copy Transfer Characterization". Um ihr Modell zu überprüfen, haben sie einen Microbenchmark geschrieben, mit dem man Speicherbandbreiten messen kann. Genauso wie beim Messen von Speicherlatenzzeiten benutzen sie

Abbildung 4.3: Speicherlatenzzeiten eines Pentium II Prozessors mit 400 MHz bei aufeinanderfolgenden Ladeoperationen. Die Schrittweite zwischen zwei Ladeoperationen variiert von Kurve zu Kurve.

einen Speicherbereich, dessen Größe variiert wird, und laden Daten mit unterschiedlicher Schrittweite. Im Unterschied zum Messen von Speicherlatenzzeiten sind die Ladeoperationen voneinander unabhängig und nicht streng sequentiell, so daß der Prozessor mehrere Ladeoperationen in schneller Folge ausführen kann. Dieser Benchmark kann auch für das Messen der Bandbreite nicht lokaler Speicherzugriffe genutzt werden, wie STRICKER und GROSS (1997) zeigen.

#### 4.6 Speicheroperationen im Verhältnis zu Rechenoperationen: Horner-Schema

Bei einer Analyse verschiedener Verhältnisse von Speicheroperationen zu Rechenoperationen erhält man Daten darüber, unter welchen Bedingungen ein Prozessor mit hoher Leistung rechnen kann. Durch diese Daten kann bestimmt werden, wieviele Rechenoperationen ein Prozessor auf den in Registern vorhandenen Daten durchführen muß, ehe er auf angeforderte, externe Daten zugreift, wenn man möglichst nahe an die Leistungsgrenze des Prozessors kommen möchte. Werden zu häufig Daten angefordert, können die Speicher diese nicht mehr mit der nötigen Geschwindigkeit liefern.

Um diese Eigenschaft zu analysieren, eignet sich das Horner-Schema (HORNER, 1819) zum Auswerten von Polynomen. Das im folgenden beschriebene Verfahren wurde auch vom PARKBENCH Comittee eingesetzt (HOCKNEY und BERRY, 1993, Seite 22). Mit diesem Schema läßt sich die Anzahl der Rechenoperationen im Verhältnis zu den zu ladenden Daten sehr einfach variieren. Die einzigen benötigten Operationen sind Laden, Speichern, Addieren und Multiplizieren.

Horner-Schema Nach dem Horner-Schema wird der Wert eines Polynoms an einer Stelle x folgendermaßen berechnet:

$$\sum_{i=0}^n a_i x^i = \left( \left( \dots \left( (a_n) x + a_{n-1} \right) \dots \right) x + a_1 \right) x + a_0$$

In einem Microbenchmark nach dem Horner-Schema wertet man ein Polynom in einer Schleife an verschiedenen Stellen aus. Es lassen sich die Anzahl der Auswertungsstellen und der Grad des Polynoms (die Anzahl der benötigten Koeffizienten und damit der Rechenaufwand pro geladenen Daten) variieren. Dadurch bekommt man einen Überblick über die Charakteristik der Speicheranbindung des Prozessors.

Die Parameter bedeuten im einzelnen:

\_h

| -h         |                    | Eine Beschreibung der Aufrufstruktur wird als Hilfe ausgegeben.                                                                                                                      |

|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>-</b>   | max_length         | Die maximale Anzahl der Auswertungsstellen (Voreinstellung 1.048.576 = 1024 <sup>2</sup> ).                                                                                          |

| -d         | max_degree         | Der maximale Grad des Polynoms, das ausgewertet werden soll (Voreinstellung 18, implementationsbedingt höchstens 40).                                                                |

| -m         | {muladd, mul, add} | Die Art der Operation, die benutzt wird. Entweder eine muladd Operation, oder nur add oder nur mul Operationen (Voreinstellung muladd).                                              |

| <b>-</b> s | {memory, register} | Bei memory werden die Resultate der Auswertung in einen Vektor im Speicher geschrieben, bei register werden die Resultate an eine feste Adresse geschrieben (Voreinstellung memory). |

Abbildung 4.4: Die Handbuchseite des Horner-Schema-Benchmarks zeigt, daß mit dem Benchmark auch die benutzten Operationen modifiziert werden können, um beispielsweise die Geschwindigkeit von Multiplikation und Addition zu vergleichen. Mathematisch berechnen diese Varianten etwas anderes als eine Auswertung eines Polynoms nach dem Horner-Schema.

Der Horner-Schema-Benchmark, der in der Benchmarksammlung PARKBENCH in Fortran implementiert ist, wurde im Rahmen dieser Arbeit in ANSI-C reimplementiert und flexibler gestaltet. Die Aufrufsyntax und Variationsmöglichkeiten der Reimplementation zeigt die Handbuchseite in Abbildung 4.4. Bei der Implementation wurde darauf geachtet, daß ein Compiler für jeden Polynomgrad optimalen Code erzeugen kann. Um dies zu erreichen, wurde für jeden Grad eine Funktion mit fester Anzahl von Schleifendurchläufen generiert, so daß der Compiler diese Schleifen komplett ausrollen kann, damit weniger Verwaltungskosten für Schleifen entstehen und die Register optimal genutzt werden können.

#### Alpha 21164 Prozessor mit 600 MHz

Die in Abbildung 4.5 dargestellen Resultate des Horner-Schema-Benchmarks für einen Alpha 21164 lassen sich wie folgt interpretieren. Bei niedrigen Graden des Polynoms (2–6) und wenig Auswertungsstellen (1–50) wird wenig gerechnet, und es entsteht ein hoher Verwaltungsaufwand für die Schleifen, die oft durchlaufen werden, damit die Meßzeit ausreichend lang ist. Bei einer mittleren Anzahl von Auswertungsstellen (50–10000) und niedrigem Polynomgrad bleiben die Koeffizienten des Polynoms in Registern, und nur die Daten für die Auswertungsstellen müssen geladen werden, so daß der Speicherbus zum Engpaß wird. Je höher der Grad des Polynoms wird, desto mehr wird mit der auszuwertenden Stelle ohne weitere Speicheroperationen gerechnet, und um so besser wird die Leistung, weil die Wartezeiten durch Rechenoperationen überbrückt werden können. Bei Graden von 6–10 bleibt die Leistung relativ konstant, weil der Prozessor nicht mehr ohne dabei zu rechnen auf Daten vom Speicher warten muß und so seine Höchstleistung erreicht. Steigt der Grad des Polynoms noch weiter, sinkt die Leistung wieder ab, weil nicht mehr alle Koeffizienten des Polynoms in Registern des Prozessors gehalten werden können. Dies macht sich mit wachsendem Polynomgrad immer deutlicher bemerkbar.

Abbildung 4.5: Die Ergebnisse des Horner-Schema-Benchmarks für einen 600 MHz Alpha 21164 in einer Cray T3E zeigen, daß das Verhältnis von Lade- zu Rechenoperationen starken Einfluß auf die erreichbare Leistung hat.

Bei einer großen Anzahl von Auswertungsstellen (mehr als 10000) können diese nicht mehr im L1 Cache untergebracht werden, und die Latenzzeiten zum Laden der benötigten Daten steigt, so daß der Prozessor nicht mehr bis zur Höchstleistung ausgelastet wird.

An die theoretische Höchstleistung von 1200 MFlop/s kommt man mit diesem Microbenchmark mit im besten Fall 1161 MFlop/s bei Polynomgrad 11 und 2048 Auswertungsstellen

sehr nahe heran. Dafür lief der Prozeß auf einem einzelnen Knoten auf einer Cray T3E und wurde nicht vom Betriebssystem unterbrochen, so daß die Caches nur von diesem Prozeß genutzt wurden.

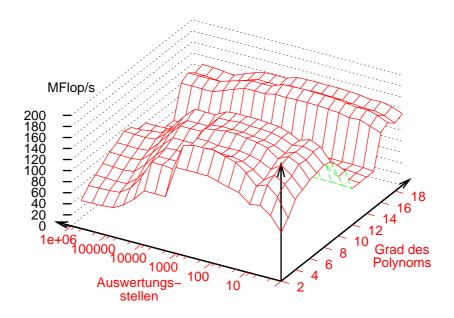

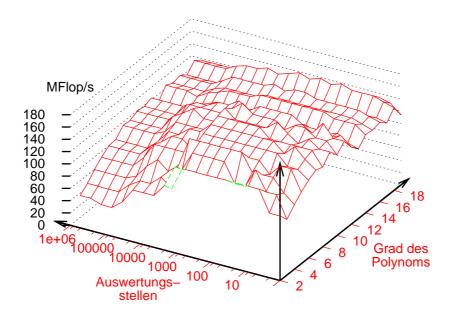

#### Pentium II mit 400 MHz

Bei einem Pentium II System unter Linux bemerkt man die Bedeutung eines guten Compilers, der effizienten Code erzeugt. Die Abbildungen 4.6 und 4.7 zeigen die Ergebnisse, die mit zwei verschiedenen Compilern in der gleichen Testumgebung gemessen wurden. Durch die relativ geringe Registeranzahl (8 Register für Gleitkommazahlen im Gegensatz zu 32 entsprechenden Registern im Alpha 21164 und höhere Latenzzeiten für den L1 Cache) ist es für die Compiler schwierig, die Leistung optimal zu nutzen.

Abbildung 4.6: Auf einem Pentium II mit 400 MHz liefert eine Messung mit der Evaluierungsversion des Fujitsu C-Compilers unter Linux beim Horner-Schema-Benchmark diese Charakteristik.

Beim Fujitsu C-Compiler gibt es einen großen Leistungseinbruch bei Polynomen mit Graden zwischen 12 und 15. Dies läßt sich ohne Kenntnis interner Compilerdetails nur schwer begründen, könnte aber daran liegen, daß eine Optimierungsstufe, die für kleinere Grade funktioniert hat, nicht mehr anwendbar ist und eine andere, die für Grade ab 16 optimieren kann, noch nicht einsetzbar ist. Davon abgesehen zeigt sich ein mit dem Alpha 21164 grundsätzlich vergleichbares Bild. Die theoretische Höchstleistung von 400 MFlop/s wird allerdings nicht annähernd erreicht (Maximum 190 MFlop/s bei Polynomgrad 3 und 128 bis 512 Auswertungsstellen). Dies liegt an der sehr geringen Registeranzahl, wodurch häufig auf den Speicher zugegriffen werden muß. Die relativ schlechte Speicheranbindung des L1 und L2 Caches in PCs kann diese Speicherzugriffe nicht mit der nötigen Geschwindigkeit abarbeiten, so daß der Prozessor oft auf Daten warten muß.

Abbildung 4.7: Die Messungen mit der GCC 2.95.2 für Linux auf einem Pentium II mit 400 MHz ergeben ein nicht ganz gleichmäßiges Diagramm für den Horner-Schema-Benchmark. Daran läßt sich erkennen, daß die optimale Nutzung der wenigen Register der IA-32 Architektur schwierig ist.

Bei der GNU Compiler Collection (GCC) wird die maximale Leistung bei Polynomgrad 10 und 512 Auswertungsstellen mit 174 MFlop/s erreicht. Auch wenn mit der GCC nicht die Leistung erreicht wird, die der Fujitsu C-Compiler maximal liefert, ist das Leistungsbild wesentlich gleichmäßiger, was dem Programmierer erleichtert, diese Systemleistung effektiv für seine Applikation zu nutzen. Daß die maximale Leistung bei einem im Verhältnis zur Registeranzahl hohen Polynomgrad auftritt, überrascht, wird aber durch die relativ ähnlichen Leistungswerte in der Umgebung relativiert und könnte auf Einflüsse des Betriebssystems während der Messung zurückzuführen sein.

Diese zwei Beispiele (Alpha 21164 und Pentium II) zeigen, daß eine sinnvoll gestaltete Speicherhierarchie für eine gute Auslastung des Prozessors wichtig ist. Beide Prozessoren benutzen zwei Zwischenspeicher, und obwohl der Hauptspeicher des Alpha 21164 längere Latenzzeiten hat als der des Pentium II, kann man die Leistung des Alpha 21164, weil er mehr Register hat und der L1 Cache schneller ist als der des Pentium II, besser nutzen.

# Simulation von Speicherhierarchien

A good simulation, be it a religious myth or scientific theory, gives us a sense of mastery over experience.

- HEINZ R. PAGELS (1939 - 1988)

Simulatoren für Speicherhierarchien dienen der Analyse und Optimierung von Speicherhierarchien. Unterschiedliche Verfahren zur Realisierung von solchen Simulatoren wurden mit der Zeit entwickelt und werden in diesem Kapitel beschrieben. Verschiedene Techniken der Instrumentierung werden präsentiert und ihre Vor- und Nachteile betrachtet. Abschließend werden einige Simulatoren für Speicherhierarchien vorgestellt, um einen Einblick in die unterschiedlichen Möglichkeiten zu geben.

#### 5.1 Zweck und Arten von Simulatoren für Speicherhierarchien

Eine gute Nutzung einer Speicherhierarchie eines Prozessors ist sehr wichtig, um die Rechenleistung eines Prozessors so gut wie möglich auszunutzen, wie bereits die Untersuchung des Horner-Schema-Benchmarks in Kapitel 4 ab Seite 21 gezeigt hat. Mit einem Simulator für Speicherhierarchien kann man Speicherzugriffe auf die verschiedenen Speicherebenen analysieren und versuchen, Speicherzugriffsmuster einer Anwendung zu optimieren. Außerdem werden Simulatoren von Speicherhierarchien dazu eingesetzt, Speicherhierarchien für Prozessoren zu optimieren und Kosten-Nutzen-Abschätzungen durchzuführen. Dabei werden Beispielapplikationen mit verschiedenen Speicherhierarchien simuliert und die Ausnutzung der Zwischenspeicher (Verhältnis von Cache-Hits zu Cache-Misses) berechnet.

Die Ansteuerung von Simulatoren von Speicherhierarchien können im wesentlichen auf zwei verschiedene Arten durchgeführt werden. Dementsprechend unterscheidet man zwei Arten von Simulatoren:

Trace Driven: Bei einem durch ein Laufprotokoll gesteuerten Cachesimulator (Trace Driven) wird eine Anwendung so modifiziert, daß sie alle nötigen Daten, die der Cachesimulator benötigt, während der Ausführungszeit speichert (Laufprotokoll, Trace). Der Simulator analysiert dann nach dem Programmlauf die aufgezeichneten Daten. Die gespeicherten Daten können eventuell auch mehrmals mit verschiedenen Einstellungen analysiert werden, solange sie auch für diese Einstellungen gültig sind.

**Execution Driven:** Bei einem ausführungsgesteuerten Simulator (Execution Driven) wird ein Programm so modifiziert, daß es Routinen des Cachesimulators aufruft, während es läuft. Für diese Cachesimulatoren wird kein Laufprotokoll benötigt.

#### 5.2 Instrumentierung von Programmen

Unabhängig von der Art des Simulators muß das zu simulierende Programm so modifiziert werden, daß es die nötigen Eingaben für den Simulator liefert (entweder in Form von gespeicherten Daten oder in Form von Funktionsaufrufen). Diese Modifikation nennt man Instrumentierung.

Bei protokollgesteuerten Simulatoren ist das Ziel der Instrumentierung, daß das Programm ein Protokoll erzeugt, das dann vom Simulator gelesen werden kann. Bei ausführungsgesteuerten Simulatoren wird durch die Instrumentierung das Programm so modifiziert, daß an allen nötigen Stellen Routinen des Simulators aufgerufen werden.

Unabhängig von der Ansteuerung des Simulators sind zwei verschiedene Arten der Instrumentierung üblich: entweder wird ein ausführbares Programm oder der Quelltext eines Programms instrumentiert.

#### Instrumentierung des ausführbaren Programms

Für die Instrumentierung von ausführbaren Programmen gibt es Bibliotheken, wie die "Executable Editing Library" (EEL) von LARUS und SCHNARR (1995), die eine Vielzahl verschiedener Plattformen und Binärformate unterstützen. Die EEL ist eine in C++ geschriebene Bibliothek und benutzt ihrerseits die "Binary File Descriptor Library" (CHAMBERLAIN, 1991). Mit Hilfe der EEL läßt sich der Kontrollflußgraph eines ausführbaren Programms berechnen. Die Knoten dieses Graphen beschreiben Blöcke von sequentiell ausgeführten Codeteilen, die Kanten Sprunganweisungen für Funktionsaufrufe oder Schleifen. Mit der EEL können Programmfragmente an diese Kanten angebracht werden. Die EEL erzeugt dann aus dem modifizierten Kontrollflußgraphen ein neues, ausführbares Programm, das so arbeitet wie das Originalprogramm und zusätzlich bei einem Kontrollflußwechsel die vorher im Graphen angebrachten Programmfragmente (zum Beispiel einen Aufruf einer Simulatorfunktion) ausführt.

Die Portabilität ist bei einer Instrumentierung von ausführbaren Programmen nicht in dem Maße gegeben wie bei einer Instrumentierung des Quelltextes, da sich auf einer neuen Rechnerarchitektur der Instruktionssatz, die Registeranzahl, die Semantik von Instruktionen oder das Format der ausführbaren Dateien ändern können. Bei Nutzung einer Bibliothek wie der EEL ist diese für eine neue Architektur in jedem Fall anzupassen, wofür detaillierte Kenntnisse über die Maschineninstruktionen nötig sind.

Einfluß auf die Portabilität

#### Instrumentierung des Quelltextes

Eine Instrumentierung des Quelltextes setzt voraus, daß der Quelltext der zu untersuchenden Anwendung verfügbar ist. Allerdings ist eine Analyse durch einen Simulator für Speicherhierarchien zur Optimierung von Programmen nur sinnvoll, wenn man das Programm danach auch ändern kann, so daß diese Einschränkung selten Einfluß hat. Die Instrumentierung des Quelltextes kann entweder automatisch über ein Instrumentierungsprogramm erfolgen oder von Hand vorgenommen werden.

Eine Quelltextinstrumentierung von Hand ist zwar aufwendig, dafür aber auch wesentlich flexibler als eine automatische Instrumentierung, weil der Simulator ganz gezielt aufgerufen werden kann. Eine automatische Instrumentierung dagegen ist nicht so fehleranfällig, kann aber auch dazu führen, daß sich das Programm mit dem eingesetzten Compiler nicht mehr kompilieren läßt, weil durch die Instrumentierung Konstrukte erzeugt wurden, die der genutzte Compiler nicht übersetzen kann.

#### 5.3 Funktionsweise von Simulatoren für Speicherhierarchien

Es gibt viele Simulatoren für Speicherhierarchien, die sich zum Beispiel im Detaillierungsgrad der Simulation oder der simulierbaren Speicherhierarchien unterscheiden, unterschiedliche Informationen für die Berechnung benötigen und auch unterschiedliche Informationen produzieren.

Ein Simulator für Speicherhierarchien benötigt Informationen darüber, auf welche Speicheradressen ein Programm zugreift und ob diese Zugriffe lesend oder schreibend sind. Diese Informationen stellen eine entsprechende Instrumentierung des Programms zur Verfügung. Außerdem benötigt ein Simulator für Speicherhierarchien zusätzlich Daten über den Aufbau der Speicherhierarchie, die simuliert werden soll.

Stehen diese Informationen zur Verfügung, vollzieht der Simulator die Zugriffe auf den Speicher nach und errechnet, in welcher Speicherebene die Daten zwischengespeichert werden, zählt Cache-Hits und Cache-Misses, zählt, wie häufig eine Cache-Zeile genutzt wurde, bevor sie wieder ersetzt wurde, summiert die Latenzzeiten, die mit Speicherzugriffen auf verschiedene Speicherebenen verbunden sind oder berechnet und sammelt andere Daten, die schließlich abgefragt werden können.

Ein Cachesimulator benötigt intern Datenstrukturen und Mechanismen, die die Verwaltung von Zwischenspeichern nachbilden. Mit Hilfe dieser Datenstrukturen wird festgestellt, welche Cache-Zeilen belegt und welche frei sind, welche als nächste zu ersetzen sind und welche Adressen in welchen Cache-Zeilen gespeichert sind. Die internen Datenstrukturen eines Cachesimulators hängen vom Detaillierungsgrad und der Flexibilität des Simulators ab.

Einige Simulatoren simulieren sehr detailliert das Verhalten des Prozessors oder der Auftragspuffer der Cache-Controller, um bessere Berechnungen der Ausführungszeit durchführen zu können. Je nachdem wie detailliert unterschiedliche Aspekte einer Speicherhierarchie simuliert werden, differieren auch die Daten, die für die Simulation benötigt werden und der Aufwand, den die Simulation verursacht.

## 5.4 Beispiele für Simulatoren von Speicherhierarchien

Bei der Entwicklung neuer Computer werden Simulatoren für Speicherhierarchien besonders häufig eingesetzt, um die Leistungsfähigkeit verschiedener Speicherhierarchien abschätzen zu können. Aber auch um den Einfluß neuer Architekturen von Zwischenspeichern auf verschiedene Programme zu analysieren, werden Simulatoren programmiert. In den folgenden Abschnitten sollen verschiedene Simulatoren für Speicherhierarchien exemplarisch vorgestellt werden.

#### **Der Active Memory Cachesimulator**