### University of Passau

# Delay Testing in Nanoscale Technology under Process Variations

Author:

Jie Jiang

Supervisor:

Prof. Dr. Ilia Polian Prof. Dr. Joan Figueras

A thesis submitted in partial fulfillment for the degree of Doctor of Computer Science

in the

Faculty of Computer Science and Mathematics

Department of Computer Engineering

# Declaration of Authorship

I, JIE JIANG, declare that this thesis titled, 'Delay Testing in Nanoscale Technology under Process Variations' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at the University of Passau.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at the University of Passau or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| Signed: |  |  |  |

|---------|--|--|--|

|         |  |  |  |

|         |  |  |  |

| Date:   |  |  |  |

"Learn from yesterday, live for today, hope for tomorrow. The important thing is not to stop questioning."

Albert Einstein

#### Abstract

In modern CMOS technology, process variations have significantly increased impact on the circuit behavior with continuously scaled transistor sizes. Manufactured devices tend to have different performances due to parameter variations during manufacturing and in the operating context. Conventional tests generated regardless of variations could fail to rule out devices with low performance and even functional failure caused by extreme variations; the unreliability in shipped products is in turn raised. To tackle the problem, many existing test approaches have focused on identifying and testing a number of critical paths in the circuit, and aimed at the efficiency of the searching process. However, the statistical circuit model, which better describes the circuit timing behavior under variations, is not yet sufficiently investigated and employed by existing testing methodologies.

This thesis work proposes Opt-KLPG and MIRID, which can be utilized by a statistical delay testing flow. Opt-KLPG—a K Longest Paths Generation (KLPG) algorithm for optimal solutions under memory constraints—can pin-pointedly generate tests for small delay defects, which are common small timing deviations under process variations, based on the traditional KLPG algorithm. In contrast to KLPG, Opt-KLPG guarantees the optimality of the solution (the K longest sensitizable paths indeed). MIRID is a mixed-mode timing-aware simulator, incorporating effects of power-supply noise and combining an event-driven logic simulation engine with interfaces to provided electrical models. MIRID aims at evaluating delay tests in presence of process variations efficiently yet accurately, by performing logic simulation at the gate level while determining the gate delays using simplified electrical modes. The electrical models applied by the simulator focus on the IR drop effect. Electrical parameters mainly contributing to the effect are incorporated into the model. The simulator is generic and flexible to be adapted by modifying the interfaces with minor effort. Both applications were verified in various aspects by experiments for academical/industrial circuits, and turned out to have satisfiable effectiveness and performance.

# Acknowledgements

Firstly, I would like to express the deepest appreciation to my advisor Prof. Dr. Ilia Polian for the continuous support of my Ph.D study and related research, for his patience, motivation and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my Ph.D study.

Besides my advisor, I would like to offer my special thanks to Prof. Dr. Joan Figueras to be the second supervisor of this thesis.

My sincere thanks also goes to my collaboration partners: Prof. Dr. Michel Renovell, Prof. Dr. Mariane Comte and Dr. Marina Aparicio Rodriguez from Montpellier; Prof. Dr. Bernd Becker, Dr. Matthias Sauer, Dr. Alexander Czutro from Freiburg; and Prof. Dr. Hans-Joachim Wunderlich, Michael E. Imhof and Abdullah Mumtaz from Stuttgart, not only for their precious collaboration but also for their insightful comments and encouragement.

Last but not the least, I would like to thank my family: my parents Yanfen Song and Ping Jiang, and my husband Yujiong Chen, for supporting me spiritually throughout writing this thesis and my life in general.

# Contents

| D  | eclar  | ation o      | f Authorship                                               | j    |

|----|--------|--------------|------------------------------------------------------------|------|

| A  | bstra  | ${f ct}$     |                                                            | iii  |

| A  | cknov  | wledge       | ments                                                      | iv   |

| Li | ist of | Figure       | es                                                         | viii |

| Li | ist of | Tables       |                                                            | х    |

| A  | bbrev  | viation      | S                                                          | xi   |

| 1  | Intr   | oducti       | on                                                         | 1    |

|    | 1.1    | Backgr       | round and State-of-the-art                                 | 2    |

|    |        | 1.1.1        | Process Variation in Nanoscale Technologies                |      |

|    |        | 1.1.2        | Delay Testing Under Process Variations                     |      |

|    |        |              | 1.1.2.1 Delay Fault Models                                 | 6    |

|    |        |              | 1.1.2.2 Timing Analysis                                    | 8    |

|    |        | 1.1.3        | State-of-the-art Approaches                                | 8    |

|    |        |              | 1.1.3.1 Statistical Design Approaches                      | 9    |

|    |        |              | 1.1.3.2 Statistical Testing Approaches                     | 10   |

|    | 1.2    | Statist      | ical Testing flow                                          | 11   |

|    |        | 1.2.1        | Overview of a Statistical Testing Flow                     | 11   |

|    |        | 1.2.2        | Statistical Fault Coverage                                 | 12   |

|    |        | 1.2.3        | SDD Tesing and KLPG Algorithm                              | 14   |

|    |        | 1.2.4        | Variation-aware Fault Simulation                           | 16   |

| 2  | KLI    | PG: <i>K</i> | Longtest Path Generation                                   | 19   |

|    | 2.1    | Motiva       |                                                            |      |

|    | 2.2    | Prelim       | inaries                                                    | 21   |

|    |        | 2.2.1        | Classification of Path Delay Faults                        |      |

|    |        | 2.2.2        | SAT-solver and SAT-based ATPG                              |      |

|    | 2.3    |              | 's KLPG Algorithm                                          | 25   |

|    | 2.4    | -            | LPG: K Longest Path Generation for Optimal Solutions Under |      |

|    |        |              | ry Constraints                                             |      |

|    |        | 2.4.1        | Algorithm Overview                                         |      |

|    |        | ソカウ          | Esperance Computation                                      | 30   |

*Contents* vi

|   |     | 2.4.3  | KLPG Module                                           | <br>. 35 |

|---|-----|--------|-------------------------------------------------------|----------|

|   |     | 2.4.4  | Sensitization check                                   |          |

|   |     |        | 2.4.4.1 Direct Implication                            |          |

|   |     |        | 2.4.4.2 ATPG using TIGUAN                             | . 42     |

|   | 2.5 | Applie | cation of Opt-KLPG by Variation-aware Fault Grading   | <br>. 45 |

|   |     | 2.5.1  | Modeling for Variation-aware Delay Testing            | <br>. 45 |

|   |     | 2.5.2  | Variation-aware Fault-grading Procedure               | <br>. 46 |

|   |     | 2.5.3  | Path-oriented Delay ATPG                              | <br>. 47 |

|   | 2.6 | Exper  | rimental Results                                      | <br>. 48 |

|   |     | 2.6.1  | On the Optimality of KLPG Algorithms                  | <br>. 48 |

|   |     | 2.6.2  | Fault-grading Procedure using Opt-KLPG                | <br>. 53 |

| 3 | MI  | RID: N | Mixed-mode IR Drop Induced Delay Simulator            | 56       |

|   | 3.1 | Motiv  | ration                                                | <br>. 56 |

|   |     | 3.1.1  | Mixed-mode Simulation                                 | <br>. 58 |

|   | 3.2 | Prelin | ninaries                                              |          |

|   |     | 3.2.1  | Power Distribution Network (PDN)                      | <br>. 59 |

|   |     | 3.2.2  | IR Drop Effect                                        |          |

|   |     | 3.2.3  | Power-aware Test                                      |          |

|   | 3.3 | Simula | ation Overview                                        |          |

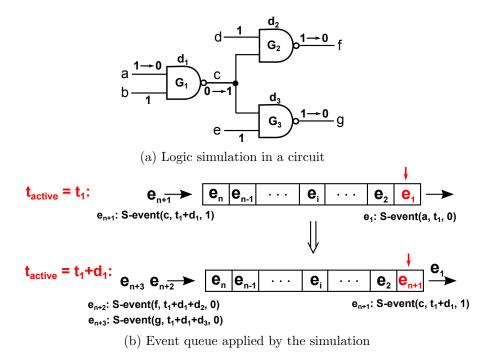

|   |     | 3.3.1  | Event-driven Logic Simulation                         |          |

|   |     | 3.3.2  | Interfaces to Electrical Models                       |          |

|   | 3.4 | Electr | rical Models                                          |          |

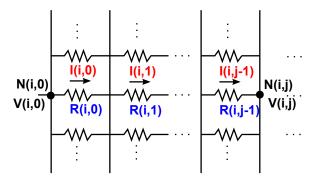

|   |     | 3.4.1  | PDN Configuration                                     |          |

|   |     |        | 3.4.1.1 Structural Assumption                         |          |

|   |     |        | 3.4.1.2 Parasitic Elements in PDN                     |          |

|   |     |        | 3.4.1.3 Mapping to the Logic Block                    |          |

|   |     | 3.4.2  | Current Distribution in PDN Grids                     |          |

|   |     | 3.4.3  | Electrical Models at the Gate Level                   |          |

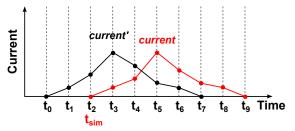

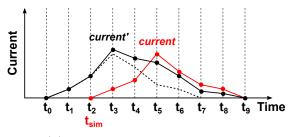

|   |     |        | 3.4.3.1 Dynamic Current Model                         |          |

|   |     |        | 3.4.3.2 Gate Delay Model                              |          |

|   | 3.5 |        | ator                                                  |          |

|   |     | 3.5.1  | Logic Library                                         |          |

|   |     | 3.5.2  | Simulation Preprocessing                              |          |

|   |     | 3.5.3  | Logic Simulation                                      |          |

|   |     |        | 3.5.3.1 Zero-delay Logic Simulation                   |          |

|   |     |        | 3.5.3.2 Timing-aware Event-driven Simulation          |          |

|   |     | 3.5.4  | Interface Functions For Electrical Models             |          |

|   |     |        | 3.5.4.1 Estimation of Dynamic Currents                |          |

|   |     |        | 3.5.4.2 Distribution of Currents in PDNs              |          |

|   |     |        | 3.5.4.3 Estimation of Gate Delays                     |          |

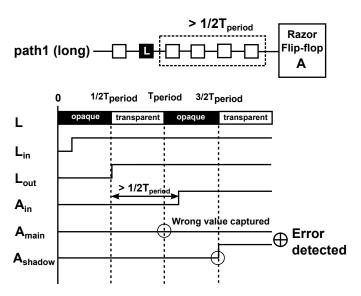

|   | 3.6 |        | cation to Self-adaptive Better-than-worst-case Design |          |

|   |     | 3.6.1  | Short-path Invalidation                               |          |

|   |     | 3.6.2  | Detection Conditions                                  |          |

|   |     |        | 3.6.2.1 Simplified Variability Model                  |          |

|   |     |        | 3.6.2.2 Mitigation by Buffer Padding                  |          |

|   |     |        | 3.6.2.3 Mitigation by Latch Placement                 | . 109    |

|            | ••   |

|------------|------|

| Contents   | V11  |

| Contective | V 11 |

|        | 3.6.3     | Strategies of Mitigation                                         | 112 |

|--------|-----------|------------------------------------------------------------------|-----|

| 3.7    | Experi    | mental Results                                                   | 113 |

|        | 3.7.1     | Accuracy Validation                                              | 113 |

|        | 3.7.2     | Investigation on IR Drop induced Delay                           | 120 |

|        | 3.7.3     | Performance for Large Circuits                                   | 123 |

|        | 3.7.4     | Mitigation of the Short-path Problem using Buffers and Latches . | 125 |

| 4 Co   | onclusior | 1                                                                | 128 |

| Biblio | ography   |                                                                  | 134 |

# List of Figures

| 1.1  | Overview of the variation classification                                    | 3  |

|------|-----------------------------------------------------------------------------|----|

| 1.2  | Overview of the statistical test flow [1]                                   | 11 |

| 2.1  | An example of the longest path                                              | 20 |

| 2.2  |                                                                             | 22 |

| 2.3  |                                                                             | 23 |

| 2.4  | Opt-KLPG overview                                                           | 28 |

| 2.5  | Path store initialization                                                   | 29 |

| 2.6  | PERT delays under different delay assignments                               | 30 |

| 2.7  | Computation of PERT delays for a signal driving a fan-out                   | 31 |

| 2.8  | Iterative computation of PERT delays                                        | 34 |

| 2.9  | KLPG module                                                                 | 36 |

| 2.10 | New Path submodule                                                          | 37 |

| 2.11 | KLPG flowchart                                                              | 38 |

| 2.12 | Examples of direct implication                                              | 40 |

| 2.13 | An example of sensitization check using direct implication                  | 40 |

| 2.14 | A false path that cannot be identified using direct implication             | 43 |

| 2.15 | An example of CMS@ derivation                                               | 44 |

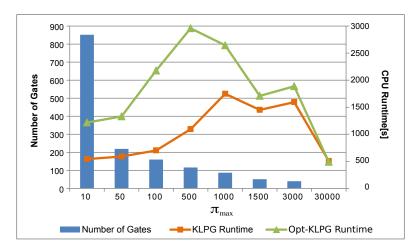

| 2.16 | Experimental results for circuit p35k. Runtimes are shown by lines; num-    |    |

|      | ber of gates with shorter paths are shown by bars                           | 53 |

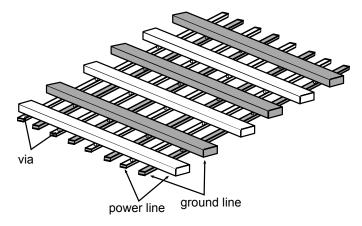

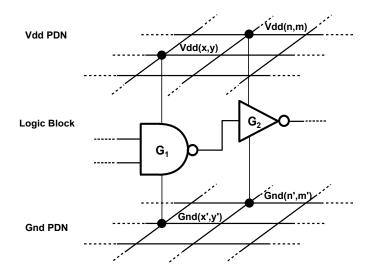

| 3.1  | A two-layer power distribution grid                                         | 60 |

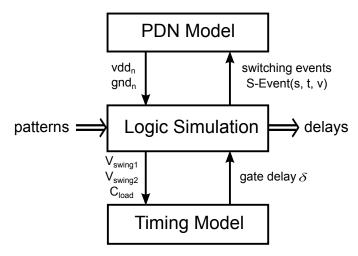

| 3.2  | Schematic illustration of the simulator                                     | 65 |

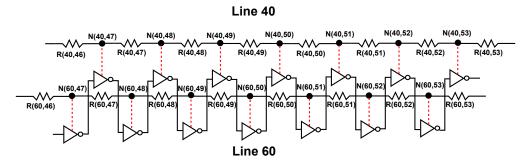

| 3.3  | Two sets of Vdd and Gnd lines                                               | 69 |

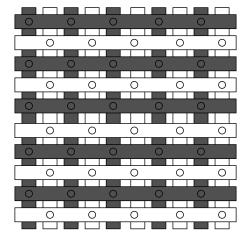

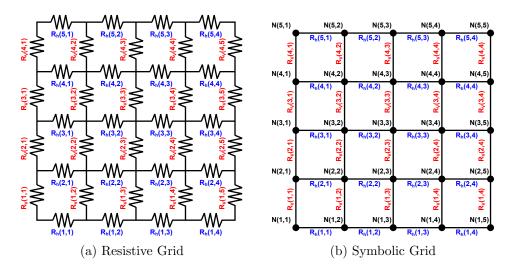

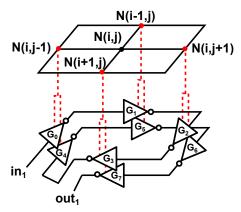

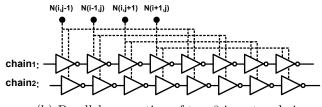

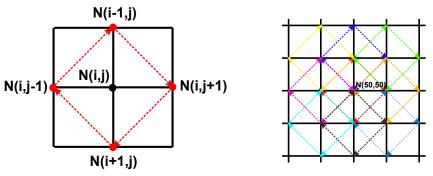

| 3.4  | PDN grids                                                                   | 70 |

| 3.5  | Gates connected to Vdd and Gnd power supply nodes                           | 72 |

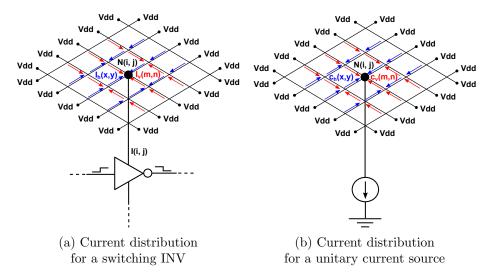

| 3.6  |                                                                             | 73 |

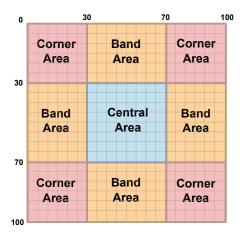

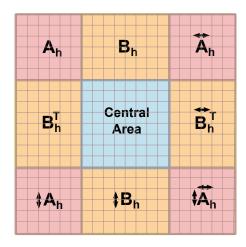

| 3.7  | Central, corner and band areas in a $100 \times 100$ grid                   | 74 |

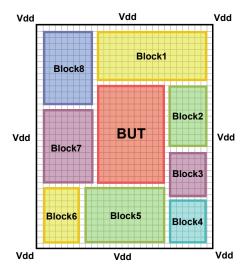

| 3.8  | A high-level view of the power grid over a chip with 9 blocks               | 75 |

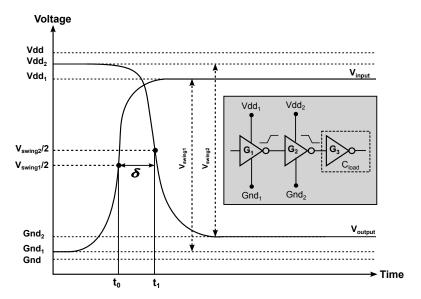

| 3.9  | Supply and input voltage swings and gate delay                              | 80 |

| 3.10 | Definition of the gate object                                               | 83 |

| 3.11 | Definition of the signal object                                             | 84 |

| 3.12 | Definition of the <i>pin</i> object                                         | 84 |

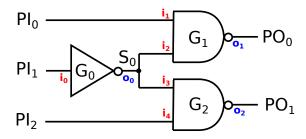

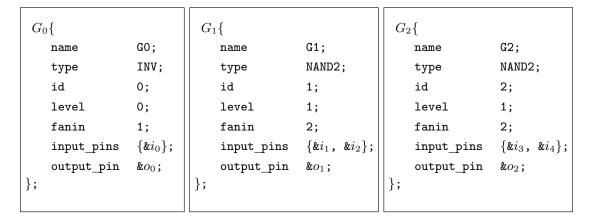

|      | A circuit containing an inverter and two NAND gates                         | 85 |

|      | Examples of constructed gate objects                                        | 85 |

|      | Examples of constructed signal and pin objects                              | 86 |

|      | Symbolic presentation of operations for matrices in different areas in PDN  | 88 |

|      | Symbolic presentation of operations for matrices in different areas in 1 DN |    |

List of Figures ix

| 3.18 | Calculation of voltage level at PDN node $N(i,j)$                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.19 | Update current array $current' \dots \dots$ |

| 3.20 | Short-path invalidation in Razor design                                                                                                           |

| 3.21 | Mitigation by latch placement                                                                                                                     |

| 3.22 | Input-to-latch invalidation                                                                                                                       |

| 3.23 | Strong latch-to-output invalidation                                                                                                               |

| 3.24 | Weak latch-to-output invalidation                                                                                                                 |

| 3.25 | 14-inverters model for validation                                                                                                                 |

| 3.26 | Current validation for 14-inverters chain                                                                                                         |

| 3.27 | Voltage validation for 14-inverters chain                                                                                                         |

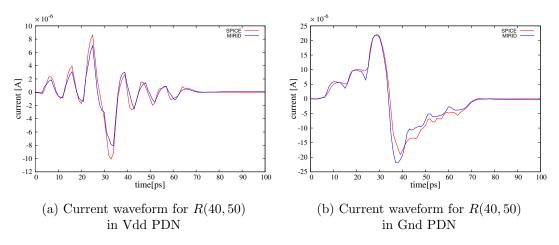

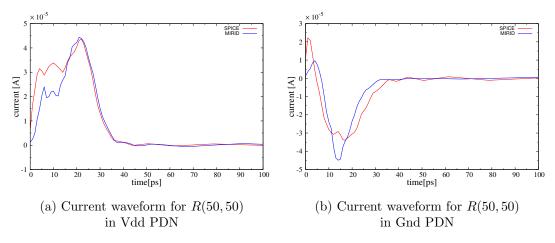

| 3.28 | Current validation for c17                                                                                                                        |

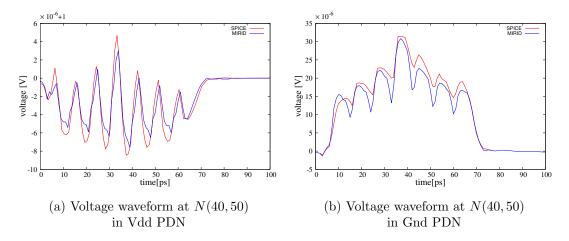

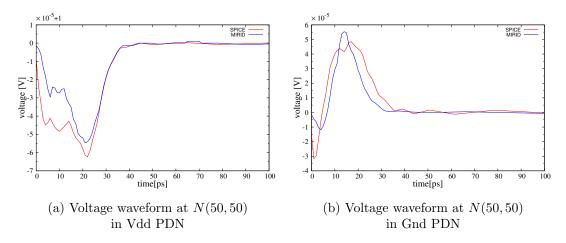

| 3.29 | Voltage validation for c17 $\dots \dots \dots$    |

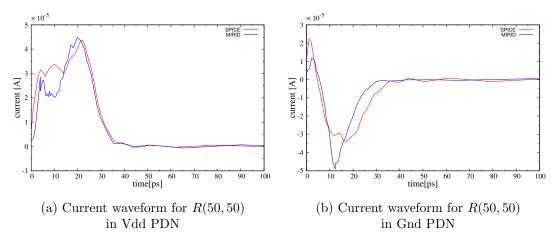

| 3.30 | Current validation for c17 with $10^{-1}$ ps precision                                                                                            |

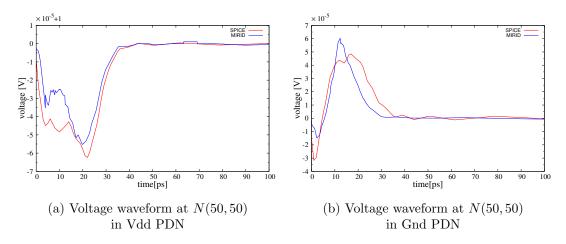

| 3.31 | Voltage validation for c17 with $10^{-1}$ ps precision                                                                                            |

| 3.32 | 8-inverter chains connected to a $2\times 2$ grid                                                                                                 |

| 3.33 | Model of 9 inverter chains                                                                                                                        |

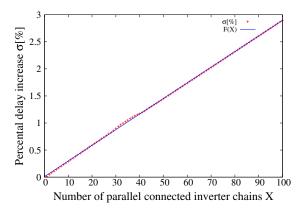

| 3 34 | Correlation of the IR drop induced delay and X                                                                                                    |

# List of Tables

| 2.1 | Experimental results under functional sensitization criterion                |

|-----|------------------------------------------------------------------------------|

| 2.2 | Comparison of KLPG and Opt-KLPG under different model assumptions            |

|     | for circuit c7552                                                            |

| 2.3 | Comparison of KLPG and Opt-KLPG under different model assumptions            |

|     | for industrial circuit p45k                                                  |

| 2.4 | Statistical fault coverages for 101 instances, 100 random faults and 9 fault |

|     | sizes                                                                        |

| 3.1 | Difference of currents in 14-inverter chain reported by MIRID and SPICE 116  |

| 3.2 | Difference of voltages in 14-inverter chain reported by MIRID and SPICE 117  |

| 3.3 | Difference of current and voltage at $N(50, 50)$ in c17 reported by MIRID    |

|     | and SPICE                                                                    |

| 3.4 | Simulation for ISCAS and NXP circuits                                        |

| 3.5 | Experimental results for buffer padding and latch placement                  |

# **Abbreviations**

ATPG Automatic Test Pattern Generation

VLSI Very-Large-Scale Integration

CMOS Complementary Metal Oxide Semiconductor

$\mathbf{VDSM} \ \mathbf{Very} \ \mathbf{Deep} \ \mathbf{Sub\text{-}Micron}$

$\mathbf{CUT} \ \mathbf{C}\mathrm{ircuit} \ \mathbf{U}\mathrm{nder} \ \mathbf{T}\mathrm{est}$

SDD Small Delay Defect

IC Integrated Circuit

**TF** Transition Fault

PDF Path Delay Fault

KLPG K Longest Paths Generation

PDN Power Distribution Network

$\mathbf{MIRID}\ \mathbf{M}\mathrm{ixed}\text{-mode}\ \mathbf{IR}\text{-drop}\ \mathbf{Induced}\ \mathbf{D}\mathrm{elay}\ \mathrm{Simulator}$

BUT Block Under Test

SAT Boolean Satisfiability Problem

CNF Conjunctive Normal Form

MLR Multiple-Linear Regression

NRMSE Normalized Root Mean Square Error

IFA Inductive Fault Aanlysis

### Chapter 1

# Introduction

Reliability is a very important issue in Complementary Metal Oxide Semiconductor (CMOS) manufacturing. Devices delivered to customers should operate not only correctly as required by the specification, but also reliably during the whole life time and in all expected operation conditions. However, nothing is perfect—due to the intrinsic physical limitations of the fabrication process, the uncertainties in the parameters of fabricated devices and in the operating environment during the lifetime are not avoidable; the situation is even getting more severe as technology scales. These uncertainties contributes to the source of process variations—variations in parameters of transistors or interconnects—and in turn impair the performance of devices or even cause operation failures.

In today's semiconductor manufacturing technology, up to 30% variation in operating frequency and 5 to 10 times variation in leakage power are expected [3]. Due to the effect of variations, the behavior of the fabricated design in terms of performance and power differs from what designer intended; the unreliability in the design rises. Numerous solutions that require change in design methodologies, such as adaptive body bias [4], or self-adaptive technique to lower the rate of dynamic errors [5], have been proposed to combat the variations. In context of testing, the impact of variations is also significant. Traditionally, test for Integrated Circuit (IC) uses fault models that abstract from defect-specific parameters affecting the circuit behavior. However, in presence of process variations, defects can manifest themselves differently, especially in affecting circuit timing; tests targeting the abstracted fault could fail to detect these defects. The

increased impact of process variations could lower the defect coverage and in turn impair the reliability of the device under test. Though a number of testing approaches have been proposed and contributed to raise the defect coverage under process variations [6–12], a statistical testing flow, which involves fault modeling, fault simulation and test generation with consideration of process variations, has not been sufficiently investigated.

The motivation of this thesis work is to propose variation-aware Automatic Test Pattern Generation (ATPG) and simulation methodologies that could be integrated into the statistical testing flow. The objective is two-fold: on one hand, the methodologies have to be capable of dealing with benchmark/industrial circuits and thus efficiency is an important concern; on the other hand, to increase the defect coverage the impact of process variations need to be taken into account by the methodologies, which in turn requires the accuracy in estimating the impact. The remainder of this chapter is organized as follows: Section 1.1 introduces background knowledge and the state-of-the-art approaches; Section 1.2 presents a statistical testing flow with test methodologies that are especially of interest and could be employed by the flow.

#### 1.1 Background and State-of-the-art

#### 1.1.1 Process Variation in Nanoscale Technologies

The uncertainty in device parameters, which is called manufacturing-related variation, is caused by equipment imprecision and process limitations. As CMOS technology continues to scale, manufacturing process is getting more complex while process precision control needs to remain relatively accurate at the same time. As a result, a number of steps throughout the manufacturing process are prone to fluctuations [13], e. g., optical proximity effects (variations in the linewidth of a feature as a function of the proximity of other nearby features) can be caused by patterning features smaller than the wave length of light [14]. These manufacturing imperfections can result in variations in physical parameters of devices and interconnects, such as gate length, gate-oxide thickness, channel doping concentration, and the thickness and height of interconnects. Furthermore, variations in physical parameters cause variations in electrical characteristics of

devices and interconnects, such as the threshold voltage, the drive strength of transistors, and the resistance and capacitance of interconnects, which finally affect the circuit timing behavior. It is important to note that correlations can exist between electrical variations that depend on common physical parameters. Also, physical parameters can be correlated themselves under the impact of a particular equipment variation. Analysis to determine the variations and correlations in physical parameters is very complex and impractical due to the high number of equipment-related parameters. Hence, physical parameters are often assumed to be random variables that are independent or have well-understood correlations by statistical timing analysis (analysis that determines the timing behavior of circuit elements statistically) [13].

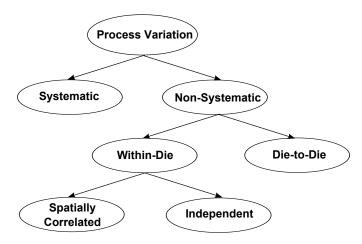

FIGURE 1.1: Overview of the variation classification

Manufacturing-related process variations can be further divided into two categories: systematic and non-systematic, as presented in Figure 1.1. Systematic variations are components of physical parameter variations that follow a well-understood behavior and can be predicted by analyzing the designed layout, e. g., the optimal proximity effects. Nonsystematic or random variations represent the truly uncertain component of physical parameter variations, such as line edge roughness and random dopant fluctuations. Nonsystematic variations can be further divided into groups of die-to-die and within-die variations according to their act on different spatial scales. In past technologies, it was sufficient to model die-to-die variations while in modern nanoscale technologies, within-die variations have become equally important [15]. Finally, within-die variations can be categorized into spatially correlated and independent variations. Many underlying processes tend to affect closely spaced devices in a similar manner, making these devices more likely to have similar characteristics than those placed far apart. The component

of variation that exhibits such a spatial dependence is known as spatially correlated variation. The residual variability of a device that is statistically independent from all other devices is referred to as independent variation. It has been observed that the contribution of independent within-die random variations is increasing with continued process scaling [13].

The other source of process variation is the uncertainty in the operating environment of a particular device during its lifetime, represented by variations related to the operating context, such as temperature, supply voltage and lifetime wear-out. These variations can depend on the functionality of individual circuit block and the applied input sequences. For example, the power density across a die varies for different rates of activities in a circuit block. Higher activity in a block puts more demand on the power distribution network, resulting in resistive and inductive voltage drops; the time-dependent supply voltage variation is in turn created. Moreover, the high rate of activities in a block raises the temperature in this area and creates the so-called hot spots, which in turn results in the temperature variation across the die. Also, aging has a significant impact on the transistor performance. Studies have shown that a transistor's saturation current degrades over years because of oxide wear-out and hot-carrier degradation effects [3]. This degradation is expected to become worse as the transistor size continues to shrink.

Unlike the dynamic sources of variations that exhibit themselves during the operating cycle, such as voltage supply and temperature, variations caused by manufacturing imperfections and aging mechanisms are static or quasi-static, that is, they could exhibit long time constants. With respect to the exhibited time constant, the sources of process variations can be briefly divided into two groups from the time aspect:

- Physical factors including variations in the electrical and physical parameters

characterizing the behavior of devices, mainly caused by manufacturing imperfections and various wear-out mechanisms. They exhibit long time constants,

typically measured in years.

- Environmental factors including power supply voltage and temperature. These factors highly depend on the design and are typically measured by time constants in similar scale to the clock frequency.

#### 1.1.2 Delay Testing Under Process Variations

The timing of Very Deep Sub-Micron (VDSM) devices is considerably affected by process variations. As reported in [16], defects that cause delay have typically represented 1% to 5% of the total defect population observed. Delay defects can cause delayed signal propagations exceeding the maximum operating frequency, i.e., the circuit fails to operate in time when these signal propagations are required. Under impact of process variations, which generally do not have fixed values and usually follow a probability distribution, delays induced by the variations will also follow a similar distribution and vary between different circuit instances.

To avoid the overall delay behavior of devices, raising the operation frequency is impractical because it contradicts the requirement for high performance. Typically, manufacturers will choose an operating frequency of the product to meet requirements from the customer and the market, as well as to make the economic trade-off between the yield loss below the operating frequency and the higher performance of the product. To screen the units that could operate slower than the desired frequency, the speed of the paths with the longest delays, called *critical paths*, are often tested under worst-case conditions.

The objective of tests is to rule out defective parts from manufacturing devices. which means, the tests should be designed such that by observing the responses from the Circuit Under Test (CUT) must lead to detection of the defects [17]. Classically, most delay testing techniques apply Boolean logic values to the CUT and observe its response at some clock frequency. Some delay defects, especially those resulting from process variation, can also be detected through analysis of the response of process monitors [18]. For the mostly used Boolean delay-defect testing, two major related questions can arise:

- What kind of test patterns should be applied?

- An what clock frequencies to apply the test patterns and at what clock frequencies to capture the output responses?

<sup>&</sup>lt;sup>1</sup>Process monitors are carefully designed special circuit structures monitoring manufacturing-process characteristics, such as ring oscillators and trees of NAND gates with controlled delays.

However, due to the fact that an extraordinary volume of defects can exhibit themselves in a circuit (and not all possible defects may be known), it is almost infeasible to derive appropriate tests for defects individually. A fault model that extracts the faulty behavior common in the target defects is therefor used, to facilitate analysis of defects and the derivation of tests. Targeting on the modeled faults, dedicated tests can be generated, with time information when to apply the test and when to observe the output.

#### 1.1.2.1 Delay Fault Models

Two fault models are often used by delay testing: the Transition Fault (TF) model and the Path Delay Fault (PDF) model [2]. Traditionally, the TF model is often used by the industry for delay testing. It assumes the delay caused by the defect to be larger than the specification time, which usually refers to the system clock period. Test generation for such a fault model takes advantage of the rather low number of faults, which is linear to the circuit size. Moreover, existing tools that test and simulate stuck-at faults—a very common and mostly used fault model—can be used with minor modifications to generate tests for TFs. However, the TF has significant limits. Under assumption of the defect size larger than the clock period, any path through the fault site can be selected to propagate the transition to the output. Indeed, ATPG tools, which are very often used by test generation, tend to seek the easiest path to excite the fault and propagate the fault effect. It implies that the selected path has relatively few gates and can be very short. Then, for defects with smaller sizes, that is, the extra delay caused by the defect is shorter than the clock period, propagation of the delay along such a short path is likely to finish during the clock period, resulting in the capture of a correct logic value at the output, i.e., the target defect escapes detection.

In fact, modern manufacturing process tends to produce defects inducing small delays. Many electrical phenomena in VDSM process technologies, such as process variations, crosstalk noise, power-supply noise, resistive shorts and opens, can induce small delay variations in the circuit components [19]. Such small delay variations are referred to as Small Delay Defect (SDD) [20, 21], which have received increased attentions over the last few decades. As reported in [22, 23], the distribution of delay-related failures is skewed toward the smaller delays. That is, small delay defects contribute to the failure

of the majority of devices that fail due to delay defects. Targeting these SDDs can lowers the test escape rate and thus improve the reliability of the shipped products.

Obviously the TF model, which assumes the delay exceeds system clock period, does not match the faulty behavior caused by a SDD properly. PDF is more preferred by testing SDDs as it assumes that a path propagates the desired transition with a total amount of time exceeding the specification time. The small delays could be detected by exercising some paths through them so that the total path propagation delay exceeds the clock period. Thus, searching for such paths are often required by testing small delays, i.e., paths through the defect site that most probably propagate the small delays to the observation point are searched, and sensitized by tests under certain sensitization conditions. The sensitization condition is often related to the timing variations of side-inputs—inputs that are not on the path and drive the on-path gates, which can affect the fault detection. To avoid such situations, tests that guarantee the detection of delay faults regardless of timing variation in the rest of the circuit, called robust tests, are targeted. Robust tests are very powerful because they detect the target fault independent of the presence of other delay faults. However, as indicated in [24], robust tests only exist for a relatively small part of delay faults in today's Very-Large-Scale Integration (VLSI) circuits. Thus, non-robust tests should also be targeted by the test generation and applied with robust tests to raise the defect coverages totally. It should be noted that PDF is the fault model that can be used for testing SDD; where and how the delays are distributed on the path are not concerned by the model itself while a SDD is related to a specific defect site. The PDF model takes advantage of the scalability of delay sizes of detectable defects. Nonetheless, for VLSI circuits the test generation using PDF model could be very time-consuming since the number of paths is normally very large and even exponential to the circuit size in worst case.

Tests that detect a PDF need to launch the desired transition—assignments of opposite logic values in two consecutive clock cycles—at the input of the path, and propagate the transition through the path to its output. Furthermore, the propagation of the transition to the output implies a necessary condition that the output value settles in a logic value opposite to its initial value. Depending on sensitization condition for the test, such as a robust or non-robust test, more value constrains for signals, especially the side-inputs, need to be considered by the test generation. Moreover, a large part of the PDFs can be functionally redundant, i.e., no tests exist that propagate the transition along the

path. For example, it has been shown that up to 81% PDFs in ISCAS'85 circuits are functional redundant [25]. Thus, an efficient identification of redundant PDFs could help to improve the performance of test generation significantly.

#### 1.1.2.2 Timing Analysis

Timing analysis that characterizes the timing behavior of circuit elements is very important for an accurate delay estimation required by timing-aware testing methodologies. It is performed during the design flow and can be static or dynamic. Static Timing Analysis checks static delay requirements of the circuit independent of input vectors whereas dynamic timing analysis verifies the functionality of the design without any timing violations for applied input vectors by simulating using timing information [13, 26].

In the past few decades, static timing analysis has been a widely adopted tool in the VLSI design and served as the timing engine in test generation, mainly because of its efficiency and conservatism in the sense that it takes the worst-case into account. However, static timing analysis is deterministic and calculates the circuit delay for a specific process condition, i.e., all parameters that affect the circuit timing are assumed to be fixed and are uniformly applied to all the devices in the design [13]. As process variations have become significantly more pronounced in nanoscale regime, the conventional characterization of circuit elements with fixed delays becomes inappropriate to be used. A statistical timing assignment [13, 26, 27] is preferred since process variations and their influences in circuit timing are statistically distributed in nature.

The need for an effective modeling of process variations in circuit timing has led to a number of statistical approaches, such as numerical integration over the process-parameter space to compute the delay of critical paths [28], path-based statistical timing analysis considering spatial correlations [27], and statistical dynamic timing analysis to effectively identify false paths [26].

#### 1.1.3 State-of-the-art Approaches

Variability in circuit parameters has become a very important concern from both design and test sides as technology scales into the nano-regime. Designing for the worst-case conditions is unrealistic as it would contradict the performance requirement, and lead

to excessive area and power consumption. Thus, design approaches are often based on statistical timing assumptions, and aim at mitigating the effects of variability. However, even with the most sophisticated approaches, the electrical models employed are incapable of exactly representing the device performance, which means that there is always the possibility of variations being outside model predictions [17]. The reason is that causes of variability could be very sophisticated and depend on manufacturing technologies; and even if the causes are well understood, predicting the results of variations on devices is a serious challenge. Moreover, as variation has a continuous distribution, situations are inevitable that parameter variations will produce a small difference in specifications, among which circuit delay is particularly interested, from allowable extremes [17]. In brief, variation effects cannot be exactly predicted by design models and totally compensated. Moreover, delay variations in devices that could lead to malfunctions are inevitable. Test methodologies are therefore required by high-quality manufacturing, to rule out such devices that could present delay defects under process variations. In this section, the state-of-the-art approaches are briefly reviewed, in both the design (1.1.3.1) and the test areas (1.1.3.2).

#### 1.1.3.1 Statistical Design Approaches

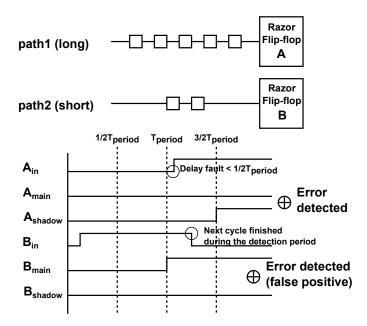

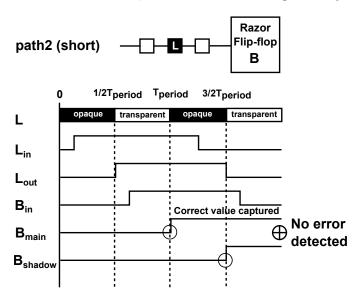

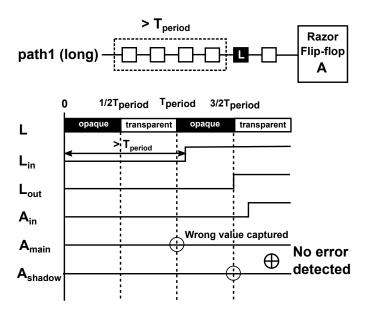

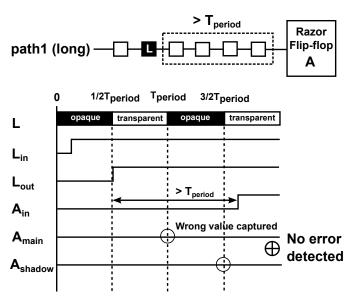

Numerous works have been contributed to the statistical-based design that considers the impact of process variations, both at the gate level [29] or at a high level [30]. Moreover, a number of techniques have been used to mitigate the impact of process variations in modern technologies [31]. The impact of process variations can be reduced by tuning certain operating parameters, such as the threshold voltage ("body bias"), the supply voltage and the frequency. Based on methods that adjust these parameters, self-calibration designs are proposed to compensate and correct the performance deviations induced by process variations adaptively [4, 32, 33]. Dynamic calibration during the operating process often requires additional hardwares (e. g., sensors), and mechanisms of fault detection and correction. For example, the RAZOR processor [5] scales the supply voltage dynamically during the process according to the computed error rate in terms of the frequency of the delayed transitions. For the purpose of monitoring and correcting errors, the processor applies extra memory elements clocked later than the system clock to capture the correct values that are possibly delayed. A similar fault-tolerant architecture that combines latch-based design and time redundancy is presented in [34].

Also, other circuit techniques for variability mitigation have emerged recently, such as clock-tuning in Intel Montecito processor [35], the adaptive and self-healing architecture ElastIC [36], and the variation-tolerant network design using self-calibrating links [37].

#### 1.1.3.2 Statistical Testing Approaches

Existing test approaches focus on identifying a number of testable critical paths for each possible fault site and generating tests that excite the transition propagated along the paths. These paths are commonly the longest testable ones given a static timing assignment, which implies, they have the minimum timing slack between the path propagation time and the operating frequency and thus most probably delay the propagated transitions under process variations. As the search space of paths for large circuits can be very huge, many approaches aim at the efficiency of the searching process, such as by pruning paths from the search space based on structural correlation [7, 38] and process-variation correlation [6]. Moreover, a number of approaches have explicitly considered process variations during test generation, usually based on statistical timing analysis that describes the timing behavior of circuit elements under process variations. In [8] an approach was proposed that intelligently selects n-detection test patterns (tests that detect each target fault at least n times) based on a gate-delay defect probability model. More sophisticated methods that employ a suitable defect-coverage metric were used to guide the test generation process. Park et al. were the first to propose the concept of statistical delay-fault coverage [9]. In [10] the impact of statistical variations including specific noise effects on circuit performance was analyzed, and further considered by a novel defect-driven path selection methodology for test generation. Shintani et al. introduced a metric called parametric fault coverage that was utilized to guide an adaptive test flow [11]. A process variation-aware test generation method targeting on resistive bridging faults was proposed in [12], which uses a metric called test robustness to quantify the impact of process variation on test quality.

#### 1.2 Statistical Testing flow

#### 1.2.1 Overview of a Statistical Testing Flow

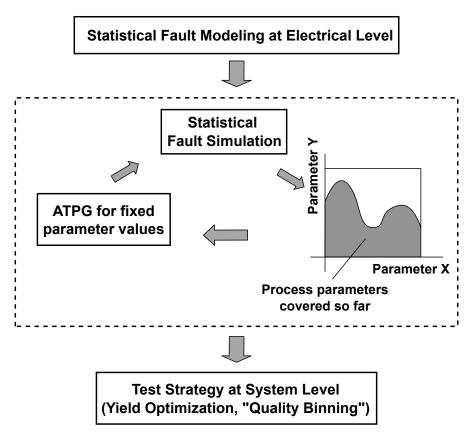

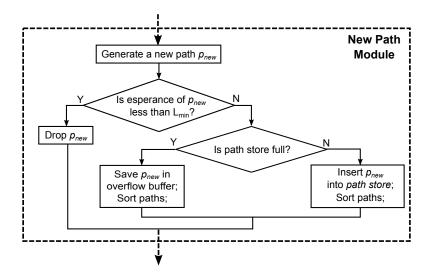

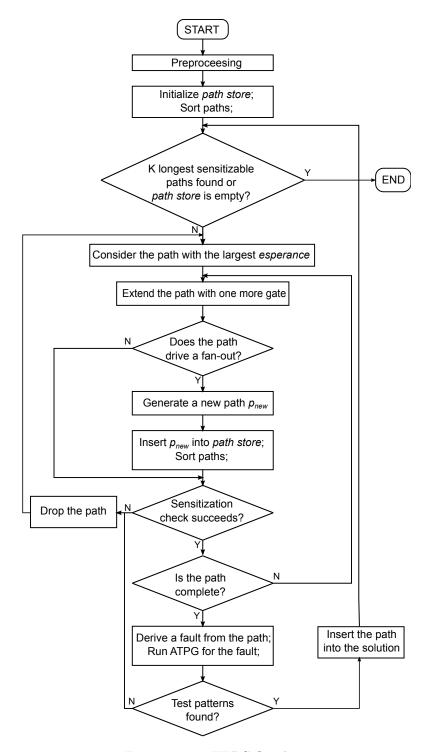

Though variability has been considered by many existing testing approaches, a testing flow based on statistical timing analysis, which involves fault modeling, fault simulation and test generation, has not yet been sufficiently investigated. The basic concept of a statistical test flow [1] is illustrated in Figure 1.2. The "statistical" concept can be adopted by approaches at various abstraction levels of the test flow, from the fault modeling at electrical level to test strategies at system level.

FIGURE 1.2: Overview of the statistical test flow [1]

The statistical fault modeling can be obtained by a systematic approach for a primitive cell library with injected defects [1]. In this approach electrical fault simulations with randomly changing circuit parameters were performed to achieve the delay distribution for injected defects, i.e., the statistical characterization of library cells in terms of the timing behavior for an injected defect approximated across all parameter variations.

Regarding the test flow at the gate level (bounded with dashed lines in Figure 1.2), due to the complexity of test generation, ATPG for fixed parameters values can be combined to the statistical fault simulation, to cover the whole parameter space incrementally. The fault coverage reported by the simulation should also be statistically defined, to evaluate the test quality under process variations and guide the iterative test flow.

#### 1.2.2 Statistical Fault Coverage

Classically the fault coverage FC is defined as in Equation 1.1.

$$FC := \#detected\ faults / \#modeled\ faults$$

(1.1)

Under the impact of process variations, the new metric of fault coverage should be defined based on the configuration of process parameters and the corresponding statistical fault modeling.

Provided with manufacturing data, a finite list of parameters that could have impact on the timing-behavior of circuit elements and the range of possible values for each parameter are modeled by  $\{P_1, P_2, \ldots, P_N\}$  and  $\Delta_i$   $(1 \leq i \leq N)$ , respectively. Due to the complexity of modeling possible correlations between process parameters, the parameters are assumed to be uncorrelated.

Given a circuit represented by a set of gates and interconnect lines between gates, a delay assignment for the circuit refers to the estimated propagation time for each gate, usually called gate delay. (The interconnect delay is not considered by this thesis work.) The gate delay can differ for different gate inputs and input edges. Thus, it can be modeled by the propagation time from a gate input to the output for a rising or falling transition. For each combination of parameter values  $p := (p_1, p_2, \dots, p_N) \in P$  where P is the parameter space  $(P := \Delta_1 \times \Delta_2 \times \dots \times \Delta_N)$ , the circuit exhibits the corresponding timing behavior, given by the delay assignment. A circuit instance that affected by a variation combination p is denoted by  $C_p$ . Moreover, assuming a normal or well-understood distribution of parameter variations, the probability density function of a possible combination of parameter values p can be derived, denoted by  $\pi(p)$ .

Then, given a delay fault f := (g, s) where gate g is the fault location and s is the delay size (that could refer to a gate input and the transition edge depending on the delay model), f is detected in  $C_p$  by a test set T if at least one test leads to an incorrect response in  $C_p$  at time point  $t_{obs}$ , where the correct response is given by the fault-free nominal circuit (in absence of variations) at time  $t_{obs}$ . The observation time  $t_{obs}$  is commonly chosen such that all circuit outputs have stabilized after the test pattern is applied. Considering process variations,  $t_{obs}$  equals to the maximal delay of the circuit in absence of variations, multiplied with a safety margin greater than 1. The detectability of f by T in circuit instance  $C_p$  is denoted by  $det_{C_p}(f,T)$  ( $det_{C_p}(f,T)$ ) equals to 1 if f is detected and 0 otherwise). Finally, using  $\pi_p$  to denote the probability of an actual manufactured circuit having the parameter configuration p, the circuit coverage of f by T is determined by Equation 1.2. In contrast to the conventional fault coverage (Equation 1.1), i.e., the percentage of faults detected by a test set in a representative circuit with fixed parameter values, Equation 1.2 describes the percentage of the manufactured circuit instances with distributed parameter values in which the test set detects a given fault.

$$CCcov(f,T) = \int_{p \in P} det_{C_p}(f,T)\pi(p)dp$$

(1.2)

Moreover, according to the statistical fault modeling, the delay behavior of a circuit element is given by a probability density function of delay sizes, denoted by  $\rho(s)$ . Considering a continuous range of sizes S, the fault coverage of f with all possible delay sizes can be statistically defined by integration of the circuit coverage over the delay size s, as given in Equation 1.3.

$$FC(f,T) := \int_{s \in S} CCcov(f,T)\rho(s)ds \tag{1.3}$$

The statistical test flow must try to maximize the fault coverage and generate (compact) test sets identifying the fault in as many circuit instances as possible. For this purpose, statistical fault simulation is performed iteratively for each combination in the parameter space. For the sake of simplicity, only the space for two parameters X and Y is illustrated in Figure 1.2. The area marked by the shadow represents the parameter combinations covered so far. The variation-unaware ATPG is invoked with fixed parameter values to cover a further parameter combination in the space. This flow is iterated

until an acceptable coverage of the complete range is achieved and can be followed by a compaction of the obtained test set.

Using the finally obtained tests, which are of high quality and variation-aware, it is possible to explore test strategies at system level, such as to separate circuit instances into classes, or called "bins", according to the frequency and voltage they can handle or according to the robustness of a system. Nevertheless, such systematic approaches are not focused by this thesis work. The test approaches at the gate level including ATPG for small delay defects and variation-aware fault simulation are more interested, which also motivate this thesis work.

#### 1.2.3 SDD Tesing and KLPG Algorithm

The scaled technology tends to bring an increasing number of small delays defects, which puts more importance on SDD testing. An SDD is only tolerable if all functional paths (those paths could be exercised by normal circuit operations) that go through the defect site excite a delayed transition (slow-to-rise or slow-to-fall) at the site, and finish propagating within the clock period. Obviously, under assumption of static timing assignment, generating tests for the longest path through the target defect will allow detection of the defect with the minimum possible size; no other paths through the defect site need to be considered.

However, depending on the accuracy of the timing analysis, and mostly due to the impact of process variations, the selected path may not be the longest indeed. An alternative approach is to test all functional paths through the defect site, which is however impractical for large circuits when all possible delay defects are targeted. It has been observed that the contribution of within-die random variations not spatially correlated is increasing with continued process scaling [13], which implies that delay defects caused by random variations can appear anywhere in a circuit. However, even a circuit of a reasonable size can contain billions of paths [16]. It is not possible to test and simulate all of them due to the time and cost constraints. As a compromise, test for a number of longest paths that go through the SDD is of interest. Similar to the idea of "n-detection", using tests generated for multiple longest paths raises the probability of detection.

Though it is easy to find the structurally longest paths by graph-traversal algorithms, many found paths are unsensitizable (or called false paths), i.e., no tests can be found to propagate desired transitions along these paths, and hence useless in practical applications. An efficient algorithm that identifies the longest sensitizable paths, which implies test generation for these paths (modeled as PDFs), is therefor required to tackle this problem. The test generation for PDF is very challenging because a large number of logic interdependency constrains have to be satisfied for the path sensitization. Such an algorithm that aims at identification of K (multiple) longest sensitizable paths through a given defect site, is called KLPG algorithm.

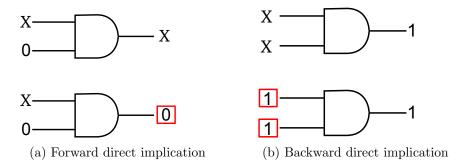

ATPG algorithms can be applied to verify the path sensitization by means of generating tests for the path modeled as PDF; the false path is identified if no tests can be found. Using traditional ATPG algorithms, tests are searched by means of assignments and justifications of signal values during the propagation of fault effect (D-Algorithm [39]); an implicit enumeration approach using path propagation constrains to limit the search space and backtrace (PODEM algorithm [40]); or approaches that improve the efficiency of the search by reducing the number of backtraces [41, 42]. Moreover, it has recently been shown that for several classes of faults a SAT-based ATPG [43-45], by which an ATPG problem is reduced to a Boolean Satisfiability Problem (SAT) instance and solved using a SAT solver [46], outperforms the structural approaches. Especially for the fault classes that could contain a large part of redundant faults (faults that are not testable), SAT-based ATPG is very efficient in contrast to the structural approach. The redundant faults can be quickly identified by SAT-based ATPG that takes techniques to prove the unsatisfiability of the Boolean formula. The performance of SAT-based ATPG can be significantly improved by utilizing learning strategies [47]. It is also possible to support non-standard fault models by a SAT-based ATPG tool, e. g., TIGUAN [44], by which tests are generated for conditional multiple stuck-at fault model that can be converted from non-standard faults. In [45], a SAT-based framework is proposed that can be integrated into the KLPG application by mapping the path search problem to SAT problem while the timing information is encoded directly into the SAT formula. As gate delays are encoded as integer numbers by the application, rounding errors of real-valued delays are inevitable; rounding strategies have to be applied to mitigate the error.

The conventional approach of KLPG [38] is to explore the structural search space containing sub-paths. As long as a sub-path is proved to be a false path, the sub-space containing all extensions of this sub-path is trimmed off immediately. Sub-paths in the search space are sorted by their largest possible length of a complete extension. Thus, the sub-path that can be potentially extended to the longest path will be tried first. The sensitizability of each extension from a sub-path to the next gate is verified. As long as the extension is proved to be incapable of propagating the desired transition without causing any conflict, the extended sub-path is eliminated from the search space; as a result all possible extensions from this path will not be considered. The next sub-path in order is taken into account. The verification can apply specific techniques that may efficiently identify the potential false paths but not all of these. To ultimately verify the sensitization of a completely extended path, ATPG algorithms can be used to generate tests that sensitize the path. A problem with the structural approach is that the number of sub-paths in the searching space can increase exponentially during the searching process. A size limitation has to be imposed to the searching space to ensure the efficiency of the application for testing large circuits. The arbitrary size can have an impact on the optimality of the solution since overflows beyond the limited space, among which the optimal solution can exist, are out of consideration. In presence of process variations, the possible sub-optimal solution of KLPG can cause a worse rate of defect escape. In this thesis work, an algorithm called Opt-KLPG is proposed. It aims at investigating the impact of the size of the search space on the optimality of the KLPG solutions. Moreover, it provides an iterative procedure that ensures all sub-paths will be considered and thus an optimal solution is guaranteed. Chapter 2 details the algorithm and presents experimental results for academic/industrial circuits.

#### 1.2.4 Variation-aware Fault Simulation

Depending on the complexity of ATPG, the effectiveness of generated tests could be limited in terms of the ability of detecting target faults and the test application time proportional to the number of applied tests. High-quality and possibly compact test sets are preferred to minimize the cost of applying tests, which can be translated into the timing and memory requirements of test equipment, and to avoid the cost due to delivering defective or unreliable devices escaped from the tests. To obtain high-quality tests, fault simulation [2, p. 75] is required to efficiently evaluate the tests and report

the fault coverage, based on which the tests could be chosen. Moreover, test sets can be compacted without sacrificing the fault coverage before applied to actual devices.

Fault simulation commonly consists of two logic simulation runs that evaluate the logic functions of gates in their structural order, in the fault-free circuit and in the same circuit with the injected fault (by simulating the fault effect). The detection of the fault is determined if the difference in at least one output of both simulation runs is observed. In context of delay testing under process variations, the fault simulation needs to estimate the timing behavior of circuit elements affected by process variations with both static and dynamic sources (variations in physical parameters during the manufacturing and in electrical parameters during the operation). Dynamic variations depending on the applied tests, such as the fluctuations in supply voltage, could have a large impact on the gate delays. To accurately simulate these effects, the simulation should incorporate important sources of variations and estimate their impact on circuit timing based on a relatively accurate electrical model.

As technology scales into the VDSM regime, power supply noise, which explicitly refers to noise appearing on the supply and ground nets of the chip and in turn affecting the voltage supplied to gates, has become one of the major variation sources [48–50]. With the continuously scaled sizes of transistors, more transistors are allowed to be packed into an area while the improved transistor performance has resulted in a large increase in frequency. As a result, the increased density of switching devices and frequency can lead to the power density problem [51]. That is, the amount of current to be delivered increases significantly with a simultaneous reduction in power supply voltages, which could be localized according to instantaneous switching of gates, and results in excessive gate delays.

These voltage fluctuations on the power and ground distribution networks, referred by power supply noise, originate from the currents flowing through the parasitic elements of both the on-chip and package supply networks. The power supply noise can be further divided into two groups depending on whether they are caused by the rate of change of the instantaneous currents flowing through parasitic inductive elements of the network (L.di/dt) or by the instantaneous currents flowing through the resistive elements of the network (IR) [52–54]. This thesis work focuses on the IR drop, which is the mainly

produced noise on the on-chip Power Distribution Network (PDN) since it is predominantly resistive [55]. Targeting on an accurate yet efficient circuit simulation under the impact of the IR drop effect, an electrical model that estimates the gate delay depending on important electrical parameters has to be established. Moreover, a timing-aware event-driven logic simulation is proposed, which benefits from the time complexity of the simulation algorithm while keeping the accuracy by employing the electrical model. This application can be used to estimate IR drop effect given the electrical models, and further adapted to electrical models that incorporate more electrical parameters to raise the accuracy. By injecting faults, it is also possible to perform variation-aware fault simulations, explicitly considering the impact of IR drop. The developed simulator has been applied to large circuits (up to more that 70K gates) with reasonable performance. Chapter 3 introduces the electrical model and details the simulation algorithm as well as the experimental results.

### Chapter 2

KLPG: K Longtest Path

# Generation

#### 2.1 Motivation

Small manufacturing defects increasingly affect the timing behavior of the circuit as technology scales and in turn degrade the circuit performance by inducing extra delays [17]. PDF [2, 17] is a conventional fault model that can be used to test such manufacturing defects. The circuit is considered faulty by testing a PDF if the propagation of an input transition through the target path exceeds the maximum allowed timing period, which usually refers to the clock cycle. In context of SDD testing, any path through the defect site can be modeled as a PDF. A two-pattern test applied in two consecutive time frames for the PDF launches an input transition and propagates the transition along the path. The delay assignment, which refers to the assignment of a delay (a number or a range) to each connection and transition (rising or falling) [2], is often required to estimate the circuit timing. The total cumulated delay along the path can be compared to the specification time, at which the output will be observed and should stabilize at its correct value in the fault-free case, to determine if the circuit behaves faulty in presence of the target fault. If such a test exists, the path is said to be sensitizable, and sensitized by the test, otherwise the path is called a false path.

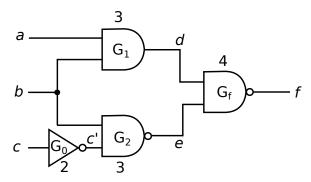

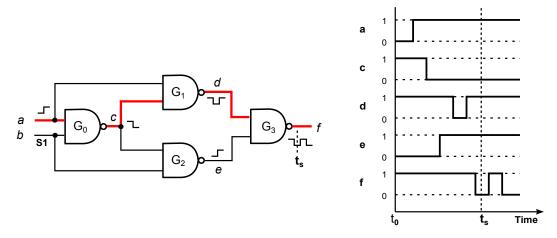

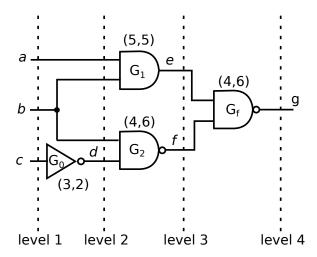

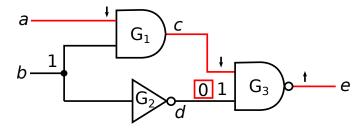

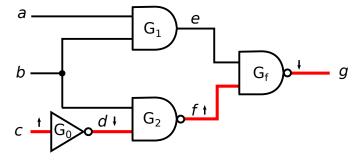

The main problem with the PDF model is the large amount of the paths in a real circuit; the exhaustive testing that tries to cover all paths is very expensive and almost infeasible for many circuits. Instead, most approaches try to find the test that sensitizes a given path, and verify if any faulty behavior presents itself under this test for all possible delay sizes caused by manufacturing defects. The quality of the test can be evaluated by how close the minimum actually detected delay fault sizes are to the minimum possible detectable fault sizes [56]. Obviously, for tests sensitizing shorter paths, more delay sizes might not be detected since it takes less propagation time through these paths than longer ones. For instance, Figure 2.1 presents a circuit containing gates with different delays according to a delay assignment. Commonly the gate delay is given by a set of pin-to-pin (from an input to the output) propagation times depending on the input transition. In this example, all pin-to-pin delays for the same gate are assumed to be identical. The inverter  $G_0$  has the delay 2, the AND gate  $G_1$  and the NAND gate  $G_2$  have the delay 3 while the NAND gate  $G_f$  where the defect lies has a larger delay 4. Assuming that the clock period is 8, the delay fault can only be detected by a test sensitizing the longest path  $c \to c' \to e \to f$  since the propagation time cumulated along the path is 9, which exceeds the clock period. For tests sensitizing other paths, only delay sizes larger than 4 can be detected.

FIGURE 2.1: An example of the longest path

Thus, tests that sensitize the longest path are commonly preferred by small delay testing to achieve better fault coverages. Furthermore, instead of the global longest path, sensitization of the longest path through a given defect site is required by testing local defects, such as resistive opens or shorts.

Under process variations, different instances of a circuit design can exhibit various timing behaviors. Thus, the longest paths selected based on the nominal delay assignment, which can be obtained by timing analysis for the circuit design, might not be the actual longest path. Multiple longest paths through the fault site need to be identified and sensitized to raise the probability of detection. For this purpose, the KLPG algorithm is

proposed [38] that targets on searching K longest sensitized paths through each possible fault sites efficiently. The approach employs graph traversal search algorithm and a data structure called path store to store all sub-paths to be considered during the search process. Under the consideration of efficiency, an arbitrary size is exposed on the path store to limit the searching space that could be extraordinarily large in practice. The approach also applies a number of speed-up techniques that help to identify false sub-paths in advance and remove them from the path store immediately. Overflows from the path store will be discarded without consideration, which may lead to a sub-optimal solution with shorter or less paths found instead. To investigate the impact of the store size on the solution optimality, this thesis work proposes a new algorithm called Opt-KLPG that guarantees the optimality of the KLPG solution.

The remainder of the chapter is organized as follows: Section 2.2 gives preliminary knowledge related to the algorithm; the KLPG flow proposed by Walker et al. [38] is introduced in Section 2.3 briefly; Section 2.4 details the Opt-KLPG Algorithm [57]; Section 2.5 presents the application of Opt-KLPG in a statistical delay testing flow under process variations and Section 2.6 reports the experimental results.

#### 2.2 Preliminaries

#### 2.2.1 Classification of Path Delay Faults

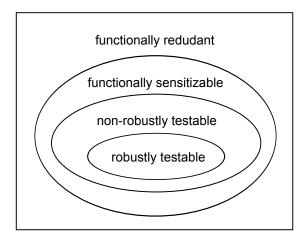

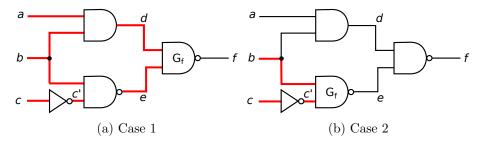

A PDF can be classified according to its testability under various conditions. One of the most popular classifications of PDF is Cheng's classification [2], given as follows: robustly testable, non-robustly testable, functionally sensitizable and functionally redundant PDFs. Figure 2.2 presents the relation between classified PDF sets. Subset relations can be observed that the functional sensitizable set contains the non-robustly testable set, which further contains the robustly testable set.

Every superset of PDF has a looser test condition—the condition required by a test to detect the PDF—than its subset. The following definitions are used to describe the test condition. A path in a circuit is a sequence of signals denoted by  $s_0s_1...s_n$ , where  $s_0$  is a primary input,  $s_1...s_{n-1}$  are gate outputs and  $s_n$  is a primary output. An on-input is a connection between two gates along the path. An off-path input (or a side-input) is

Figure 2.2: Testability classification of PDFs [2]

any input of a gate on the path other than its on-input. The test for a PDF consists of two patterns  $(P_1, P_2)$  applied to the circuit consecutively.

A PDF is functionally sensitizable if there exists an input vector  $P_2$  such that all the side-inputs settle to non-controlling values<sup>1</sup> on  $P_2$  when the on-inputs have the non-controlling values. Otherwise, it is called functionally unsensitizable. A PDF is functionally redundant if the corresponding path is a false path—the path cannot be sensitized by any test—under all delay assignments. A functional unsensitizable path is also functionally redundant. However, this is a sufficient condition but not a necessary one. The reason is that functional sensitization is only defined with respect to the second pattern  $P_2$  while the test for a PDF requires two patterns; even if  $P_2$  satisfying the functional sensitizable condition can be found, it does not mean the initialization vector  $P_1$  can always be found such that the two-pattern test sensitizes the path.

A PDF is non-robustly testable if and only if there exists a two-pattern test  $(P_1, P_2)$  satisfying the following conditions:

- it launches the desired logic transition at the primary input of the target path;

- all side-inputs of the path settle to non-controlling values under  $P_2$ .

A PDF is robustly testable if and only if there exists a two-pattern test  $(P_1, P_2)$  that satisfies the condition for the non-robust test, and, whenever the transition at an on-input is from the non-controlling value to the controlling value, a steady non-controlling value

<sup>&</sup>lt;sup>1</sup>An input of a gate is said to have a *controlling* value if it uniquely determines the gate output independent of other gate inputs. Otherwise, the value is said to be *non-controlling*.

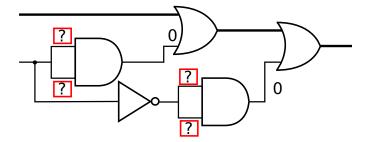

is required at every side-input of the same gate. A robust test can detect the target PDF independent of the delays in the rest of the circuits, i.e., it guarantees the detection of the target fault in presence of other PDFs, whereas the detection is not guaranteed by a non-robust test in the same circumstance. The reason is that a non-robust test allows the output to change before the on-path transition is propagated, which can invalidate the test result. An example of such an invalidation is presented in Figure 2.3.

FIGURE 2.3: An example of the invalidation by a non-robust test

A two-pattern test  $\{(0,1),(1,1)\}$  is applied to the circuit in the left under a given delay assignment. The path corresponding to the target PDF  $a \uparrow c \downarrow d \uparrow f \downarrow (\uparrow \text{ and } \downarrow \text{ denote})$ the rising and falling transitions, respectively) is marked with bold lines. Signals in the circuit are initialized by the first vector (0,1), and stabilize before the time point  $t_0$ . The signal transitions after  $t_0$  are represented in the timing diagram right. After applying the second vector (1,1), a rising transition is launched on the primary input a while b remains a static value of 1, denoted by S1. The output of  $G_0$  c falls from 1 to 0 after the gate delay of  $G_0$ . A glitch  $1 \to 0 \to 1$  at the output of  $G_1$  d is caused by the input transitions at a and c with different arrival times. Assuming that the rising transition at the output of  $G_2$  e is earlier than the first transition of d under the given gate delays, consequently the output f has a switching value of  $1 \to 0 \to 1 \to 0$ . If the observation point is  $t_s$ , the target PDF will not be detected by the test since the correct value 0 is observed at the output. The test is invalidated though the PDF is present, i.e., the transition propagated along the corresponding path is delayed (the  $1 \to 0$  transition after  $t_s$  at f). For the same circuit, an example of the robust test for PDF  $a \uparrow d \downarrow f \uparrow$ is  $\{(0,0),(1,0)\}$ . It satisfies the non-robust condition, and the additional condition for

the robust test in that the side-input e steadily remains 1 when the on-input d switches from the non-controlling value 1 to the controlling value 0.

#### 2.2.2 SAT-solver and SAT-based ATPG

SAT is the problem of determining whether there exists an interpretation that satisfies a given Boolean formula. In other words, the problem is defined by whether every variable in the given Boolean formula can be assigned with a logic value TRUE or FALSE so that the formula evaluates to TRUE. If such variable assignments exist, the formula is called *satisfiable*, otherwise the formula is *unsatisfiable*.

Solvers for SAT are powerful formal proof engines that determine an assignment to variables of a Boolean function  $\Phi: \{0,1\}^n \to \{0,1\}$  such that  $\Phi$  evaluates to 1 or prove that no such assignment exists [58]. As given by the function notation, the n variables of the function are assigned with either 1 or 0, which corresponds to the logic value TRUE or FALSE; the function evaluates to 1 or 0 indicating that the formula is satisfied by the assignment or not. The function is given in Conjunctive Normal Form (CNF), which is a conjunction of clauses; a clause is a disjunction of literals and a literal is a Boolean variable in its positive form (x) or negative form (x). SAT and extensions thereof are well investigated problems, for which efficient solving algorithms have been proposed in the past (e. g., [59–61]).

ATPG is a technology used to find a sequence of tests that can be applied to a digital circuit to distinguish between correct and faulty circuit behaviors caused by defects. A SAT-based ATPG requires a transformation of the problem description into a Boolean formula in CNF as defined above. Each signal in the circuit can be assigned with a Boolean variable representing its logic value 0 or 1. The functionality of each gate can be transformed into a set of clauses using Boolean variables to represent its inputs and output. Using truth tables or algebraic conversion a CNF can be easily derived for each gate type. Then the complete circuit is represented by a conjunction of all CNFs derived for gates, which is a CNF itself. Given a fault to be tested, additional constrains for fault excitation and propagation of the faulty behavior to some observation point can be formulated and given as a CNF. The conjunction of the CNF for the circuit and the CNF for the fault construct the SAT instance to be satisfied or proved to be not satisfiable by a SAT-solver. Each assignment of variables in the SAT instance corresponds to a test

for the given fault that excites the fault and propagates the fault effect for observation. If the SAT-solver proves that no such assignments exist, the fault is not testable.

The algorithm Opt-KLPG applies the SAT-based ATPG tool TIGUAN from the University of Freiburg [44] to verify the sensitizability of the found longest paths. The tool is originally designed for detection of conditional multiple stuck-at (CMS@) faults in multiple time frames. A CMS@ fault consists of a list of arbitrary assignments of logic values in a two consecutive time frames and a list of stuck-at faults, denoted as follows:

- a list of  $s@0 \leftarrow v$  or  $s@1 \leftarrow v$  where 0 or 1 behind @ denotes the first or second time frame, respectively; v denotes the logic value assigned to signal s in the corresponding time frame, and

- a list of stuck-at 0 or stuck-at 1 faults.

The algorithm that constructs the CMS@ fault for a path will be given in 2.4.4.2. If a test for the constructed fault can be found by TIGUAN, the corresponding path is proved to be testable, otherwise it is a false path and will be excluded from the solution—the K longest sensitizable paths.

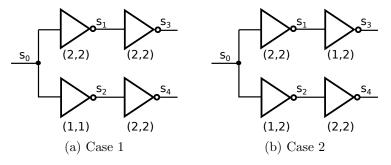

#### 2.3 Walker's KLPG Algorithm

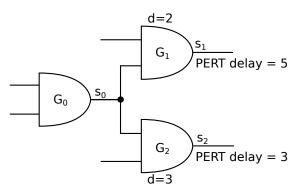

The KLPG algorithm proposed in [38] is to find K longest sensitizable path through a target gate  $G_f$ . The delay assignment is given in advance for every gate in terms of a set of propagation time of the rising or falling input transition from each input to the output. The minimum-maximum delay from each gate to a primary output without considering logical constrains, which is called min-max PERT delay, is computed as well. Gates that are neither in input-cone nor in output-cone of  $G_f$  are first identified. (The input- and output-cones of a gate refer to the circuit blocks driving and driven by the gate, respectively.) They are not considered by computation of PERT delays since these gates can never be added to a path through  $G_f$ . The computation is performed iteratively in the reversed order of gate level. Obviously the PERT delay is zero for primary outputs. For signals driving gates, the PERT delay is given by the sum of gate delay and the PERT delay from the gate output. For signals driving a fan-out, PERT

delays for branches are computed at first, the minimum and maximum among them correspond to the max and min PERT delays of the stem, respectively; the associated branches are noted as well.

A data structure called *path store* is used to store sub-paths considered at the same time. It is initialized by sub-paths, each corresponds to a rising or falling primary input in input-cone of  $G_f$ . Assuming that input-cone of  $G_f$  contains n primary inputs,  $2 \times n$  sub-paths are inserted into the path store. It is sorted by the max esperance of the sub-paths. The max (min) esperance of a sub-path is the sum of the path length and the max (min) PERT-delay of its last node. In other words, it corresponds to the upper (lower) bound of the path delay when it grows to a complete sensitizable path. These two bounds can be used by false path elimination techniques to speed up the searching.