### Request-driven GALS Technique for Datapath Architectures

Von der Fakultät für Mathematik, Naturwissenschaften und Informatik der Brandenburgischen Technischen Universität Cottbus

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

(Dr.-Ing.)

genehmigte Dissertation

vorgelegt von

Dipl.-Ing., M.Sc.El.Eng.

Miloš Krstić

geboren am 18. Oktober 1973 in Niš (Serbien und Montenegro)

Gutachter: Prof. Dr.-Ing. Rolf Kraemer

Gutachter: Prof. Dr.-Ing. Heinrich-Theodor Vierhaus

**Gutachter: Prof. Christian Piguet**

Tag der mündlichen Prüfung: 07.02.2006

### Acknowledgements

While working in the IHP's System Design department I had support from many colleagues. At this place I want to thank those who helped me with the thesis:

First of all, I want to thank to my supervisor Prof. Rolf Kraemer who supported my work on this topic over the past years.

I especially want to thank Dr Eckhard Grass who guided and supervised my activities in the area of asynchronous circuit design. In the mutual discussions we had, we defined many solutions described in the following text. Without his support this thesis would not be possible.

Dr Alfonso Troya, Dr Koushik Maharatna, and Ulrich Jagdhold were part of our great team that has developed a synchronous WLAN baseband processor. Many thanks for their support and friendship.

I also want to thank Maxim Piz for his support in performing MATLAB simulations.

Special thanks to my proofreaders: Dr Eckhard Grass, Dr Michael Methfessel, Christoph Wolf and Daniel Dietterle.

I am very grateful to Alexandra Julius, Christian Stahl, Prof. Wolfgang Reisig and Dr Frank Winkler from Humboldt University in Berlin. I really enjoyed working together with them on GALS topics, especially in the area of formal analysis and during the development of the externally driven GALS wrapper. Furthermore, I want to acknowledge Kim Fahrion for developing the 3DConverter tool and Prof. Mark Greenstreet, University of British Columbia - Vancouver, who helped me with many valuable comments.

I want to thank my parents and sister for their support during all these years.

Finally, gratitude and love go to my wife Sanja and son Boris, for their love and support.

# Contents

| Abstract                                                  | ix |

|-----------------------------------------------------------|----|

| Zusammenfassung                                           | xi |

| 1. Introduction                                           | 1  |

| 1.1 Design Challenges for Wireless Communication Systems  | 1  |

| 1.2 GALS as a Solution for the System Integration Problem | 3  |

| 1.3 Structure of the Thesis                               | 4  |

| 2. Related Work – from the Two-Flop Synchroniser to GALS  | 7  |

| 2.1 Introduction                                          | 7  |

| 2.2 System Integration Strategies                         | 8  |

| 2.2.1 Standard Synchronisers                              | 9  |

| 2.2.2 Adaptive Synchronisation                            | 10 |

| 2.2.3 FIFO Synchronisation                                | 11 |

| 2.2.4 GALS Systems                                        | 12 |

| 2.3 Power Saving with GALS                                | 18 |

| 2.4 Open Questions and Directions for Further Research    | 19 |

| 3. Proposed Novel GALS Architecture                       | 21 |

| 3.1 Introduction                                          | 21 |

| 3.2 Motivation and General Principles                     | 21 |

|    | 3.3                                                       | System                                                                                           | n Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                       |

|----|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|    | 3.4                                                       | Reques                                                                                           | st Driven Technique with External Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                       |

|    | 3.5                                                       | Potenti                                                                                          | al Gain of the Novel GALS Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                                                       |

| 4. | Harc                                                      | dware A                                                                                          | Architecture of the GALS Wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31                                                       |

|    | 4.1                                                       | Introdu                                                                                          | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31                                                       |

|    | 4.2                                                       | Overall                                                                                          | Structure of the Asynchronous Wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31                                                       |

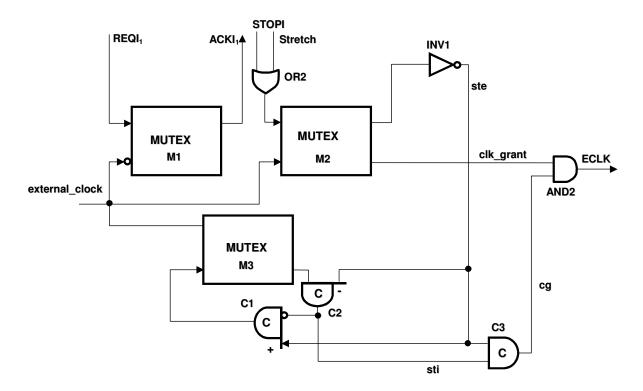

|    |                                                           | 4.2.1                                                                                            | Pausable Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                                                       |

|    |                                                           | 4.2.2                                                                                            | Clock Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36                                                       |

|    |                                                           | 4.2.3                                                                                            | Time-out Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                       |

|    |                                                           | 4.2.4                                                                                            | Input Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38                                                       |

|    |                                                           | 4.2.5                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44                                                       |

|    |                                                           | 4.2.6                                                                                            | Mutual Exclusion Element                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47                                                       |

|    | 4.3                                                       | Forma                                                                                            | al Analysis of the Asynchronous Wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                                                       |

|    | 4.4                                                       | Extern                                                                                           | nally Clocked Asynchronous Wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48                                                       |

|    |                                                           |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

| 5  | G                                                         | ALS Ap                                                                                           | plication in Wireless Communication Systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53                                                       |

| 5  | <b>G</b> /<br>5.1                                         |                                                                                                  | plication in Wireless Communication Systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>53</b><br>53                                          |

| 5  | 5.1                                                       | Introdu                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

| 5  | 5.1<br>5.2                                                | Introdu<br>Baseba                                                                                | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53                                                       |

| 5  | 5.1<br>5.2                                                | Introdu<br>Baseba                                                                                | and Processor Compliant to IEEE 802.11a Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53<br>54                                                 |

| 5  | 5.1<br>5.2                                                | Introdu<br>Baseba<br>GALS F<br>5.3.1                                                             | and Processor Compliant to IEEE 802.11a Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53<br>54<br>57                                           |

| 5  | 5.1<br>5.2<br>5.3                                         | Introduc<br>Baseba<br>GALS F<br>5.3.1<br>5.3.2                                                   | Inction       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . </td <td>53<br/>54<br/>57<br/>60</td> | 53<br>54<br>57<br>60                                     |

| 5  | 5.1<br>5.2<br>5.3                                         | Introduc<br>Baseba<br>GALS F<br>5.3.1<br>5.3.2<br>Power                                          | Inction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53<br>54<br>57<br>60<br>60                               |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduc<br>Baseba<br>GALS F<br>5.3.1<br>5.3.2<br>Power                                          | and Processor Compliant to IEEE 802.11a Standard       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                      | 53<br>54<br>57<br>60<br>60<br>62                         |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduc<br>Baseba<br>GALS I<br>5.3.1<br>5.3.2<br>Power<br>Importa                               | and Processor Compliant to IEEE 802.11a Standard       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                      | 53<br>54<br>57<br>60<br>60<br>62<br>64                   |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduce<br>Baseba<br>GALS F<br>5.3.1<br>5.3.2<br>Power<br>Importa<br>5.5.1                     | and Processor Compliant to IEEE 802.11a Standard       .       .         Partitioning       .       .       .         Transmitter Dataflow Organisation       .       .       .         Receiver Dataflow Organisation       .       .       .         Saving Mechanisms       .       .       .         Activation Interface for Blocks Rx_1 and Rx_2       .       .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53<br>54<br>57<br>60<br>60<br>62<br>64<br>64             |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduce<br>Baseba<br>GALS F<br>5.3.1<br>5.3.2<br>Power<br>Importa<br>5.5.1<br>5.5.2            | and Processor Compliant to IEEE 802.11a Standard       .       .       .         Partitioning       .       .       .       .         Transmitter Dataflow Organisation       .       .       .       .         Receiver Dataflow Organisation       .       .       .       .         Saving Mechanisms       .       .       .       .       .         Activation Interface for Blocks Rx_1 and Rx_2       .       .       .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53<br>54<br>57<br>60<br>60<br>62<br>64<br>64<br>65       |

| 5  | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduce<br>Baseba<br>GALS F<br>5.3.1<br>5.3.2<br>Power F<br>Importa<br>5.5.1<br>5.5.2<br>5.5.3 | and Processor Compliant to IEEE 802.11a Standard       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                      | 53<br>54<br>57<br>60<br>60<br>62<br>64<br>64<br>65<br>66 |

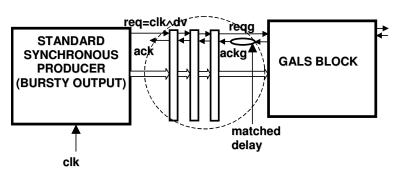

| 5.6.1 Synchronous to Asynchronous Communication                                            | 69  |

|--------------------------------------------------------------------------------------------|-----|

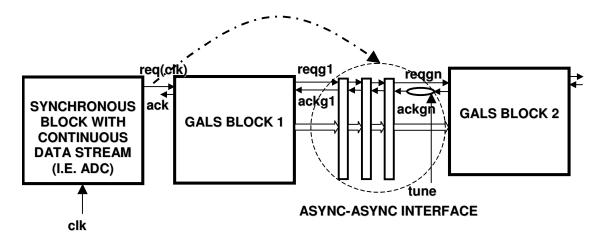

| 5.6.2 Synchronous to Asynchronous Communication with a Continuous Synchronous Data Stream. | 69  |

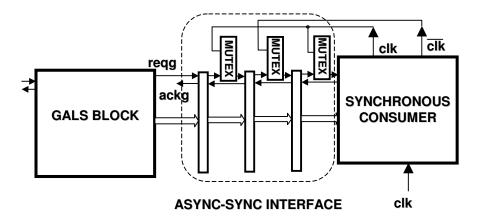

| 5.6.3 Asynchronous to Synchronous Communication                                            | 70  |

| 6 Design for Testability in GALS Systems                                                   | 73  |

| 6.1 Introduction                                                                           | 73  |

| 6.2 Test Techniques for GALS Systems                                                       | 74  |

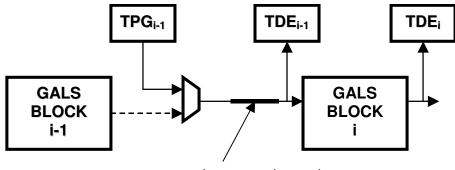

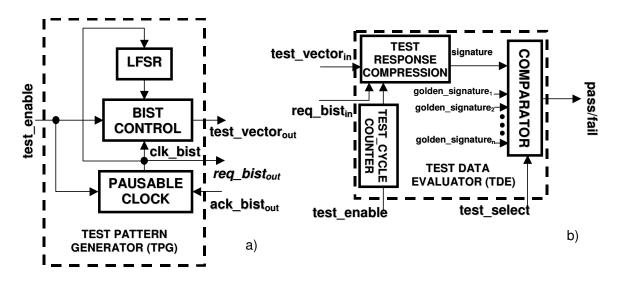

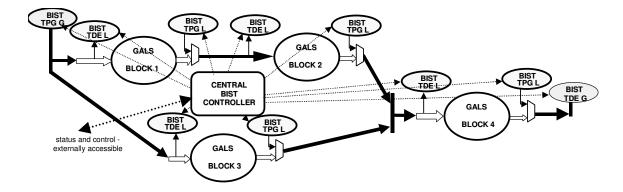

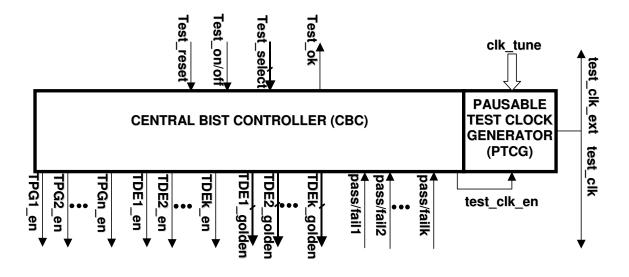

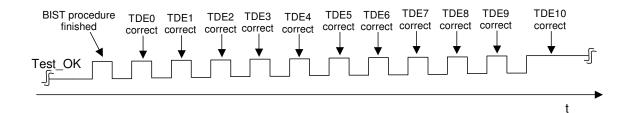

| 6.3 Proposed BIST Architecture                                                             | 75  |

| 6.4 Implementation of the BIST in the Baseband Processor                                   | 79  |

| 7 Implementation and Evaluation of GALS Systems                                            | 85  |

| 7.1 Introduction                                                                           | 85  |

| 7.2 Design Flow                                                                            | 85  |

| 7.3 System Integration with GALS                                                           | 89  |

| 7.4 Conceptual GALS Design Framework                                                       | 90  |

| 7.5 Asynchronous Wrapper Implementation                                                    | 92  |

| 7.6 Experimental GALS Chip                                                                 | 94  |

| 7.7 GALS Baseband Processor Implementation                                                 | 96  |

| 7.7.1. Evaluation of Synchronous and GALS Baseband Processor                               | 99  |

| 8. Experimental Results                                                                    | 103 |

| 8.1 Introduction                                                                           | 103 |

| 8.2 Functional Verification of the GALS Baseband Processor                                 | 103 |

| 8.3 Power Measurement                                                                      | 105 |

| 8.4 Supply Noise Measurement                                                               | 106 |

| 9. Conclusions                                                                             | 109 |

| 9.1 Achieved Results                                                                       | 109 |

| 9.2 Request-Driven GALS as a Solution – Pros and Cons.                                     | 110 |

| 9.3 Future Work                                                                            | 110 |

| 10. References                                                                             | 113 |

| Acronyms and Symbols                                                                       | 121 |

| Curriculum Vitae . | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | - | • | 12 | 25 |

|--------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|

|--------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|----|

### Abstract

In this thesis a novel Globally Asynchronous Locally Synchronous (GALS) technique applicable to wireless communication systems and generally to datapath architectures is presented. The proposed concept is intended for point-to-point communication with very intensive but bursty data transfer between the system blocks.

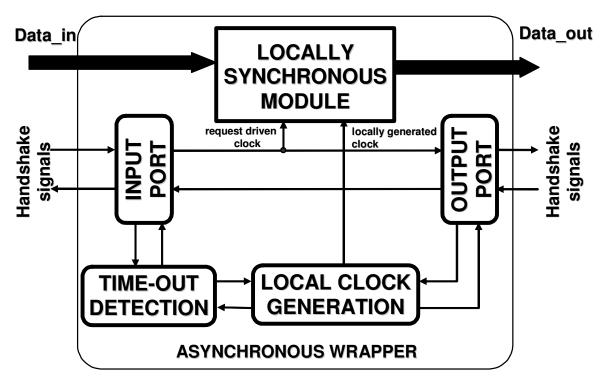

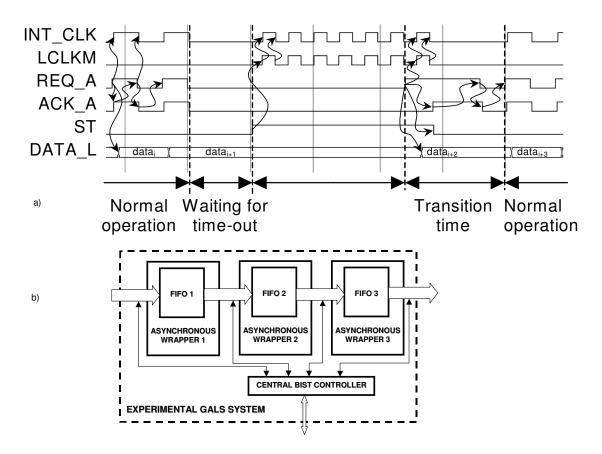

The GALS technique introduced here is based on a request-driven operation of locally synchronous modules. The key idea behind this request-driven approach is that a module can use the input request signal as its clock while receiving a burst of data. Inactivity of the request line is detected with a special time-out circuitry. When time-out occurs, clocking of the locally synchronous module is handed over to a local ring oscillator or an external clock source. This allows emptying of internal pipeline stages of a locally synchronous module after a burst of data was received.

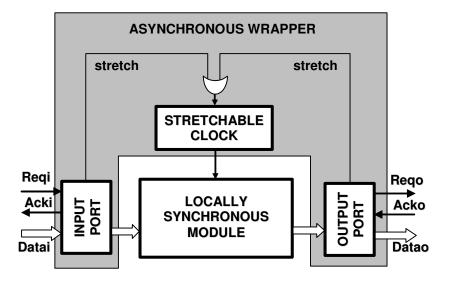

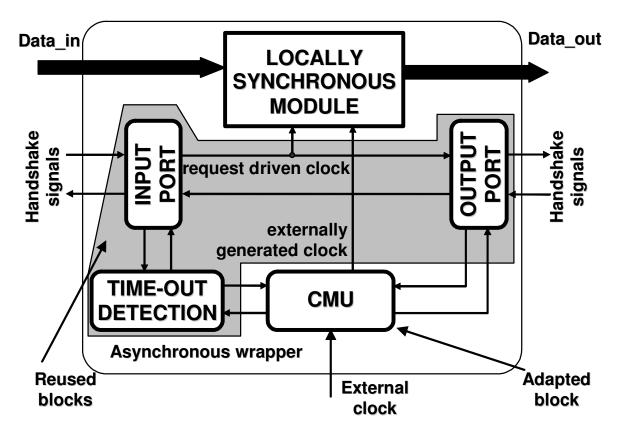

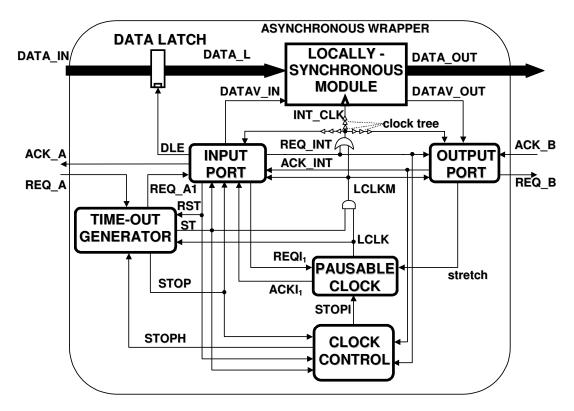

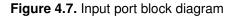

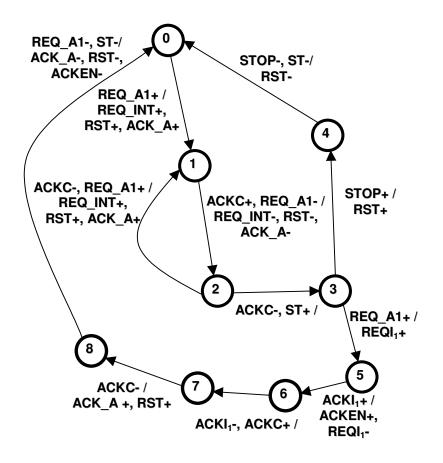

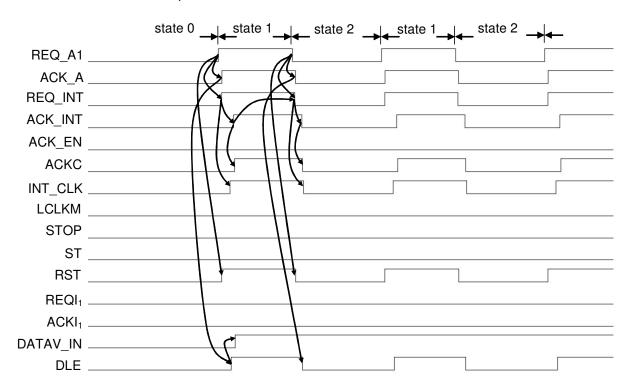

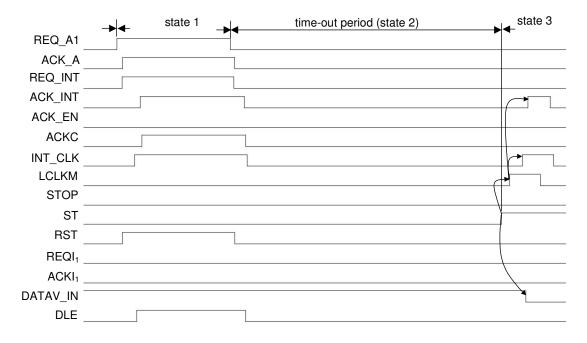

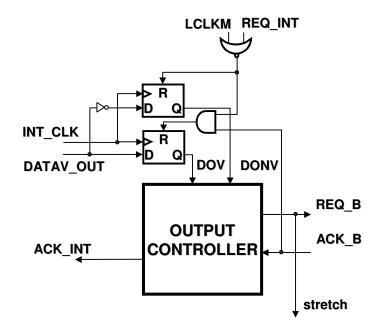

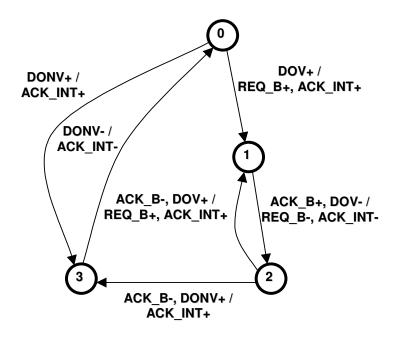

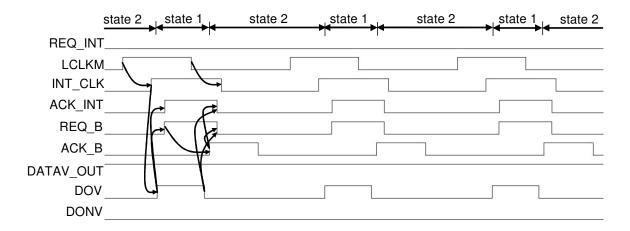

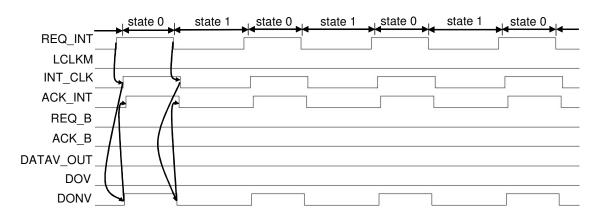

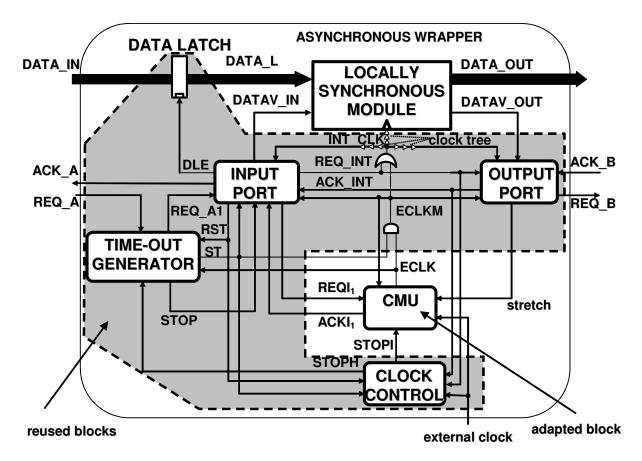

Based on this concept, a practical hardware implementation of an asynchronous wrapper is proposed. The asynchronous wrapper consists of several components, with different complexity and structure. The internal clocking circuitry is based on a tunable ring oscillator that actually consumes most of the area of the asynchronous wrapper. The main wrapper components are input and output ports, which are developed as an Asynchronous Finite State Machine (AFSM). Those ports perform hazard-free handshake operations between different GALS blocks and control safe transfer of the data. The complete asynchronous wrapper uses a few thousand gates, which is acceptable in comparison with an average synchronous block size of a few hundred thousand gates. Furthermore, we discuss an alternative asynchronous wrapper architecture based on external clocking.

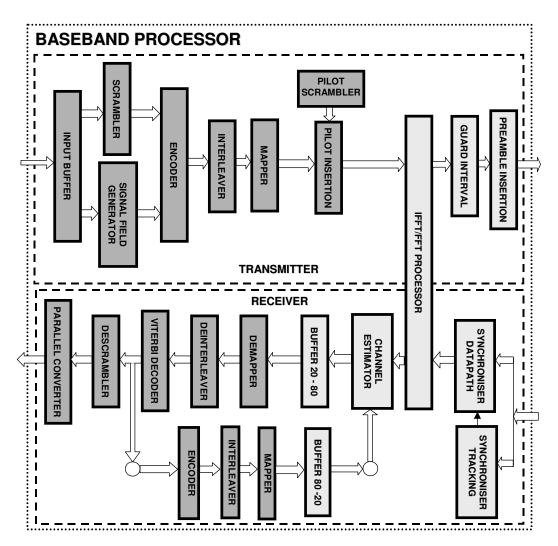

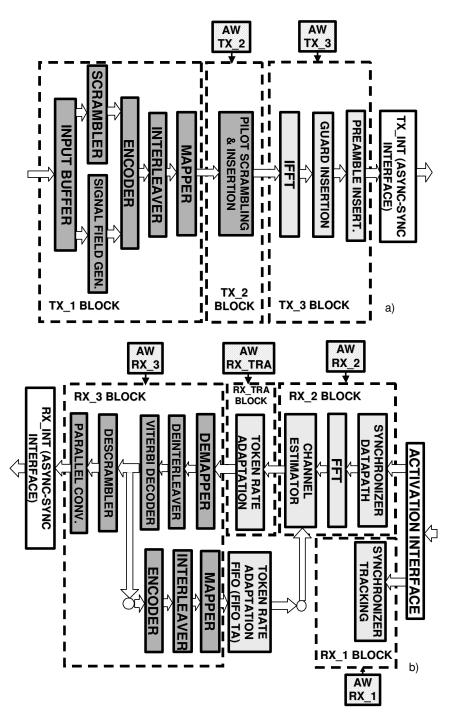

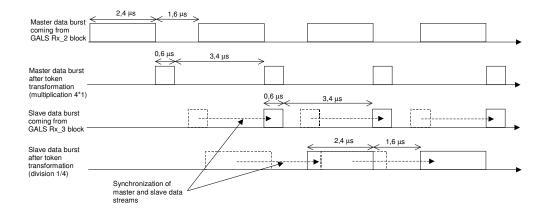

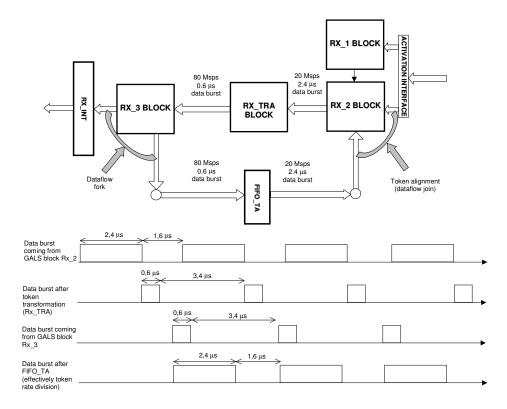

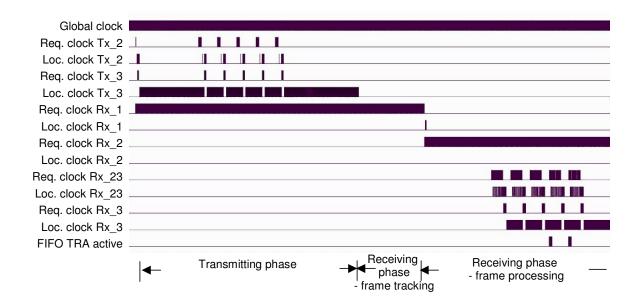

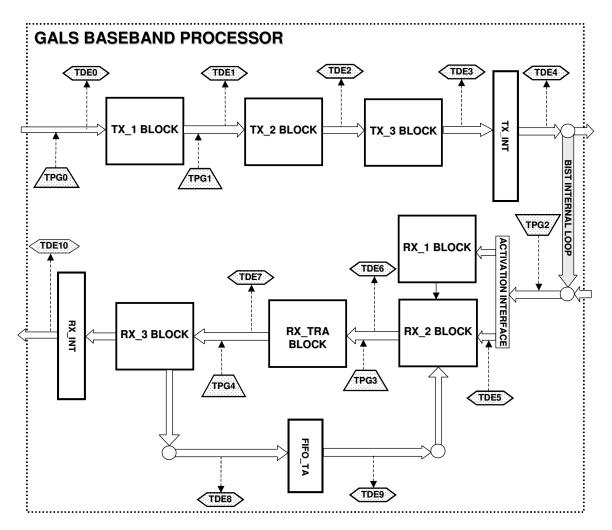

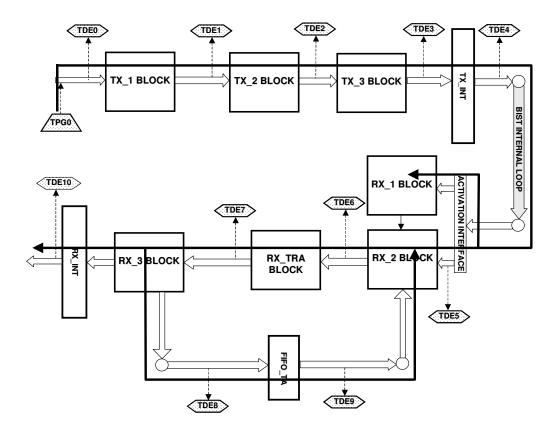

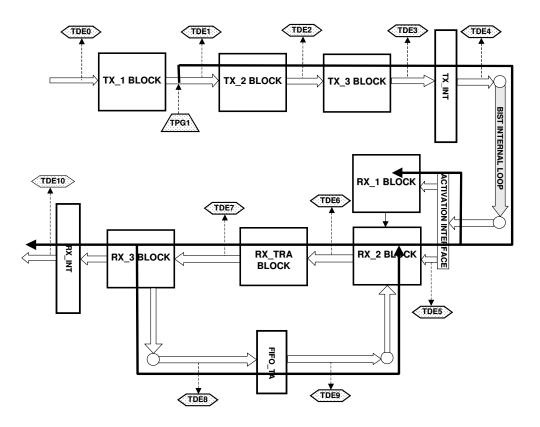

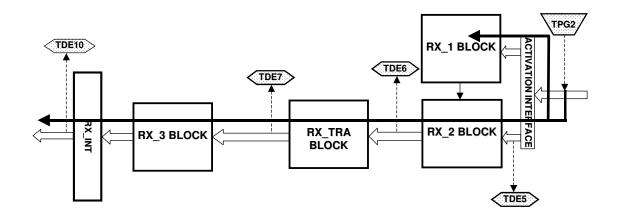

The developed wrapper is applied to the design of an IEEE 802.11a compliant baseband processor with the aim to alleviate the problems of system integration, timing closure, clock skew, power consumption and electro-magnetic interference (EMI). The baseband processor is

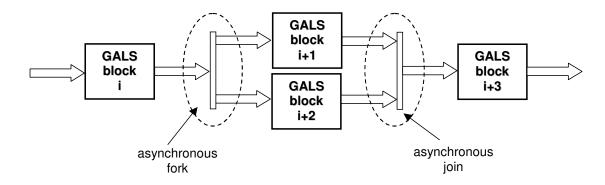

partitioned into a set of different GALS blocks. The criteria for GALS partitioning were power saving and natural architectural boundaries between the different blocks. Locally synchronous modules were extended with adequate asynchronous wrappers. In order to control the complex dataflow between the blocks, some additional asynchronous blocks for providing join, fork, and data-rate adaptation functions between the GALS blocks were proposed. Additionally, it was needed to guarantee certain performance levels for communication with the synchronous environment. For that reason, synchronous-to-asynchronous and asynchronous-to-synchronous interface blocks were proposed. For testing purposes, our GALS baseband processor is fitted with Design for Testability (DFT) logic based on Built-in Self-Test (BIST).

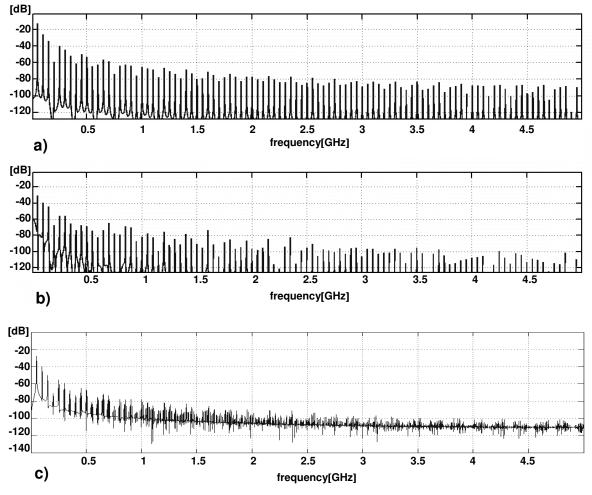

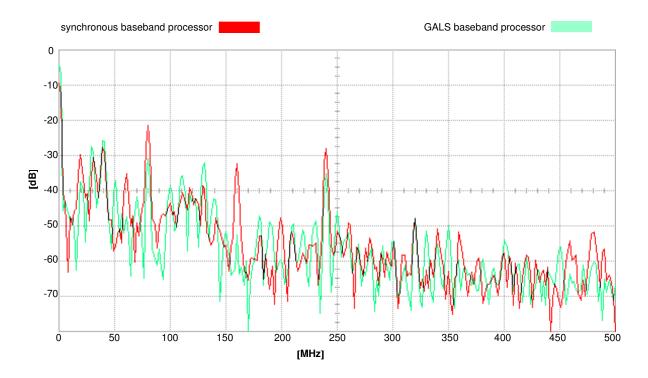

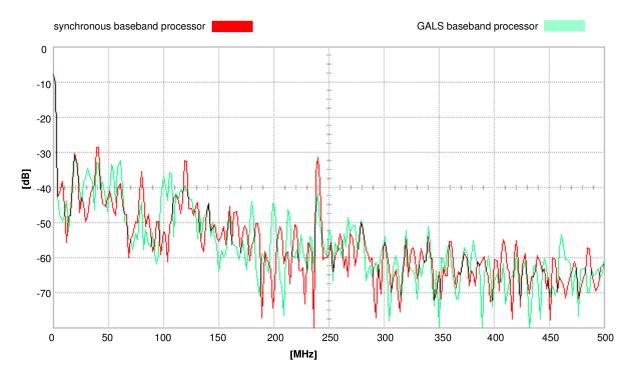

The complete baseband processor including GALS wrappers was integrated, synthesized, layouted, and finally fabricated. Implementation details are described in order to evaluate the advantages of the proposed concept. Furthermore, a design-flow for GALS systems is proposed. Finally, results of the measurements are presented and discussed. The GALS design was compared with a synchronous version of the baseband processor with implemented clock-gating as power saving technique. In our experimental setup we have measured a 1% reduction in dynamic power consumption, 30% reduction in instantaneous supply voltage variations, and 5 dB reduction in spectral noise.

Keywords: GALS, System Integration, Asynchronous design, EMI, BIST

### Zusammenfassung

In dieser Doktorarbeit wird eine global asynchrone, lokal synchrone (GALS) Technik, die auf drahtlose Kommunikationssysteme und im Allgemeinen auf Datenpfad-Architekturen anwendbar ist, dargestellt. Das vorgeschlagene Konzept ist für Punkt-zu-Punkt organisierte Strukturen mit sehr intensiver, aber Block organisierter Datenübertragung zwischen den System-Blöcken vorgesehen.

Die GALS-Technik, die in dieser Arbeit eingeführt wird, basiert auf einem Request-driven Betrieb der lokalen synchronen Blöcke. Die Schlüsselidee hinter diesem Request-driven Konzept ist, dass ein Modul das Request-Signal als Taktsignal beim Empfangen eines Blocks von Daten benutzen kann. Untätigkeit des Request-Signals wird mit einer speziellen Time-out Schaltung ermittelt. Wenn über einen bestimmten Zeitraum kein Request-Signal auftritt, wird die Erzeugung des Taktsignales für den lokalen synchronen Block von einem lokalen Ringoszillator oder einem externen Takt übernommen. Dies dient dem Leeren interner Pipeline-stufen des synchronen Blocks.

Basierend auf diesem Konzept, wird eine praktische Hardware-Realisierung eines asynchronen Wrappers vorgeschlagen. Der asynchrone Wrapper besteht aus einigen Bestandteilen mit unterschiedlicher Komplexität und Struktur. Ein stimmbarer Ringoszillator taktet den lokalen synchronen Block. Dieser Ringoszillator verbraucht den größten Teil der Fläche des asynchronen Wrappers. Die Haupt-bestandteile sind Eingangsschaltung und Ausgangsschaltung, die als asynchrone endliche Zustands-automaten (AFSM) entwickelt wurden. Diese Schaltungen sollen die Hazard-freie Kommunikation zwischen unterschiedlichen GALS-Blöcken durchführen und die sichere Übertragung der Daten steuern. Im Allgemeinen benötigt der vollständige asynchrone Wrapper wenige tausend Gatter, die im Vergleich mit einer durchschnittlichen synchronen Blockgröße von einigen hunderttausend Gattern annehmbar ist. In der Arbeit besprechen wir auch eine alternative asynchrone Wrapper-Architektur, die auf externer Taktung basiert.

Die entwickelte Wrapper-Struktur wird auf das Design eines IEEE 802.11a kompatiblen Basisbandprozessors angewendet, um die Probleme System integration, Timing-closure, Clockskew, Leistungsaufnahme und elektromagnetische Störung (EMS) zu vermindern. Der Basisbandprozessor wird auf eine Anzahl unterschiedlicher GALS-Blöcke verteilt. Die Kriterien für die Aufteilung waren Energieeinsparung und natürliche Grenzen zwischen den unterschiedlichen Blöcken. Dann wurden lokal synchrone Blöcke mit passenden asynchronen Wrappern erweitert. Um den komplizierten Datenfluss zwischen den Blöcken zu steuern, werden einige zusätzliche Blöcke vorgeschlagen, die die Datenraten-Anpassung, das Aufteilen eines Datenstomes in mehrere Datenströme und die Kombination mehrerer Datenströme in einen einzigen realisieren. Zusätzlich war es erforderlich, bestimmte Kommunikationmuster mit der synchronen Umgebung zu garantieren. Aus diesem Grund wurden synchron-zu-asynchrone und asynchron-zu-synchrone Schnittstellen-Blöcke eingeführt. Für den Test wurde der GALS-Basisbandprozessor um Designfür-Testability (DFT) Logik erweitert, die auf einem eingebauten Selbsttest (BIST) basiert.

Der komplette Basisbandprozessor einschließlich GALS Wrapper wurde integriert, synthetisiert, und schließlich gefertigt. Implementierungsdetails werden hier beschrieben, um die Vorteile des vorgeschlagenen Konzeptes darzustellen. Zusätzlich wird eine Entwurfsmethodik für GALS-Systeme vorgeschlagen. Schließlich werden die Resultate der Messung dargestellt und diskutiert. Das GALS-Design wird mit einer synchronen Version des Basisbandprozessors verglichen, die Clock-Gating zur Energieeinsparung verwendet. Unsere Messungen ergaben eine Verringerung des dynamischen Energieverbrauchs um 1%, eine Verringerung von Versorgungsspannungsschwankungen um 30% und eine Reduktion des spektralen Rauschens um 5 dB.

Schlagwörter: GALS, System Integration, asynchroner Entwurf, EMI, BIST

### **Chapter 1**

## Introduction

#### **1.1 Design Challenges for Wireless Communication Systems**

Designing modern wireless communication systems is a very challenging task. The complexity of digital systems grows enormously, as can be noticed from the technology roadmap [ITRS03, MED02] in Table 1.1. We can conclude from the table that this trend will be continued in the following years. The increasing demands of wireless applications create several problems for system design and integration. The following issues will have the main importance in future: integration of complex systems, timing closure including clock generation and control, system noise characteristic, and power consumption for mobile applications.

| Year                                          |      |       |       |      |

|-----------------------------------------------|------|-------|-------|------|

| Property                                      | 1999 | 2001  | 2005  | 2011 |

| CMOS process [µm]                             | 0.18 | 0.15  | 0.1   | 0.05 |

| Transistors on chip [Mtrans/cm <sup>2</sup> ] | 7    | 14    | 41    | 247  |

| On-chip clock [GHz]                           | 1.25 | 1.77  | 3.5   | 10   |

| Off-chip clock [GHz]                          | 0.48 | 0.722 | 1.035 | 1.54 |

| Power dissipation (handheld systems) [W]      | 1.4  | 1.7   | 2.4   | 2.2  |

| Vdd [V]                                       | 1.5  | 1.2   | 0.9   | 0.5  |

Table 1.1 Technology roadmap from 1999 to 2011

When a complex digital system is designed, system integration and timing closure are very important tasks. A communication system usually contains blocks operating at different frequencies and even different supply voltages. Integration of such blocks requires advanced design techniques. An additional problem is the integration of prelayouted hardware IP-cores from different vendors for specific process technologies. Those blocks are individually tested, but embedding them into the system structure is often not trivial.

Most digital systems designed today operate synchronously. Consequently, one of the crucial problems is the construction of the clock tree. The clock tree in complex digital systems is not just a set of buffers, but it includes clock-gating supporting circuitry, clock dividers for different clock domains, PLLs and complex clock-phasing blocks. Difficulties in clock-tree generation may lead to a substantial slow-down of the design process. Even worse, in some cases it is not possible to design a functional global clock tree at all. Additionally, a designer may have big problems with other timing closure issues like: the appropriate setup and hold time requirements, a reset-tree generation, and control of the boundary timing between different clock domains.

Today's industrial trend is focussed on cost reduction by System-on-Chip (SoC) implementation with integration of digital and analog processing parts on a single chip. There are already products on the market that can be denoted as SoC systems. However, the noise level in the RF part of the circuit can be significantly increased due to interference by strong spectral components of the synchronous clock frequency and their harmonics. The synchronous global clock generates increased electromagnetic interference (EMI), which can lead to severe distortions and crosstalk in the analog domain.

One of the most important properties of a communication system is mobility. However, mobile communication systems have one very critical constraint – power consumption. The limited capacity of the batteries creates firm limits for the system power consumption. Furthermore, the power demands of complex systems are usually high and hence, power consumption must be controlled and minimised. Partly, this can be achieved by using known methods for minimisation and localisation of switching power like clock gating, asynchronous design or voltage scaling. However, clock gating makes the design of the clock tree even harder. Furthermore, mobile systems should support an "idle" mode of operation that deactivates most of the system functionalities and even completely switches off hardware blocks from power supply.

An additional issue is "time to market". The intensive growth on the communication systems market has been followed with rapid technological developments and increased competition between companies. Consequently, design cycle time has been reduced to only few months. For example, the expected design cycle in 1997 was 18-12 months and in the year 2002 this was expected to be reduced to 8-6 months [CHAN99]. Accordingly, all already described design problems have to be resolved rapidly and more or less automatically.

Most known integration concepts are oriented towards general system structures and are not optimized for particular applications. The optimization towards a specific application can lead to increased performance, as well as power and noise reduction. This fact justifies our research effort in this area.

For example, digital signal processing algorithms in communication systems can be implemented with general DSP processors or dedicated datapath oriented hardware. If the system is implemented as a dedicated datapath architecture, it usually contains complex circuit blocks that perform sophisticated arithmetic or trigonometric operations. For example, a wireless LAN modem complying with standard IEEE802.11a [IEEE99] requires an FFT/IFFT processor, Viterbi decoder, CORDIC processor as well as cross- and auto-correlators. Often those blocks have point-to-point communication using localised or distributed control. Typically, the communication between those blocks requires high datarates. In many cases, periods of high data throughput are followed by periods of long inactivity, thus causing bursty activity patterns. An optimal integration technique for this particular system can give much better results than the application of some general integration technique.

The described issues have to be investigated when a complex communication system is being implemented. There are several methods and tools for managing each challenge separately. However, there are almost no techniques which conceptually address most of these issues at the same time. From my point of view, GALS techniques have the potential to solve some of the most challenging design issues of SoC integration of communication systems in the future.

#### 1.2 GALS as a Solution for the System Integration Problem

The idea that system blocks can internally operate synchronously and communicate asynchronously is not novel. Already twenty years ago the first GALS proposal was formulated in [CHAP84]. However, this topic has been reconsidered many years later and it is currently in the focus of research. There are several GALS architectures that are proposed as an elegant solution for the problems described previously [YUN96, BOR97, MUT01, MOO00].

Usually, a GALS system consists of a number of locally synchronous modules each surrounded with an asynchronous wrapper. Communication between synchronous blocks is performed indirectly via asynchronous wrappers. The current level of GALS development offers a reliable framework for the implementation of complex digital systems. However, known GALS techniques may introduce drawbacks in performance, additional constraints in the system, and hardware overhead. On the other hand, all proposed GALS techniques are oriented toward some general architecture with sporadic and not too intensive data transfer on its interfaces. For datapath organised circuits, the known implementations of GALS do not fully utilise the potential of this technique.

There are several goals that we want to achieve with the introduction of GALS for communication systems. Firstly, the proposed GALS concept must guarantee fast and reliable transfer of large databursts between locally synchronous modules. The data-transfer must be possible at every clock cycle of the locally synchronous clock. The design-flow must be user-friendly and easily adoptable by a designer who is not familiar with asynchronous design. The construction of complex designs should be simpler than with the standard synchronous approach, and problems of timing closure and clock tree generation should be relaxed.

One of our main motivators is noise reduction inside the digital system. The global clock is the most important source of EMI. It is conceivable to conclude that if we decouple local blocks from the central clock source and connect them to different local clock generators, the spectral noise can be considerably reduced. Furthermore, we are aiming to reduce instantaneous supply current peaks. In order to deal with mixed-signal applications, this can be a powerful technique to decrease noise emission of the digital circuits. However, the noise reduction concept must not rely on the results of the GALSification only. Further improvements can be achieved with additional application of clock-jittering and clock-phasing.

Finally, mobile wireless communication systems' power consumption is limited by battery capacity. Therefore, a GALS design methodology should include power saving mechanisms. The goal is to completely integrate power saving mechanisms into the asynchronous wrappers. Consequently, GALSification would automatically introduce a certain power reduction. However, the power saving in GALS is based on the same assumptions as clock-gating in the synchronous design. The main idea is identical – lowering of switching activity by disabling the clock signal. Consequently, the results of power saving in GALS are expected to be close to the results achieved by clock-gating.

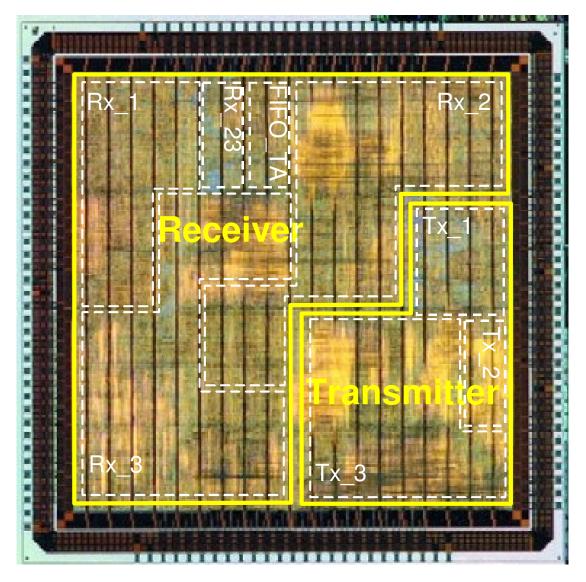

Based on the described motivation, in this thesis we will introduce a novel GALS concept and architecture, optimised for ASIC datapath structures, which are widely used in wireless communication systems. The complete spectrum of advantages and disadvantages of our proposed request-driven GALS technique can be seen best in a real complex datapath application. Our activity to work in the GALS area was initiated by the work on developing an IEEE 802.11a compliant modem. Therefore, a baseband processor for that standard appears to be the perfect candidate for introducing GALS. The baseband processor is a complex design (around 700k gates) with an internal datapath structure which includes sub-blocks such as Viterbi decoder, FFT/IFFT processor, and different CORDIC processors. Introducing the GALS technique in this baseband processor was a challenge and our results will be reported here.

#### 1.3 Structure of the Thesis

The thesis is structured in ten different chapters. In Chapter 2, the state-of-the-art in the GALS area is described. Moreover, some alternative approaches for complex digital system integration are

described. Then, a discussion of possible gains of GALS techniques is presented. The conclusion of this chapter contains a critical view on existing approaches and identifies possible drawbacks when applying these.

Chapter 3 gives the motivation for our new GALS technique as well as the main ideas and theoretical concepts of a request driven GALS technique. Accordingly, a global structure of the request-driven GALS system is suggested and the purpose of the main system components is described. Furthermore, the potential gain of the application of the proposed technique is evaluated. Finally, some directions on the possible adaptation of the proposed concept are sketched. A modified version of the wrapper which avoids local ring oscillators and uses an external clock instead is introduced.

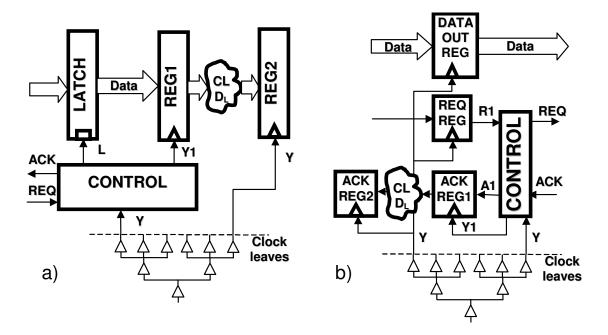

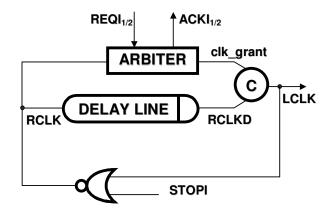

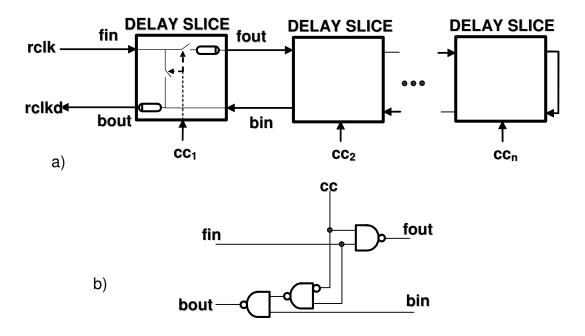

Furthermore, in Chapter 4, a possible request driven asynchronous wrapper implementation is proposed. The detailed structure of the asynchronous wrapper is shown. The main components of the wrapper are thoroughly discussed: pausable clock generator, clock control block, time-out generator, input port, output port, and mutual-exclusion element. Details on the formal analysis of the asynchronous wrapper are also included in this chapter. At the end of the chapter, a modified version of the asynchronous wrapper with external clocking is considered.

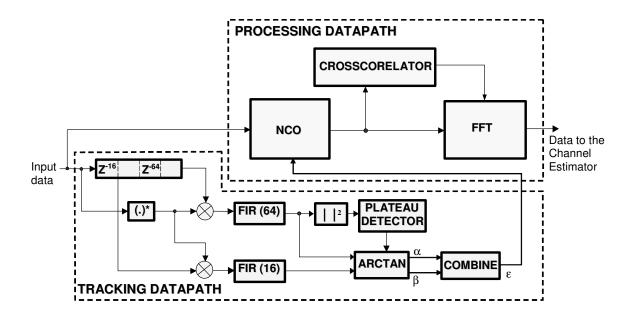

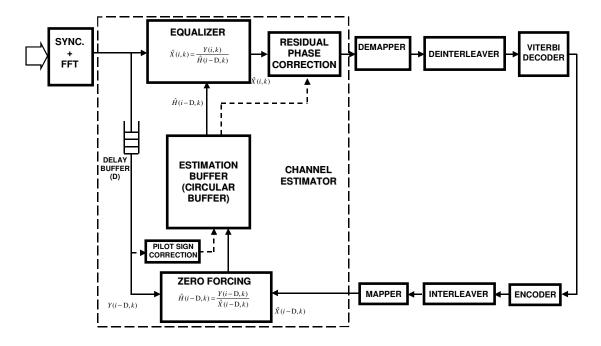

Chapter 5 is dedicated to the application of the proposed GALS technique in wireless communication system. The baseband processor for standard IEEE 802.11a is chosen as a verification platform for GALS. In this chapter, some details on the structure of the processor and a proposal for GALS partitioning is described. Special attention is paid to the power saving strategy in this system. Due to the complexity of the system, it was necessary to design several additional blocks as well as interfaces between synchronous and asynchronous blocks.

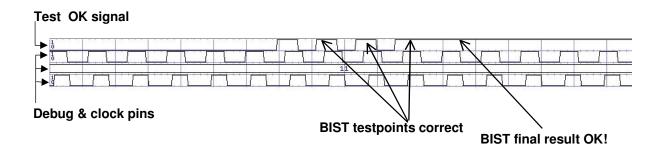

Modern digital systems must support effective ways of testing. Therefore, Chapter 6 is focused on testing and design for testability (DFT) of GALS systems. Different DFT techniques are evaluated. A test technique based on Built-in Self-Test (BIST) is proposed and the test structure is elaborated.

In Chapter 7 the current state of the design-flow, test flow and implementation details of asynchronous wrappers are given. Additionally, a complete GALS design framework is proposed. Our GALS technique is applied to the baseband processor, compliant with standard IEEE 802.11a. In this chapter all relevant details regarding this implementation are presented.

Chapter 8 reports the results of testing and measurement of the produced GALS baseband processor chip. Much attention is paid to answer the question how GALSification affected the power consumption. In addition to that, the power supply variation spectrum is measured and evaluated. All measurements include a comparison with the pure synchronous variant of the baseband processor.

Chapter 9 summarizes the achievements of this thesis and points to possible future challenges and solutions. Finally, Chapter 10 gives the references used in this thesis.

### **Chapter 2**

## Related Work – from Two-Flop Synchroniser to GALS Wrappers

#### 2.1 Introduction

System on Chip (SoC) integration imposes a number of technical challenges on designers and tools. The number of difficulties for the SoC implementation additionally grows in the area of wireless communication systems. The methods and tools for reducing power consumption and minimizing crosstalk between analog and digital parts of the system are very limited and often inefficient.

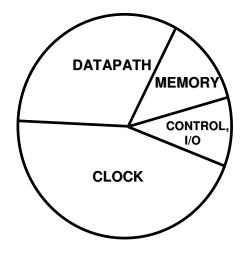

Many of the challenges are in conjunction with the design of the clock network in complex digital systems. Clock skew appears to be a severe bottleneck for high-performance digital circuits. The synchronous transitions of the clock lines are a strong source of noise and electro-magnetic interference (EMI). Additionally, the power spent just for running the clock tree is comparable to the power consumed in the functional blocks of the system. It is conceivable to conclude that splitting a complex digital system into several independent subsystems, will relax problems significantly. Dealing with smaller blocks is much simpler, and power saving techniques could be more successfully applied. Crosstalk and EMI are suppressed due to the uncorrelated operation of the autonomous blocks. However, synchronisation between blocks operating at the different speed could be very complicated.

Several existing approaches address the problem of block partitioning and data synchronisation between independent blocks. Some of them are used to deal with increased power consumption and EMI. Today, these techniques are mainly referred to as Globally Asynchronous Locally Synchronous (GALS) methods. Many of them are effectively not applicable. However, some of the techniques are actually present in the design practice. Choosing between different proposed strategies depends very much on the particular system architecture.

In the following chapter, different synchronisation and integration schemes will be described. Hereupon, advantages and disadvantages of those techniques will be discussed. Additionally, some open points and issues not covered by the proposed techniques will be pointed out. Finally, directions for possible activities in the area of synchronisation and GALS will be suggested.

#### 2.2 System Integration Strategies

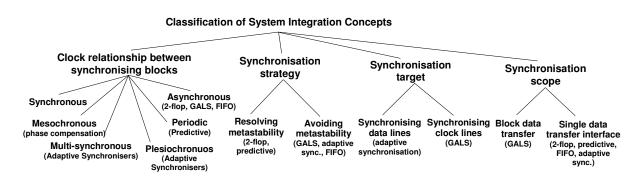

There is a long history of approaches that guarantee safe communication between blocks that do not share the same common clock. In general, most of such systems rely on synchronous operation of the local blocks, and asynchronous communication is based on handshakes between them. All these systems could be referred to as Globally Asynchronous Locally Synchronous (GALS) systems. However, in the literature only one subset of the related approaches is actually referred as "GALS". The "GALS" techniques are usually oriented toward providing a complete infrastructure for data transfer between the complex synchronous blocks and include pausable clocks as local triggers. On the other hand, there are many other approaches that aim to provide prerequisites for safe data transfer. In Figure 2.1, a classification of system integration concepts is given.

Figure 2.1. Classification of system integration methods

The first classification parameter is the relationship between the clocks of the synchronous modules that we want to integrate [GIN02]. In this context, a system can be synchronous (and no synchronisation is required); mesochronous when there is a fixed phase difference but same frequency of the different system blocks (in this case, a phase compensation can solve the problem); multi-synchronous or plesiochronous when the phase varies or there is a very small difference in frequency between the local blocks (adaptive synchronisation can be used for those cases); periodic (predictive synchronisers are used); or asynchronous (when classical 2-flop synchronisers, FIFO or GALS solutions are applied).

Furthermore, system integration techniques can avoid metastability (like in GALS or FIFO technique) or try to resolve from the metastable state (as in 2-flop or predictive synchronisers). An additional parameter can be the target for synchronisation. On one hand we can synchronise data

lines (as in adaptive synchronisation), and on the other hand, the clock lines can be synchronised (as in GALS).

Finally, the integration approaches can be categorized on the basis of synchronisation scope. Two main groups can be defined: the first that controls all existing data transfers from a single block to all other connecting blocks (the examples are GALS techniques), and the other that focuses only on particular interfaces for data transfer from block A to block B (this approach is used in all other "non-GALS" solutions).

In the following text I will first describe some of the interesting "non-GALS" proposals and then different "GALS" techniques and systems.

#### 2.2.1 Standard Synchronisers

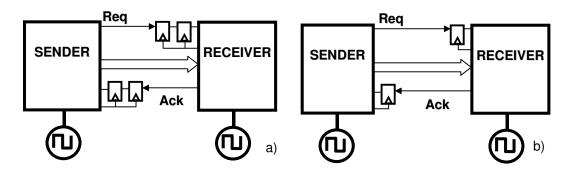

To avoid metastability and perform safe data transfer between asynchronously communicating blocks, it is possible to implement standard synchronisers based on a cascade of registers. These schemes are already known and successfully used for decades. A standard solution is to use two-flop synchronisers (Figure 2.2a) or, as a minimum, one-flop synchronisers (Figure 2.2b) [GIN03]. As can be seen from Figure 2.2, synchronised handshake is being performed to transfer data. In order to avoid metastability problems a number of flip-flops is inserted to synchronise the request (*Req*) and acknowledge (*Ack*) signals.

Figure 2.2. Two-flop (a) and one-flop (b) synchroniser

In general, the parameter that defines the synchroniser characteristics is Mean Time Between Failures (MTBF) [GIN03, DIKE99]:

$$MTBF = \frac{e^{T/\tau}}{T_w f_a f_D}$$

where  $\tau$  is the settling time constant of the flop, T a settling window,  $T_W$  a time window of susceptibility,  $f_a$  the synchroniser 's clock frequency, and  $f_D$  the frequency of data transfer.

The technique that uses a two-flop synchroniser is very safe, and the probability of a failure is negligible. As an example, we calculated MTBF for 0.25  $\mu$ m CMOS technology, with a clock frequency of 80 MHz and data transfer every 8<sup>th</sup> cycle. In this case, the MTBF can be estimated as 10<sup>258</sup> years. Unfortunately, a two-flop synchroniser adds several clock cycles latency, which could be unacceptable for high-speed data communication. A one-flop synchroniser (Figure 2.2b) adds less latency in the communication channel, but decreases MTBF by reduction of the settling window *T*. To conclude, application of standard synchronisers is justified for low-speed data-transfer between independent hardware blocks. For high-speed purposes, some other scheme must be used.

#### 2.2.2 Adaptive Synchronisation

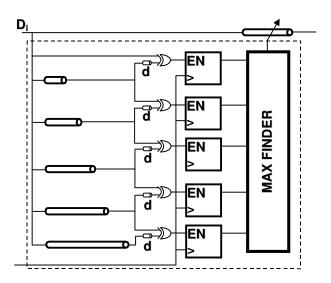

As an alternative, the adaptive synchronisation techniques [KOL98] could be used for mesochronous systems. Mesochronous systems are using clock sources with exactly the same frequency but unknown, constant phase shift between different blocks. The general scheme of an adaptive synchroniser is shown in Figure 2.3. The main idea behind this approach is to delay data lines as much as it is needed in a particular moment, in order to avoid metastability.

Figure 2.3. Adaptive synchroniser

Additional circuitry is needed to estimate the delay margin needed. For that purpose, a statistical phase detector is used, as shown in Figure 2.3. The role of this circuit is to perform measurements on a statistical basis and to find the delay within one clock period that corresponds to the lowest risk of metastability. The measurement is performed such that several counters count the number of ones at the outputs of the corresponding XOR gates. Every XOR gate should calculate the difference between the instantaneous data input and the same data input delayed by some fraction of the clock period. A configuration as shown in Figure 2.3 uses delay increments of T/5. After a long calibration time, some of the counters should show significantly higher values than the others. This will indicate that for the corresponding values of data delay, the risk of metastability will be very high. On the other hand, if we

choose a data delay that corresponds to the counter with the lowest stored value, this risk will be low. The statistical measurement is usually performed when the system is not in operation. These calibration periods are referred as *training sessions*. The duration of the training session is estimated to be around 100000 cycles in order to generate a representative statistical model of the data delay. Training sessions must be performed after reset and can be repeated periodically in order to keep track with PVT (Power, Voltage, Temperature) changes.

When the most suitable delay value for a data line is found, a tunable delay circuit connected to the corresponding data line is programmed. This way, the probability of metastability can be reduced to some degree, which is sufficient for most practical applications. However, this approach does not offer any power saving mechanism and introduces a relatively large hardware overhead, because a separate delay line is needed for every single data line. Also, the time overhead needed for statistical analysis of the data could be important. On the other hand, this solution could be accepted in the case of mesochronous communication between blocks. For the data transfer between blocks operating at different clock speed, this approach cannot be applied.

Researchers from Technion in Haifa, Israel have recently formulated an optimized solution [FRA04] for the same problem. This paper proposes the use of a *Two-way Adaptive Predictive Synchroniser* for mesochronous operation. The synchronisation latency is smaller than one clock cycle. However, even with providing a possibility for high-speed data-transfer between clock domains, this technique is restricted to mesochronous systems and adds a significant amount of hardware overhead.

#### 2.2.3 FIFO Synchronisation

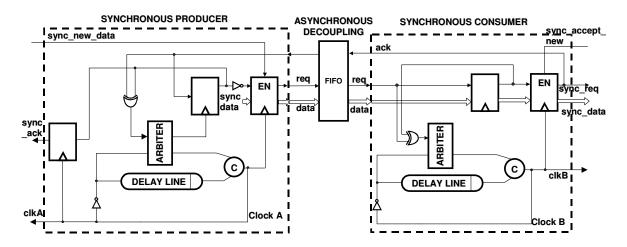

Another possible approach is interfacing blocks with specially designed asynchronous FIFO buffers. Consequently, hardware redundancy of the FIFO hides the problem of the synchronisation in the system. Such a system can tolerate very large interconnect delays and is also quite robust with regard to metastabillity. It can be used for interconnection of asynchronous and synchronous systems, but also for synchronous-synchronous and asynchronous-asynchronous connections. Acceptable data throughput via such an interface can be achieved [CHE01, CHE00a, CHE00b]. Additionally to the data cells, the FIFO structure includes the full and empty detector as well as a special deadlock detector. The advantage of FIFO synchronisers is that the operation of the locally synchronous module is not affected by synchronisation. However, with very wide interconnect data buses, FIFO structures could be very expensive in terms of area. Also, the introduced latency might be significant and possibly not acceptable for high-speed applications. In the experiment described in [IYE02], the application of the proposed FIFO structure in a 5-clock domain GALS processor caused a performance drop in the range of 5 to 15 %.

Another interesting approach in the area of FIFO synchronisation is the STARI technique that was presented in [CHAK99]. This technique is based on a self-timed FIFO that compensates clock skew

between different clock domains. However, this approach can lead to a significant performance loss when large data bursts have to be transferred.

#### 2.2.4 GALS Systems

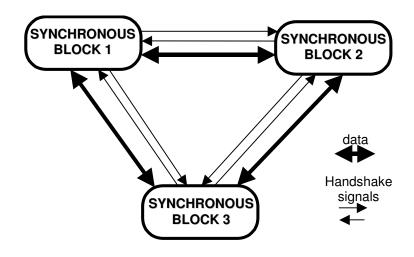

Although all previous systems in general could be referred as GALS systems, usually this term is only used for systems that offer a complete design framework. GALS systems have a unique structure that is similar for all the different proposals. The principle architecture of GALS is given in Figure 2.4. Locally synchronous modules are usually surrounded by asynchronous wrappers. Local clocks drive those synchronous circuit blocks. Stoppable ring oscillators are frequently used to generate the local clocks. Data transfer between different blocks requires stopping of the local clocks during data-transfer in order to avoid metastability problems. The asynchronous wrappers should perform all necessary activities for safe data transfer between the blocks. Locally synchronous modules do not play any role in providing the prerequisites for block-to-block data transfer.

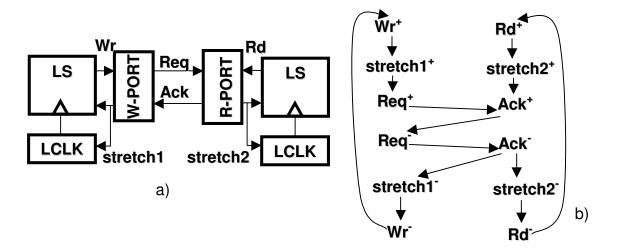

GALS as a technique was for the first time investigated in [CHAP84]. In this thesis, the fundamental basis of globally asynchronous locally synchronous systems was given. Although the circuitry described there cannot be successfully applied to modern high-speed digital systems, the ideas given there are even today very interesting. Use of stretched clocks, for example, is the basic idea behind this work, and is used in most modern GALS proposals.

Figure 2.4. GALS architecture

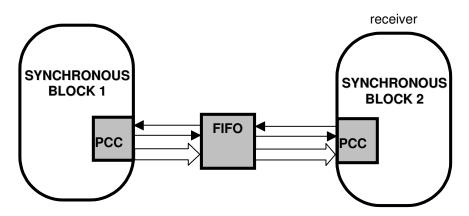

Many years after the first proposal, the GALS idea has been reactivated and a working architecture is described in [YUN96, YUN99b]. This solution is based on pausable clocks in order to prevent metastability. To increase the throughput, an asynchronous FIFO is added to this circuitry as depicted in Figure 2.5.

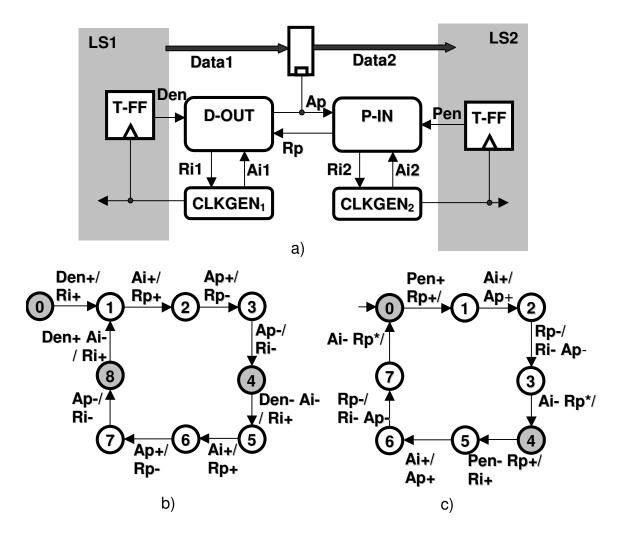

Figure 2.5. Two synchronous modules communicating via an asynchronous channel

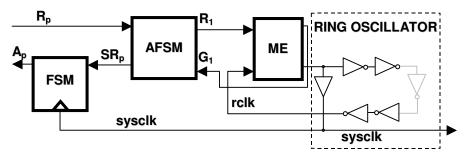

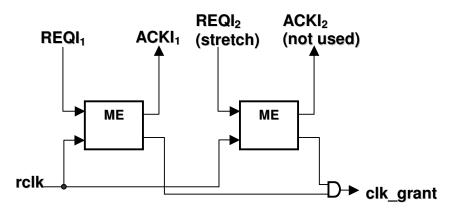

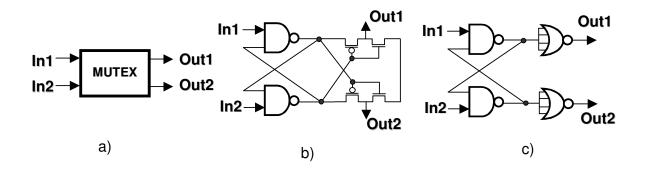

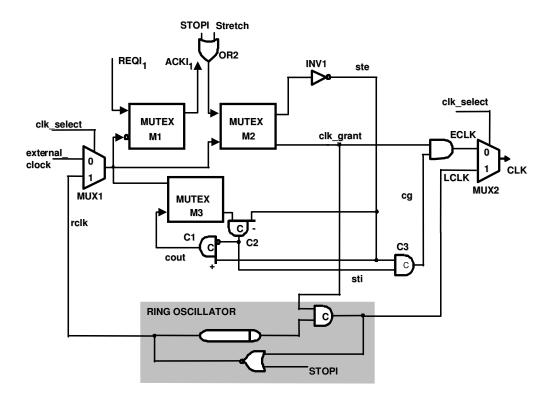

The clock signal is controlled by a pausable clocking control (PCC) circuit given in Figure 2.6. A fundamental problem of the GALS technique is a prevention of the simultaneous appearance of the incoming request and the local clock. Consequently, for the purposes of arbitration a mutual exclusion element (ME) is used (Figure 2.6). Therefore, when the clock signal is high, an incoming request will not be processed until the clock is released. Also, when the request is asserted, the rising clock for the locally synchronous module will be delayed until the request is released. If both events appear at the same moment, the mutual exclusion circuit will "toss the coin" and grant just one of its outputs. Consequently, either the next clock cycle will be granted or a data transfer handshake. In this way, asynchronous data transfer between two blocks can be performed safely. The PCC controller is equipped with an AFSM for supporting the asynchronous handshake protocol, and additionally, with a synchronous FSM that should synchronise the acknowledge signal *Ap* to the local system clock *sysclk*. A major drawback is the limitation to transfer only one data item every other clock cycle. Additionally, multi-port applications will lower the maximum throughput. Therefore, this solution results in poor performance for data-transfer intensive multi-channel systems.

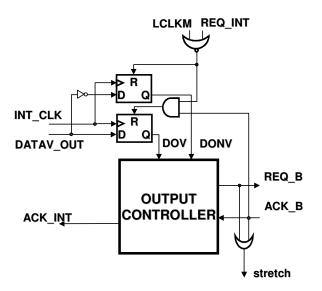

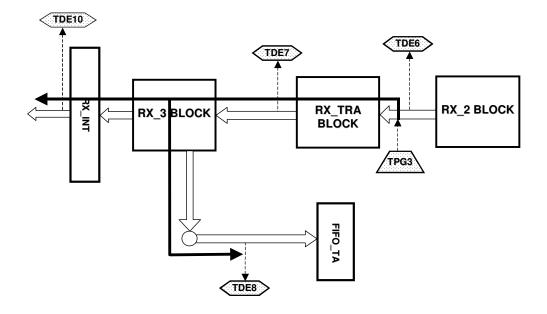

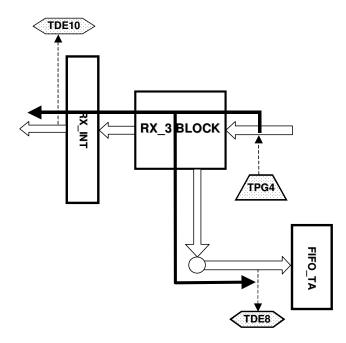

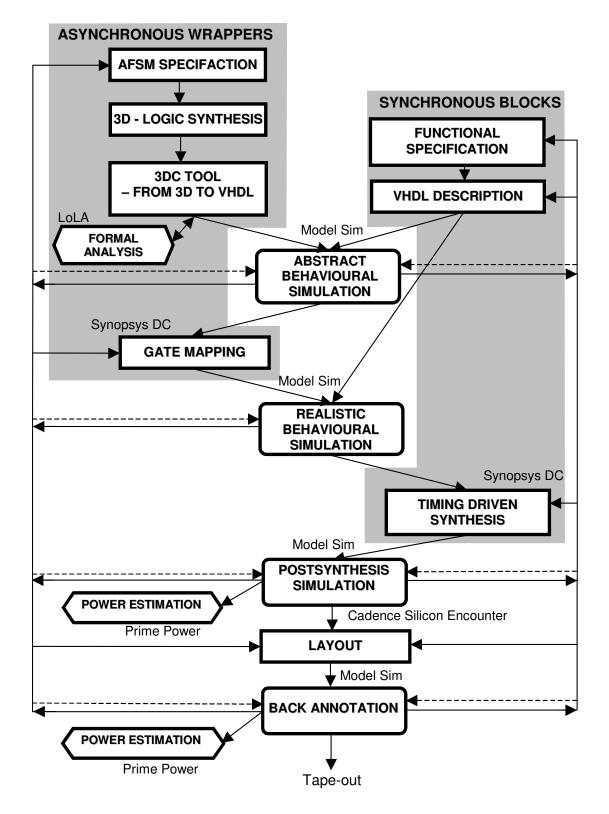

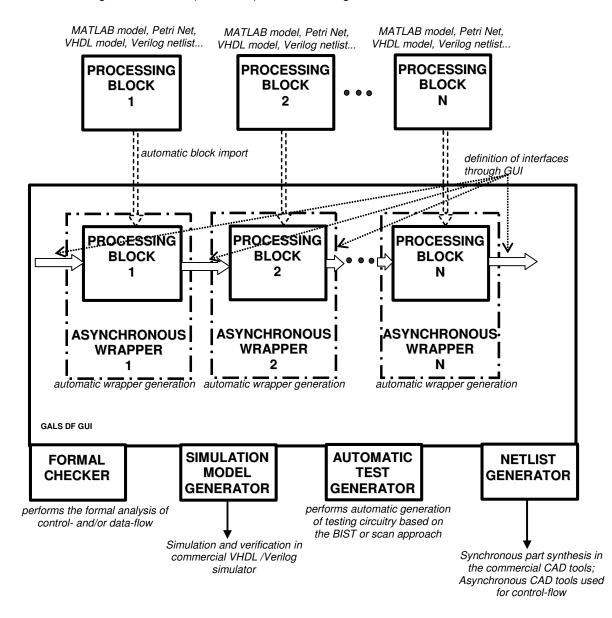

Figure 2.6. Pausable clock control (PCC) circuitry