# Mechanisms for Energy-Efficient Processor Allocation and Redistribution on Manycore Systems

Von der Fakultät 1 - MINT - Mathematik, Informatik, Physik, Elektro- und Informationstechnik der Brandenburgischen Technischen Universität Cottbus-Senftenberg genehmigte Dissertation zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften (Dr.-Ing.)

vorgelegt von

Master of Science (M.Sc.)

Philipp Gypser

geboren am 10.07.1990 in Cottbus

| Vorsitzender: | Dr. M. Reichenbach               |  |  |

|---------------|----------------------------------|--|--|

| Gutachter:    | Prof. Dr. J. Nolte               |  |  |

| Gutachter:    | Prof. Dr. W. Schröder-Preikschat |  |  |

| Gutachter:    | Prof. Dr. A. Polze               |  |  |

Tag der mündlichen Prüfung: 04.05.2023

**DOI:** https://doi.org/10.26127/BTU0pen-6385

# Abstract

Multi- and manycore processors promise to combine high overall peak performance with moderate power consumption to meet the constantly growing demand for computational power under the energy constraints of today's CMOS technology. Future systems with manycore processors are expected to contain a huge amount of cores, which exceeds the number of processes that will run simultaneously. Consequently, processor time sharing approaches, that introduce significant overhead from regular context switches in common Operating Systems, will no longer be necessary.

This work investigates mechanisms for scalable and energy-efficient spatial partitioning of multi- and manycore processor systems. In addition, it explores the implications of exclusive processor core allocation to user processes due to the absence of temporal multiplexing and offers approaches to ease the adaptation to the new programming model.

The proposed mechanisms achieved fast thread allocation which motivates applications for dynamic thread allocation and benefits performance as well as energy efficiency. The efficiency control and resource revocation mechanisms detect and prevent wasteful and inefficient resource occupation from poorly optimized or malicious processes. In this way, the global efficiency of the system is optimized. The dynamic processing resource allocation and revocation handling has been integrated into a task parallel runtime system, to disburden the application programmer from manual implementation and to increase productivity.

# Zusammenfassung

Mehrkern- und Vielkernprozessoren versprechen eine hohe Spitzenrechenleistung bei moderatem Stromverbrauch, um den ständig wachsenden Bedarf nach Rechenleistung mit den Energiebeschränkungen der heutigen CMOS-Technologie zu erfüllen. Es wird erwartet, dass zukünftige Systeme mit Vielkernprozessoren eine riesige Anzahl von Rechenkernen enthalten werden, welche die Anzahl der gleichzeitig laufenden Prozesse übersteigt. Folglich werden Ansätze für das zeitliche Multiplexing der Prozessoren, die in bestehenden Betriebssystemen erhebliche Kosten durch regelmäßige Kontextwechsel verursachen, nicht mehr zwingend erforderlich sein.

Diese Arbeit untersucht Mechanismen für eine skalierbare und energieeffiziente räumliche Partitionierung von Mehrkern- und Vielkernprozessorsystemen. Darüber hinaus werden die Auswirkungen der exklusiven Prozessorkernzuweisung, aufgrund des fehlenden zeitlichen Multiplexings, für den Benutzer untersucht und Ansätze zur Erleichterung der Anpassung an das neue Programmiermodell angeboten.

Die entwickelten Mechanismen erreichen eine schnelle Threadallokation, die Anwendungen zur dynamischen Ressourcenbelegung motiviert und damit sowohl die Rechenleistung als auch die Energieeffizienz erhöht. Die Mechanismen zur Effizienzkontrolle und zum Entzug von Ressourcen erkennen und verhindern eine verschwenderische und ineffiziente Ressourcenbelegung durch schlecht optimierte oder bösartige Prozesse. Auf diese Weise wird die globale Effizienz des Systems verbessert. Die dynamische Belegung von Rechenressourcen und die Behandlung von Ressourcelimitierungen wurden in ein aufgabenparalleles Laufzeitsystem integriert, um Anwendungsprogrammierer von der manuellen Implementierung zu entlasten und die Produktivität zu steigern.

# Contents

| 1 | Intr | Introduction 1    |                                                                    |    |  |  |  |

|---|------|-------------------|--------------------------------------------------------------------|----|--|--|--|

|   | 1.1  | Problem Statement |                                                                    |    |  |  |  |

|   | 1.2  | Main (            | Contributions                                                      | 4  |  |  |  |

|   | 1.3  | Struct            | ure of this Thesis                                                 | 4  |  |  |  |

| 2 | Bac  | kground           | d                                                                  | 7  |  |  |  |

|   | 2.1  | Multi             | and Manycore Architectures                                         | 7  |  |  |  |

|   |      | 2.1.1             | Core Composition                                                   | 8  |  |  |  |

|   |      | 2.1.2             | Multithreading                                                     | 8  |  |  |  |

|   |      | 2.1.3             | Tiling                                                             | 10 |  |  |  |

|   |      | 2.1.4             | NoC Topology                                                       | 11 |  |  |  |

|   | 2.2  | Dynan             | nic Power Management in Multi- and Manycore Processors             | 11 |  |  |  |

|   |      | 2.2.1             | Energy Dissipation in CMOS Processors                              | 12 |  |  |  |

|   |      | 2.2.2             | Dynamic Power Consumption Reduction Techniques                     | 12 |  |  |  |

|   |      | 2.2.3             | Processor Power Management from the Operating System's Perspective | 13 |  |  |  |

|   |      | 2.2.4             | Dynamic Performance Boosting                                       | 16 |  |  |  |

|   | 2.3  | Opera             | ting System Processor Allocation                                   | 16 |  |  |  |

|   |      | 2.3.1             | Intra-Program Scalability                                          | 17 |  |  |  |

|   |      | 2.3.2             | Optimization Criteria                                              | 19 |  |  |  |

|   |      | 2.3.3             | Processor Multiplexing                                             | 21 |  |  |  |

|   |      | 2.3.4             | Spatial Processor Partitioning                                     | 23 |  |  |  |

|   |      | 2.3.5             | Application Profiling                                              | 27 |  |  |  |

|   |      | 2.3.6             | Linux                                                              | 30 |  |  |  |

|   |      | 2.3.7             | iRTSS                                                              | 31 |  |  |  |

|   |      | 2.3.8             | MyThOS                                                             | 34 |  |  |  |

|   | 2.4  | Thread            | d Management in Parallel Runtime Systems                           | 36 |  |  |  |

|   |      | 2.4.1             | OpenMP                                                             | 36 |  |  |  |

|   |      | 2.4.2             | Intel Threading Building Blocks                                    | 36 |  |  |  |

|   | 2.5  | Conclu            | usion                                                              | 37 |  |  |  |

| 3 | Ene  | rgy-Effi          | cient Processor Allocation on Multi- and Manycore Systems          | 39 |  |  |  |

|   | 3.1  | Analog            | gy to Memory Management                                            | 39 |  |  |  |

|   |      | 3.1.1             | Abstraction                                                        | 40 |  |  |  |

|   |     | 3.1.2  | Virtualization                                                     | 41              |

|---|-----|--------|--------------------------------------------------------------------|-----------------|

|   |     | 3.1.3  | Replacement                                                        | 42              |

|   |     | 3.1.4  | Working Set                                                        | 42              |

|   |     | 3.1.5  | Fragmentation                                                      | 43              |

|   |     | 3.1.6  | Resource Quality                                                   | 43              |

|   | 3.2 | Requir | rements and Assumptions                                            | 43              |

|   |     | 3.2.1  | Hardware Model                                                     | 43              |

|   |     | 3.2.2  | Application Model                                                  | 44              |

|   |     | 3.2.3  | Partitioning and Allocation Mechanism                              | 44              |

|   |     | 3.2.4  | Profiling and Redistribution                                       | 45              |

|   |     | 3.2.5  | Flexible Task-Parallel Runtime System                              | 46              |

|   | 3.3 | Hierar | chical Processor Allocation                                        | 46              |

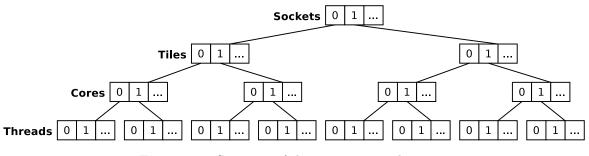

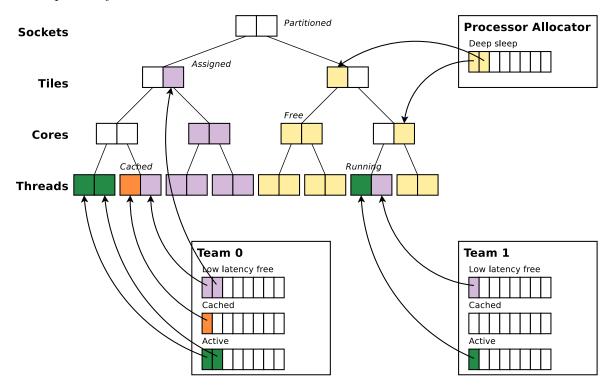

|   |     | 3.3.1  | Processor Topology Tree                                            | 46              |

|   |     | 3.3.2  | Resource Management Approaches                                     | 47              |

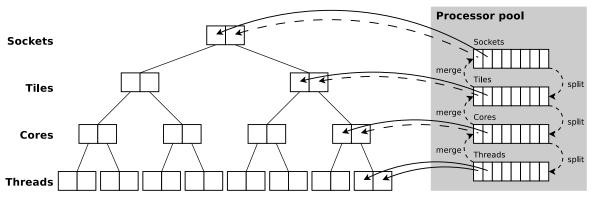

|   |     | 3.3.3  | Hierarchical Processor Pools                                       | 48              |

|   |     | 3.3.4  | Pool Balancing Strategy                                            | 50              |

|   |     | 3.3.5  | Placement Strategy                                                 | 52              |

|   | 3.4 | Applic | cation Profiling and Processor Redistribution                      | 55              |

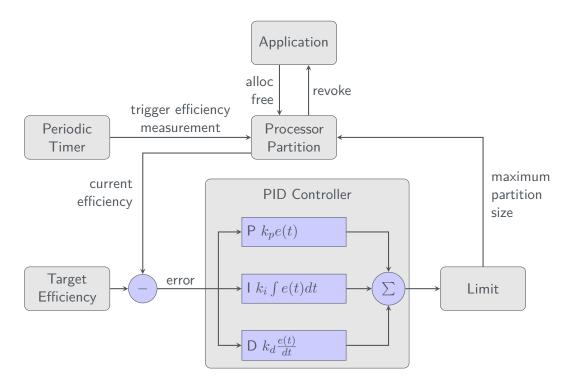

|   |     | 3.4.1  | Online Application Profiling                                       | 56              |

|   |     | 3.4.2  | Processor Revocation                                               | 60              |

|   | 3.5 | Dynar  | nic Processor Allocation in Task-based Parallel Runtime Systems $$ | 61              |

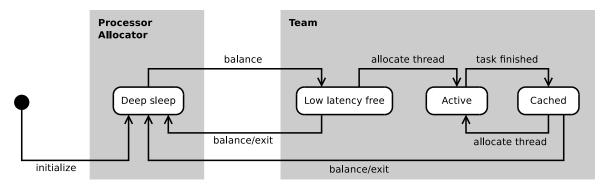

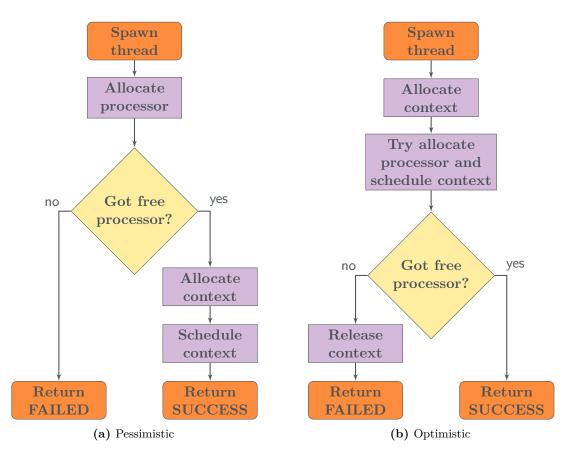

|   |     | 3.5.1  | Dynamic Thread Allocation                                          | 61              |

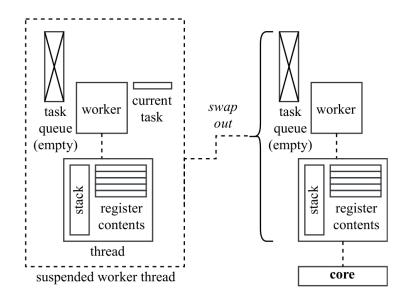

|   |     | 3.5.2  | Worker Suspension                                                  | 63              |

|   |     | 3.5.3  | Worker Resumption                                                  | 65              |

|   | 3.6 | Summ   | ary                                                                | 67              |

| 4 | l   |        |                                                                    | 60              |

| 4 | •   | Drease |                                                                    | <b>69</b><br>69 |

|   | 4.1 |        |                                                                    |                 |

|   |     | 4.1.1  |                                                                    | 70<br>71        |

|   |     | 4.1.2  |                                                                    | 71              |

|   | 4.0 | 4.1.3  |                                                                    | 73<br>76        |

|   | 4.2 |        | 0                                                                  | 76<br>77        |

|   | 4.3 | Ū.     |                                                                    | 77<br>70        |

|   |     | 4.3.1  |                                                                    | 78<br>70        |

|   |     | 4.3.2  | Worker Suspension and Resumption                                   | 79              |

| 5 | Evaluation |                                                                                           |                                                                   |     |  |  |  |

|---|------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|--|--|--|

|   | 5.1        | Measuring the Idle State Power Consumption and Wakeup Latency of a Real                   |                                                                   |     |  |  |  |

|   |            | Syster                                                                                    | n                                                                 | 81  |  |  |  |

|   |            | 5.1.1                                                                                     | Evaluation System                                                 | 82  |  |  |  |

|   |            | 5.1.2                                                                                     | Accurate Time Measurement on Multi-Core Processors                | 83  |  |  |  |

|   |            | 5.1.3                                                                                     | Power Measurement using RAPL                                      | 83  |  |  |  |

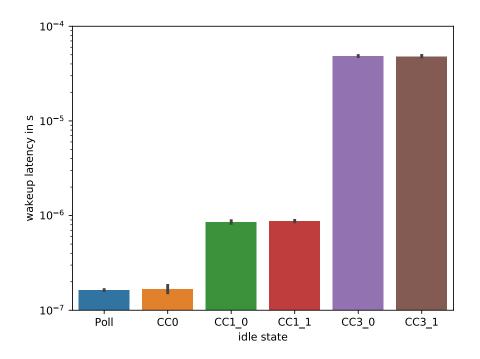

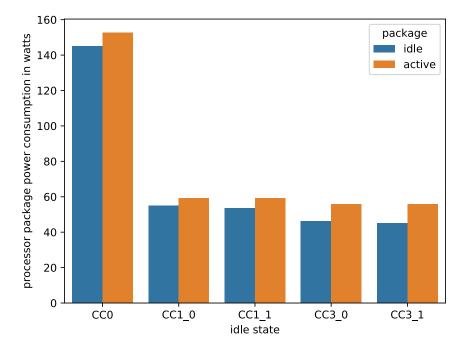

|   |            | 5.1.4                                                                                     | Experimental Measuring of Wakeup Latency                          | 84  |  |  |  |

|   |            | 5.1.5                                                                                     | Energy Consumption                                                | 86  |  |  |  |

|   |            | 5.1.6                                                                                     | Conclusion                                                        | 87  |  |  |  |

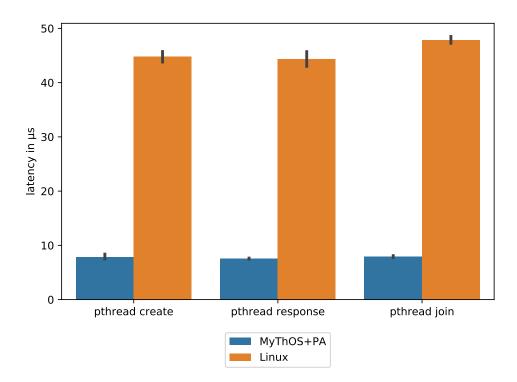

|   | 5.2        | Thread Allocation Latency                                                                 |                                                                   |     |  |  |  |

|   |            | 5.2.1                                                                                     | Setup                                                             | 88  |  |  |  |

|   |            | 5.2.2                                                                                     | Expectations                                                      | 89  |  |  |  |

|   |            | 5.2.3                                                                                     | Results                                                           | 90  |  |  |  |

|   |            | 5.2.4                                                                                     | Conclusion                                                        | 90  |  |  |  |

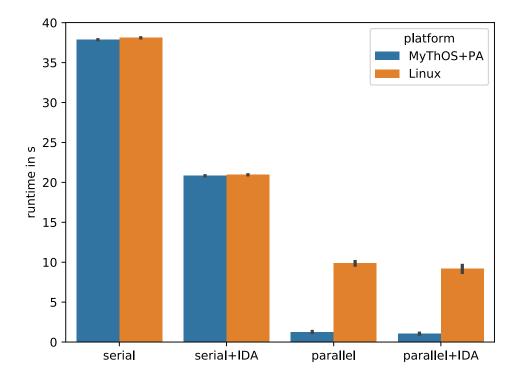

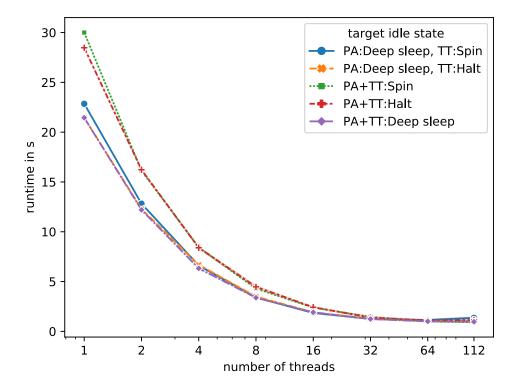

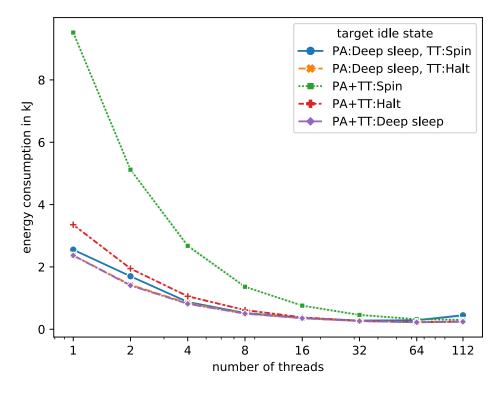

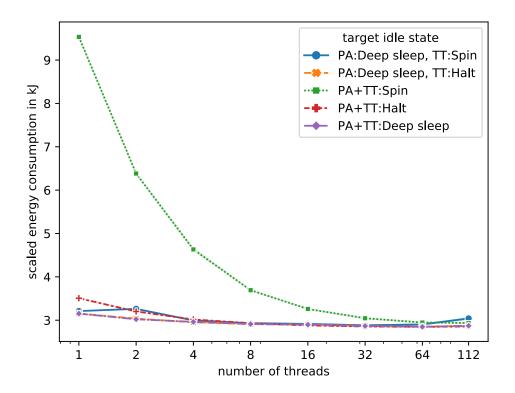

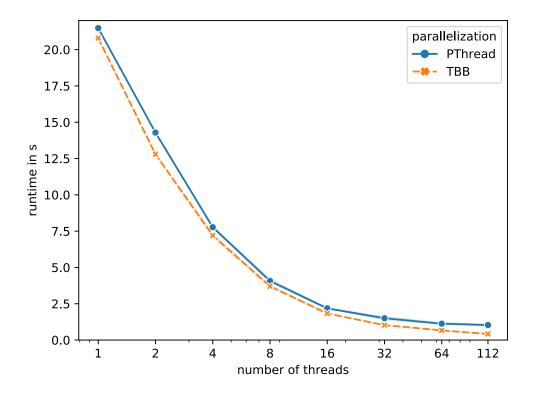

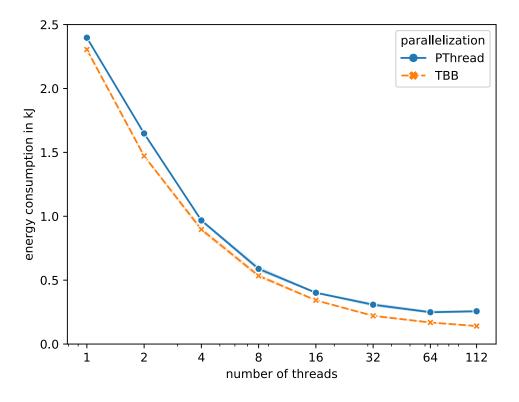

|   | 5.3        | Evalua                                                                                    | ation of the Energy Consumption and Execution Time on the Example |     |  |  |  |

|   |            | of a M                                                                                    | Iandelbrot Set Rendering Application                              | 91  |  |  |  |

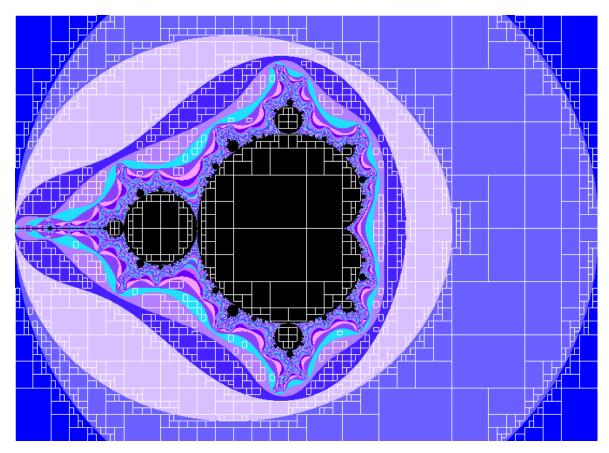

|   |            | 5.3.1                                                                                     | Mandelbrot Set Benchmark Application                              | 92  |  |  |  |

|   |            | 5.3.2                                                                                     | Setup                                                             | 93  |  |  |  |

|   |            | 5.3.3                                                                                     | Expectations                                                      | 94  |  |  |  |

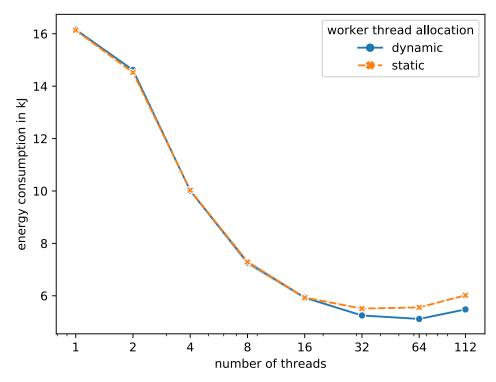

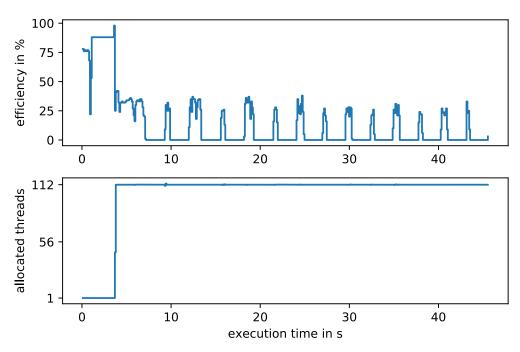

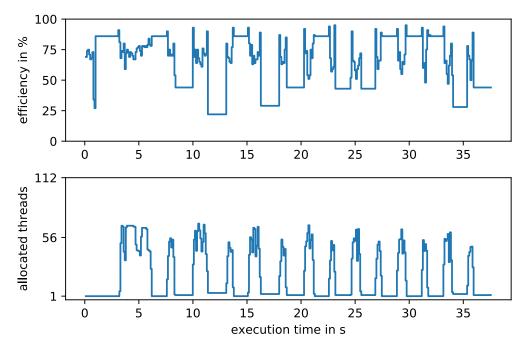

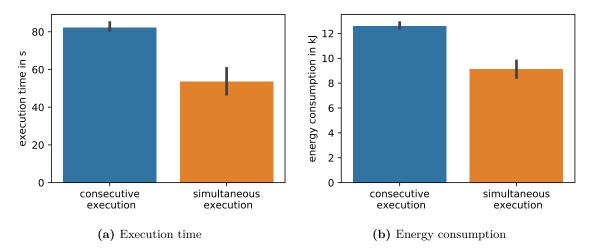

|   |            | 5.3.4                                                                                     | Results                                                           | 95  |  |  |  |

|   |            | 5.3.5                                                                                     | Conclusion                                                        | 102 |  |  |  |

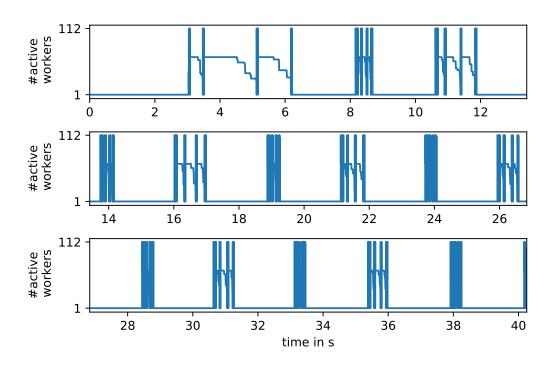

|   | 5.4        | Automated Processing Resource Allocation in the Parallel Runtime System $% \mathcal{A}$ . |                                                                   |     |  |  |  |

|   |            | 5.4.1                                                                                     | Setup                                                             | 103 |  |  |  |

|   |            | 5.4.2                                                                                     | Expectations                                                      | 105 |  |  |  |

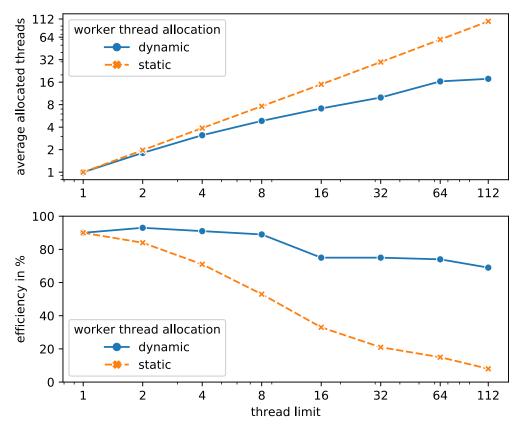

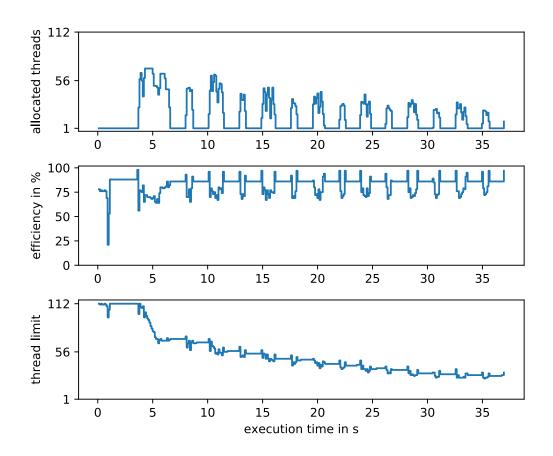

|   |            | 5.4.3                                                                                     | Results                                                           | 105 |  |  |  |

|   |            | 5.4.4                                                                                     | Conclusion                                                        | 106 |  |  |  |

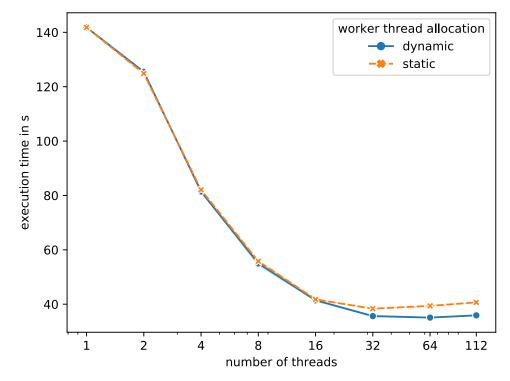

|   | 5.5        | Impac                                                                                     | et of Dynamic Resource Allocation in Parallel Runtime Systems on  |     |  |  |  |

|   |            | Performance and Energy Efficiency                                                         |                                                                   |     |  |  |  |

|   |            | 5.5.1                                                                                     | Setup                                                             | 109 |  |  |  |

|   |            | 5.5.2                                                                                     | Expectations                                                      | 110 |  |  |  |

|   |            | 5.5.3                                                                                     | Results                                                           | 111 |  |  |  |

|   |            | 5.5.4                                                                                     | Conclusion                                                        | 114 |  |  |  |

|   | 5.6        | Resource Efficiency Control through Online Application Profiling and Resource             |                                                                   |     |  |  |  |

|   |            | Revoc                                                                                     | ation                                                             | 115 |  |  |  |

|   |            | 5.6.1                                                                                     | Setup                                                             | 115 |  |  |  |

|   |            | 5.6.2                                                                                     | Expectations                                                      | 117 |  |  |  |

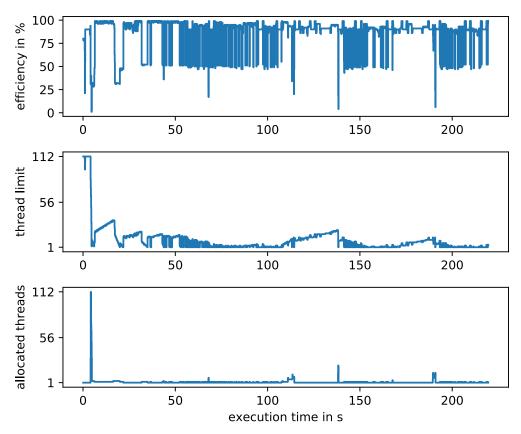

|     |                           | 5.6.3                                                                | Results                                                                                         | 118 |  |  |  |

|-----|---------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|--|--|--|

|     | 5.6.4 Conclusion $\ldots$ |                                                                      |                                                                                                 |     |  |  |  |

|     | 5.7                       | 7 Optimizing Energy Efficiency using Dynamic Resource Redistribution |                                                                                                 |     |  |  |  |

|     |                           | 5.7.1                                                                | Setup                                                                                           | 124 |  |  |  |

|     |                           | 5.7.2                                                                | Expectations                                                                                    | 125 |  |  |  |

|     |                           | 5.7.3                                                                | Results                                                                                         | 125 |  |  |  |

|     |                           | 5.7.4                                                                | Conclusion                                                                                      | 125 |  |  |  |

|     | 5.8                       | Summ                                                                 | ary                                                                                             | 126 |  |  |  |

| 6   | Con                       | clusion                                                              |                                                                                                 | 129 |  |  |  |

| Α   | Enei                      | rgy Diss                                                             | sipation in CMOS Processors                                                                     | 133 |  |  |  |

|     | A.1                       | Static                                                               | Power Consumption                                                                               | 133 |  |  |  |

|     | A.2                       | Dynan                                                                | nic Power Consumption                                                                           | 134 |  |  |  |

|     |                           | A.2.1                                                                | Transient Power Consumption                                                                     | 134 |  |  |  |

|     |                           | A.2.2                                                                | Capacitive-Load Power Consumption                                                               | 135 |  |  |  |

| в   | CPL                       | J Instru                                                             | ctions for Entering Idle States                                                                 | 137 |  |  |  |

|     | B.1                       | HLT (                                                                | Halt) $\ldots$ | 137 |  |  |  |

|     | B.2                       | MONI                                                                 | TOR/MWAIT                                                                                       | 137 |  |  |  |

|     | B.3                       | Intel's                                                              | UMONITOR/UMWAIT                                                                                 | 138 |  |  |  |

|     | B.4                       | AMD's                                                                | s MONIORX/MWAITX                                                                                | 138 |  |  |  |

|     | B.5                       | PAUSI                                                                | Ε                                                                                               | 138 |  |  |  |

|     | B.6                       | TPAU                                                                 | SE                                                                                              | 139 |  |  |  |

|     | B.7                       | Conclu                                                               | nsion                                                                                           | 139 |  |  |  |

| С   | Acro                      | onyms                                                                |                                                                                                 | 141 |  |  |  |

| Lis | t of                      | Figures                                                              |                                                                                                 | 143 |  |  |  |

| Lis | st of                     | Tables                                                               |                                                                                                 | 147 |  |  |  |

|     |                           |                                                                      |                                                                                                 |     |  |  |  |

# CHAPTER 1

# Introduction

For decades, the microprocessor industry has been committed to the continuous improvement of single-core processors by increasing clock frequency and core sophistication to maximize serial performance. Due to the enormous requirements in die area for more and more complex cores and constraints in power consumption, which are limited by the chip's heat density, the industry responded by halting increases in core sophistication and clock rate improvements. Instead, multiple processor cores are integrated into a single chip, producing a multi- or manycore processor to achieve higher overall peak performance without increasing power consumption and complexity of every single core. In this manner, the energy efficiency in form of computation per watt can be improved by scaling the energy consumption linearly with the number of cores instead of exponentially with the frequency and voltage. Thereby, the former trend of integrating a huge amount of simple in-order cores in a manycore processor went to a smaller but increasing number of more complex and powerful out-of-order cores. So, not only do today's large-scale supercomputers and cloud computers already contain tens to hundreds of cores per socket, but also mobile and Internet of Things (IoT) devices accommodate an increasing number of processor cores[54, 107]. However, future processors are expected to contain a much larger number of cores.

In order to take full advantage of the potential of a multi- or manycore processor, applications need to divide their work and employ multiple threads in parallel to process a problem cooperatively. Parallel runtime systems ease the development of parallel applications, because they implement the basic functionality of the parallel execution model, for example, taskification, synchronization, work distribution, and work balancing.

Usually, parallel programs operate in multiple phases with variations in parallel work that can be executed concurrently. So, a single process is usually not able to keep all cores of a manycore processor fully utilized to derive the highest potential benefit from the available hardware. That is why multiple programs have to be executed in parallel. Due to process isolation, the programs are functionally not affecting each other. To overlap input and output latencies and phases with low parallelism, the number of threads of all processes must be greater than the number of processor cores.

The management of the available processor cores as a hardware resource is a typical task of the Operating System (OS). The process scheduler, as a part of the OS, has to decide which process thread to run on which processor core at which time. In order to approach specific optimization goals like throughput, fairness, or response time, the scheduler regularly switches the execution between multiple threads on a core, when the number of threads exceeds the number of cores available. This is called *time sharing*[32].

# 1.1 Problem Statement

The development of multi- and manycore processors were driven by the constantly growing demand for computational power. In addition to acquisition costs, energy consumption is one of the major cost factors in the operation of computing systems. The maximum performance of processors is limited both by the amount of energy available and by the dissipation of power loss in the form of thermal energy. Therefore, users have an interest in obtaining the highest possible ratio of computing work per energy input. Due to the breakdown of *Dennard Scaling*[24], only fractions of the integrated circuits of those processors can be active at the full frequency at any given time without violating Thermal Design Power (TDP) constraints. *Dark Silicon*[33, 100] refers to the amount of circuitry that is powered off in order to meet the given power constraints. The Operating System-directed Configuration and Power Management (OSPM) is responsible for managing processor power consumption and systematically putting unused cores to sleep to save energy and boost active cores. Thereby, choosing the right idle sleep depth means a trade-off between energy savings and wake-up latency when needed again[18, 23].

Parallel applications try to improve their performance by using multiple threads solving problems cooperatively. Unfortunately, creating and starting a new thread is an expensive procedure when using existing OSs. Repeating this process every time a new task is produced results in significant performance degradation, which contradicts the reason for using multiple threads. In order to mitigate this performance loss, common parallel runtime systems try to reduce the number of threads to be created by building and maintaining static thread pools instead of dynamically creating and destroying them. Accordingly, threads are created and kept in the thread pool until they are needed. After finishing a task, they are returned to the thread pool to be used again later[37, 22]. This behavior hides the dynamics in the application parallelism from the OS and, thus, complicates the resource and power management of the OS.

Today's OSs still rely on processes as an abstraction for running programs to simulate exclusive access to all processor resources. The processes abstraction was originally introduced in the single-core era to provide pseudo concurrent execution and overlap latency of input and output operations when there is only one processor available. Hence, each process perceives its own virtual processor that is realized using time-division multiplexing of the processor where it is quickly switching between processes, running each for tens to hundreds of milliseconds[96]. In today's systems, offering real hardware parallelism due to multiple processor cores, processes are still in use although they can now be executed fully concurrently. A process can include multiple software threads that have an individual control flow but share the same address space and might be executed in parallel as well. However, processes on common OSs are still agnostic to the processor utilization and, therefore, tend to create more threads than free cores available. This leads to oversubscription of the processor cores which is still handled using preemptive scheduling that requires regular context switches [115]. Those context switches do not come for free. The direct overhead of a process context switch includes entering the kernel mode, switching the kernel stack, saving the old thread state, loading the new data into the registers, switching the address space, and refreshing the Translation Lookaside Buffer (TLB). Additionally, indirect overhead arises due to missing hotness of the TLB and all levels of caches which slows down the execution of the new process after switching. While the direct overhead takes about tens of processor cycles, the indirect costs can be much higher but are heavily dependent on the hardware platform, application behavior, and data set size [72, 99]. Hence, frequent context switches introduce significant overhead to the actual productive work.

Research OSs with a focus on manycore processors propose to follow the one-thread-per-core execution model[67, 86], where a multi-threaded process can allocate multiple cores, but a core is always allocated exclusively to only a single process. So, frequent context switches, including their overheads, are avoided and scheduling complexity can be reduced which benefits the scalability of the scheduling algorithm. Since the overall number of threads of all processes becomes limited to the number of cores in the system, thread allocation requests might fail, which requires all applications to act resource-aware. However, these research OSs do not focus on energy efficiency and thermal interdependency between all cores of the same processor socket. Furthermore, they lack dark-silicon management and require offline performance analyzes or specialized hardware for application profiling in order to rebalance resource allocation. Preemptive resource revocation is not supported.

When following the one-thread-per-core model, keeping temporally unused threads in pools blocks the associated cores from doing any productive work. Hence, common parallel runtime systems are not suitable for such resource-aware environments, because they do neither dynamically express the applications parallelism profile to OS nor are they able to deal with limited resources or resource revocation.

# 1.2 Main Contributions

This thesis made several research contributions in the field of energy-efficient resource management on multi- and manycore processor systems. It introduces a scalable processing resource management mechanism that improves energy efficiency compared to Linux. Therefore, it follows the one-thread-per-core execution model to avoid the overhead of regular context switches and systematically puts unused cores, considering the actual hardware topology, into a specific sleep state to reduce energy consumption and accelerate active cores. Additionally, the core allocation latency is reduced to motivate the runtime system to pass the application's dynamics in parallelism using dynamic core allocation and deallocated instead of thread pools.

This thesis introduces a resource revocation mechanism allowing asynchronous deprivation of cores that are already allocated to processes but do not meet the global requirements for energy efficiency with their utilization. As a basis for the dynamic resource balancing decisions, an online application profiling mechanism, that uses hardware performance counter and a proof-of-concept balancing strategy are introduced as well.

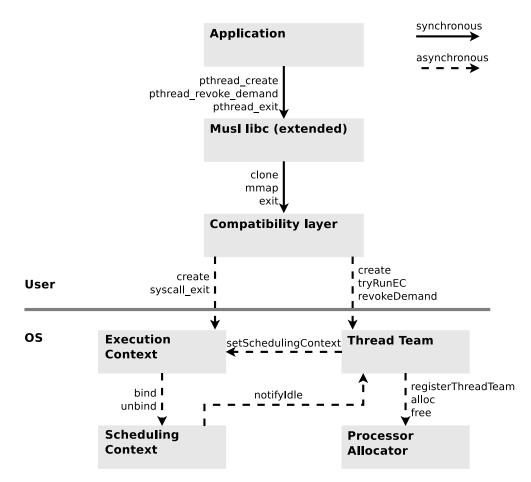

State-of-the-art parallel runtime systems are neither able to handle limited resources nor resource revocation. Hence, a concept for adapting existing parallel runtime systems to behave malleable and handle resource revocation is introduced and exemplarily integrated into Intel Threading Building Blocks (TBB).

# 1.3 Structure of this Thesis

The remainder of this dissertation is outlined as follows. The second chapter presents an overview of the architecture and properties of multi- and manycore processors and how their power consumption can be controlled by the OS. Additionally, the processor resource management of existing OSs and parallel runtime systems are examined. In Chapter 3,

requirements and design aspects for the scalable and energy-efficient organization of processing resources in the OS, mechanisms for core allocation and redistribution based on application profiling, and resource-aware thread management for task-based parallel runtime systems are discussed and concepts derived. Chapter 4 presents the integration of the developed resource management mechanism and application profiling into Many Threads Operating System (MyThOS) as well as the adaptation of a parallel runtime system in order to meet the requirements of malleable applications on the example of TBB. The benefits of resourceaware applications combined with hierarchical processor management are evaluated and the limitations are critically examined in Chapter 5. Chapter 6 summarizes the contributions of this thesis and gives an outlook on future work.

# CHAPTER 2

# Background

The goal of this thesis is to investigate scalable and energy-efficient processor resource management mechanisms for multi- and manycore processor systems. Therefore, this chapter examines the architecture and power management infrastructure of existing multi- and manycore processors. After that, processor resource management mechanisms of state-ofthe-art OSs and approaches for online application profiling are analyzed. Finally, thread management in common parallel runtime systems is presented.

## 2.1 Multi and Manycore Architectures

Due to limits in power density, the microprocessor industry has stopped trying to just steadily increase single-core performance. Instead, multiple processor cores are integrated into a single chip to improve the overall performance without increasing the power consumption. Multi-core processors correspond to this approach but do only contain a few but complex cores. They still provide a high single-core performance so that a good performance can be gained even with moderate parallelism of the application. Manycore processors do not only contain more, but generally simpler cores and aim for power efficiency. The lower single-core performance needs to be compensated with massive parallelism. However, a clear distinction between multi- and manycore is difficult to make for recent processors because they include a high number of complex cores with good single-core performance. Nevertheless, there are multiple properties that allow a further classification of multi- and manycore processors. The following section examines the difference based on the core composition, multithreading support, Tiling, and Network on a Chip (NoC) topology. Multiple processor examples and their classifications are given in table 2.1.

| Name                 | Cores | Composition | Multithreading    | Tiling               | NoC topology        | Release |

|----------------------|-------|-------------|-------------------|----------------------|---------------------|---------|

| AMD EPYC 7003        | 64    | homogeneous | 2 way SMT         | eight cores per tile | $star^1$            | 2021    |

| Intel Xeon Gold 6200 | 28    | homogeneous | 2  way SMT        | one core per tile    | 2D mesh             | 2020    |

| Intel Xeon Phi 7200  | 72    | homogeneous | 4  way SMT        | two cores per tile   | 2D mesh             | 2016    |

| Intel Xeon Phi 7100  | 61    | homogeneous | 4  way SMT        | one core per tile    | bi-directional ring | 2013    |

| Mellanox TILE-Gx72   | 72    | homogeneous | -                 | one core per tile    | 2D mesh             | 2013    |

| UltraSPARC T1        | 8     | homogeneous | 4 way interleaved | one core per tile    | crossbar            | 2005    |

Table 2.1: Examples for multi- and manycore processors [20, 21, 56, 58, 62, 69, 102]

#### 2.1.1 Core Composition

Multi- and manycore processors can be categorized by the composition of processing cores[77]. Homogeneous processors include a collection of identical cores. This simplifies hardware design, verification, and implementation as well as software development. Due to the end of Dennard scaling[24], that stated that the energy consumption per chip area stays constant even if the transistors get smaller and the number of transistors per area increases, the power density became the limiting factor for processor performance. This causes the dark silicon effect[33] so that not all transistors can be used at the same time and some areas of the chip remain dark. To counteract this effect, heterogenous processors integrate a mix of processing cores that differ in the power and performance characteristics or functionality. So, a task can be executed on the most suitable processor core with comparatively high performance and low energy consumption.

### 2.1.2 Multithreading

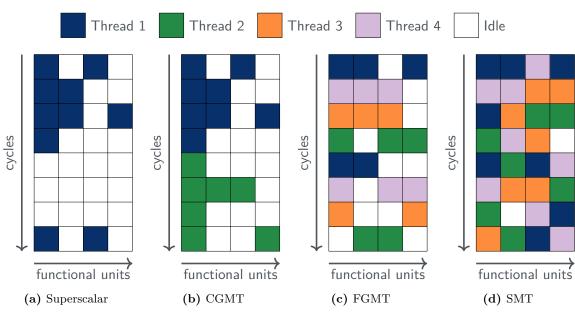

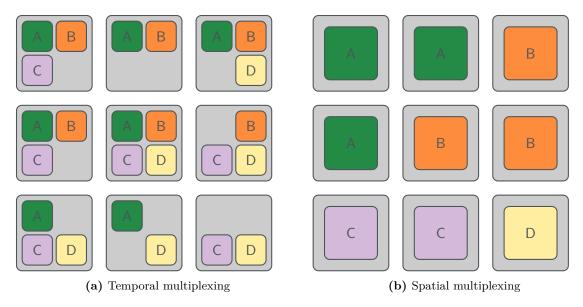

Hardware multithreading is the capability of a compute core to process multiple threads of execution concurrently. There are different types of hardware multithreading: *Temporal multithreading* and *Simultaneous Multithreading (SMT)*[12, 69, 93, 98]. These and their subtypes are explained in the following section and are illustrated in figure 2.1 for comparison.

**Temporal Multithreading** In temporal multithreading only instructions of one thread can be executed at a time and the processor core regularly switches between multiple threads. Hence, it is also called time-sliced or vertical multithreading. It is used to improve throughput

<sup>&</sup>lt;sup>1</sup>Up to eight compute cores form a Core Complex (CCX) and share one last level cache. Each CCX is contained within a single die, called Core Complex Die (CCD). The individual CCDs are directly connected to the central I/O Die (IOD) over Global Memory Interconnect (GMI) and *Infinity Fabric*. The IOD connects all dies and contains the memory controllers as well as other Input and Output (I/O) devices[56, 58].

Figure 2.1: Hardware multithreading types

by hiding memory latency. There are two variations of temporal multithreading. In the case of *Coarse-grain Multithreading (CGMT)*, a thread has full use of the core resources until a long-latency event like a memory stall occurs. In this case, the core switches to another thread in order to bridge the latency. This introduces overhead for the context switch that requires a flush of the instruction pipeline. Therefore, a context switch is only performed when the event is expected to exceed a certain latency. *Fine-grain Multithreading (FGMT)* (also called interleaved multithreading) switches between threads with a more fine granularity which happens typically at an instruction cycle boundary. A selection policy allocates the processor resources to threads that are currently ready and therefore not blocked due to memory stalls. In order to minimize switching costs, processors with fine-grain multithreading include special logic for thread switching.

**Simultaneous Multithreading** SMT schedules instructions from multiple threads on different functional units of a processor at the same cycle and is also called horizontal multithreading. It was introduced to improve the utilization of shared functional units in superscalar processors. However, SMT is also used to hide memory latency and increase throughput as well as energy efficiency. SMT has additional hardware costs compared to interleaved multithreading, because each pipeline stage has to track the corresponding thread identifier. The register set for the architectural state is duplicated for each individual thread, but the duplication of other components is processor-specific. Depending on the processor design and application,

SMT might decrease the performance if shared resources like Floating Point Unit (FPU), TLB, or caches become bottlenecks.

### 2.1.3 Tiling

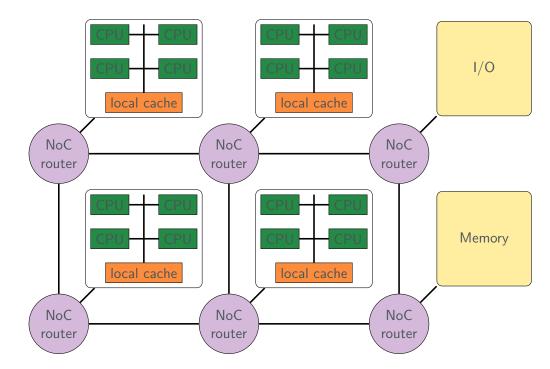

Processors can be clustered into tiles where each tile contains a set of cores, a local cache that is accessed via a shared bus, and one NoC router or switch to communicate with other tiles. An example is given in figure 2.2.

Putting all cores of a multi- or manycore processor into a single tile promises a simple hardware implementation because a NoC is not needed but suffers from limited scalability of the shared memory bus. In contrast, putting each core into an individual tile requires the most additional die area for NoC interconnection but is most flexible and scalable in the number of cores that can be attached by just adding more tiles to the NoC[101, 114].

Figure 2.2: Example of processor tiling architecture with four tiles containing four cores and a local cache each. All tiles, memory, and IO devices are connected via NoC

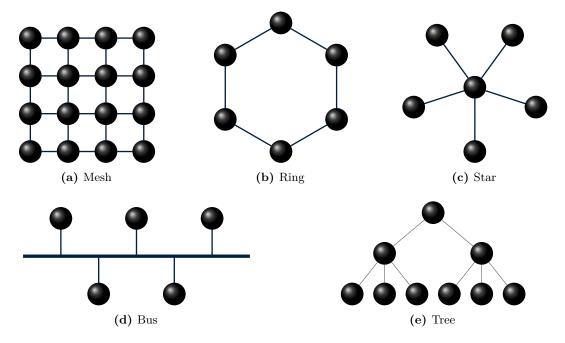

## 2.1.4 NoC Topology

Multi- and manycore processors can also be divided by the underlying Network on a Chip (NoC) topology that connects the tiles, memory, and I/O devices. Thereby, they form the foundation for communication between those individual components while each topology has its own characteristics. Choosing a NoC topology means making a trade-off to meet the chip area, complexity, latency, scalability, and power constraints. As depicted in figure 2.3, common topologies are, for example mesh, ring, star, bus, and tree.

Figure 2.3: Examples of Network on a Chip topologies

# 2.2 Dynamic Power Management in Multi- and Manycore Processors

Multi- and manycore processors increase the overall peak performance and consume less energy than systems in which each processor has its own physical chip. Due to *dark silicon*, not all circuitry of those processors can be permanently active at the full frequency and the performance is therefore tightly coupled to the available energy budget. Hence, this section examines the sources of power dissipation and the capabilities to regulate it during runtime.

#### 2.2.1 Energy Dissipation in CMOS Processors

Energy consumption is a significant criterion when designing integrated circuits. It is limited by the capabilities of the power supply and current requirements as well as the cooling capacity of the heat sink. When examining the energy consumption of processors, one has to think about the energy consumption of integrated circuits using Complementary Metal Oxid Semiconductor (CMOS) technology, because it has been the standard technology for the last five decades[111].

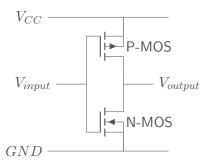

The total power consumption in CMOS technology arises from several sources. Therefore, it can be divided into static and dynamic components[61]. Static power consumption occurs when all inputs of a circuit are held at some constant level and is caused by leakage current due to parasitic diodes in the CMOS circuit. It increases with the supply voltage. Dynamic power consumption only occurs when switching between logical states in the circuit and consists of *transient power consumption* and *capacitive-load power consumption*. It contributes a major portion of the overall power consumption and scales linearly with the switching frequency and the supply voltage squared. Hence, performance improvements by frequency increase, and consequently an increase of the supply voltage as well in order to meet timing requirements, scale sublinearly to the power dissipation. Further explanation can be found in the appendix A.

### 2.2.2 Dynamic Power Consumption Reduction Techniques

In order to understand how the operating system can optimize the processor's energy consumption, this section examines existing mechanisms to dynamically influence the power dissipation during runtime [82].

**Power Gating** The most effective method for reducing power dissipation is to shut down currently unused blocks of the circuit by switching off the power supply. This technique is called *power gating* and prevents not only dynamic but also the static power dissipation, because it inhibits leakage current of unused but powered circuits. Although the benefits of high energy savings are promising, this technique requires additional logic to the circuit for power management and might cause increased time delays for entering and exiting power-saving states.

**Clock Gating** A second power reduction technique is *clock gating*. In contrast to *power gating*, it only avoids dynamic power dissipation by pruning the clock tree which prevents state transition in a specific block of the circuit. The leakage current of static power consumption remains and it requires additional logic for controlling the clock tree in the circuit.

**Dynamic Frequency and Voltage Scaling** The dynamic power consumption of CMOS-based processors increases quadratically with the supply voltage and linearly with the clock frequency. Instead of completely disabling a functional unit in the circuit, the power dissipation can be regulated by dynamically adjusting the clock frequency and supply voltage. Lowering the supply voltage (*undervolting*) promises the greatest energy savings but increases the time required to charge and discharge the capacitances in the circuit leading to slower operations. Therefore, the clock frequency needs to be adjusted to match the supply voltage in order to guarantee timing requirements. Decreasing the clock frequency (underclocking) directly reduces the dynamic power consumption linearly and also enables *undervolting* by being able to tolerate extended operation delays. When the maximum computing power is required, the opposite operation is also possible. Therefore, as long as the energy and cooling budget allow it, the clock frequency (overclocking) and supply voltage (overvolting) can temporarily be increased to boost the execution of the processor. Dynamic voltage and frequency scaling requires sophisticated hardware support which increases a processor's complexity. Additionally, the voltage and clock frequency will only be adjusted with a certain delay to fluctuating performance requirements.

#### 2.2.3 Processor Power Management from the Operating System's Perspective

Today's CMOS-based processors offer mechanisms to adjust the power consumption according to the current performance requirements. However, the processor lacks knowledge about the process schedule and performance, and energy requirements of the user. This knowledge is essential when deciding whether or not to enter a specific power optimization state because state transitions introduce extra delay and consume energy by themselves as well. The operating system is responsible for process scheduling and is therefore aware of the nearfuture processor utilization. In addition, it might include own power management strategies and accept performance hints from the user. For this reason, the power reduction mechanisms of the processor are partly made controllable by software, especially the operating system. Modern processors offer multiple interfaces for operating the power management hardware. This section provides a brief overview of the most common ones. **Performance-States (P-States)** Modern Central Processing Units (CPUs) include mechanisms to monitor thermal conditions and control power consumption. P-states [18, 57, 59] are operational performance states that allow switching between multiple voltage-frequency pairs while the processor is actively executing instructions. They are defined as performance states in the Advanced Configuration and Power Interface (ACPI)[60]. The performance increases with frequency and power consumption which is realized as frequency and voltage scaling in the processor's CMOS circuits.

P-states can be changed in up to 16 P-states from P0 to P15 where P0 is the highest power/performance state which enables the highest possible frequency and each ascending Pstate number represents lower power, lower performance state. The operating system controls P-state per core by accessing specific control, status, and limit registers in order to reduce the peak thermal load and save power. Hardware may limit P-states due to interdependencies between cores that affect the P-state (e.g. thermal constraints). Latest Intel CPUs offer support for *Hardware-Controlled Performance States (HWP)*. This technology is referred to as *Intel Speed Step* or *Intel Speed Shift*[18, 20]. When activated, the operating system is allowed to give hints about performance preferences, but the actual P-state control is performed by the hardware autonomously.

**CPU Idle States (C-States)** C-states [18, 23] are, unlike P-states, idle power-saving states which are used to shut down parts of the processor when unused. They are typically implemented using *clock-gating* and *power-gating* of individual functional units of the processor.

ACPI[60] defines a set of four logical C-states C0 to C3 where a higher number refers to a deeper sleep state with lower power consumption and potentially higher wakeup latency. Those logical sleep states do not necessarily refer to hardware C-states because the mapping is processor-specific. From a hardware perspective, we differentiate two types of C-states: core level *CC-states* and package level *PC-states*. Core level *CC-states* are used to shut down parts of individual cores. Only the CC-states can directly be influenced by the operating system. Entering those idle states can either be done using the ACPI interface or using a set of hardware specific instructions. An overview about CPU instructions for entering idle states is provided in appendix B. Each processor core might contain multiple hardware threads. Therefore, the CC-state of a core equals the lowest (not the deepest) C-state of all threads on this core. The number of available CC-states is hardware specific, but recent Intel processors specify idle states from *CC0* to *CC10* where some include substates[17]: **CC0** is the active state where the core is executing code at normal frequency and thus not an actual idle power-saving state.

CC1/CC1E is the least deep idle state leading to the lowest energy savings and wakeup latency. The core is halted and most clocks are stopped. Substate *CC1E* allows the package to throttle the core's frequency and voltage.

CC2 is only a temporary intermediate state before entering deeper sleep states.

**CC3** flushes the core local first-level data and instruction cache as well as the second-level cache to the shared Last-Level Cache (LLC).

CC4 and CC5 are only temporary intermediate states before entering deeper sleep states. CC6 saves the cores state to a dedicated Static Random-Access Memory (SRAM) and power-gates the core after completion. The core state will be automatically restored when exiting the sleep state.

CC7 - CC10 behave similar to CC6, but allow the package to enter a deeper PC-state

Package level C-states (PC-states) are able to shut down the circuits that support and connect the individual cores. The PC-state is limited to the lowest CC-state among all cores it contains and cannot explicitly be requested by the operating system. In order to enter a PC-state higher than PC0, all hardware threads and cores must be in an idle state. Intel mentions package level sleep states from PC0 to PC10 but not all states are defined:

**PC0** is the active state where at least one core is executing code or did not enter a *CC-state* higher than *CC1*. In addition, the platform configuration might prohibit entering a package level low-power state.

**PC1/PC1E** is the least deep package idle state. In PC1, no additional power reduction actions are initiated. In substate PC1E throttles the cores frequency and voltage to a minimum.

**PC2** is entered if all cores have requested CC3 or deeper idle states, but constraints like a programmed timer in the near future or outstanding memory requests prevent the package from entering a deeper PC-state.

**PC3** might flush and power of the LLC. Most Uncore clocks are stopped and Uncore voltages are reduced.

**PC6** saves the core states before they are shut down and the Phase-Locked Loop (PLL) is turned off.

PC7 behaves similar to PC6 but the LLC might get flushed.

**PC8** equals *CC*7 but the LLC must be flushed and powered off.

**PC9** equals *CC8* but most uncore devices, except input and output devices, are power-gated. **PC10** equals *CC9* but the voltage regulators are in an optimized state (low power mode).

### 2.2.4 Dynamic Performance Boosting

The dynamic usage of performance states and idle states allows to build up headroom in power in the form of saved energy and thermal capacity. The processor monitors its activity and estimates the power consumption. If the power consumption is below the internally defined capacity of the hardware, it can be used to increase the performance in means of voltage and frequency of single cores for short periods of time without exceeding design limits. Examples for this technology are AMD Core Performance Boost[57] and Intel Turbo Boost[18]

# 2.3 Operating System Processor Allocation

The available processors of a computer system must be made accessible for user applications in order to do useful work. This is one type of resource management for which the OS is responsible. Therefore, it needs to fulfill two requirements. At first, it must provide an abstract representation of the actual hardware to increase the programmability and portability of the user application and, secondly, it must control the allocation of system resources to ensure the correct execution of the applications while maximizing the efficiency of the overall system. In order to take advantage of the high peak performance of multiand manycore processors, *multiprogramming* has to be applied, because a single sequential application is not able to utilize numerous cores simultaneously. Multiprogramming can either be realized using *inter-program* parallelism, *intra-program* parallelism, or a combination of both. Inter-program parallelism denotes the parallel execution of multiple sequential applications, whereas intra-program parallelism terms the sequential execution of parallel programs[45]. This work applies a combination of both to meet the increasing number of available cores of future processors. The allocation of processing resources to applications depends on many criteria which are discussed in the following. Afterwards, examples for processing resource management in existing OSs are investigated.

#### 2.3.1 Intra-Program Scalability

Intra-program parallelism as a kind of multiprogramming is one way to utilize the high parallel peak performance of multi- and manycore processors. The number of processing elements in future processors is expected to further increase, but parallel applications are possibly not able to benefit from even more resources[54]. Hence, when assuming an infinite amount of processing resources, what would be the optimal number of processors for an application? This question is investigated in the following.

**Amdahl's Law** In 1967, Gene Amdahl[3] emphasized that single computer systems reached their limits in computational power and that, in order to significantly accelerate the execution of applications to real problems, multiple computers need to be connected to permit a cooperative solution. He also noted that the speedup in the runtime of these applications does not scale linearly with the number of compute nodes used and concluded that the speedup is limited by the sequential part of an application.

According to Amdahl, an application with a fixed problem size can always be divided into a parallel part ( $P_{parallel}$ ) and a sequential part ( $P_{sequential}$ ), so that applies  $P_{parallel} + P_{sequential} = 1$ . Therefore, the total runtime T equals the sum of the runtime of the sequential part  $T_{sequential}$  and the runtime of the parallel part  $T_{parallel}$ . The speedup of the parallel part ( $P_{parallel}$ ) is assumed to scale linearly with a number of processing units (n) applied to it while the time required to execute the sequential part ( $P_{sequential}$ ) remains constant. Based on this assumption, a model for the expected application speedup depending on the parallel portion and the number of applied processing units is made:

$$T = T_{sequential} + T_{parallel} \tag{2.1}$$

$$Speedup = \frac{T(1)}{T(n)} = \frac{T(1)}{T_{sequential} + \frac{T_{parallel}}{n}} = \frac{1}{P_{sequential} + \frac{P_{parallel}}{n}}$$

(2.2)

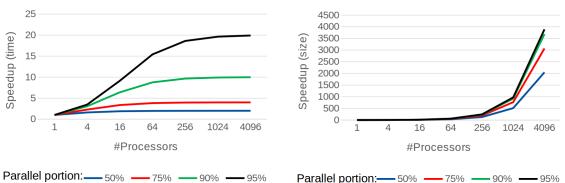

Therefore, he concludes that the portion of sequential work limits the performance of highly parallel processing. Figure 2.4a shows the expected speedup in runtime for an application with a parallel portion of 50%, 75%, 90%, and 95% that is executed on up to 4096 processing units.

**Gustafson's Law** In 1988, John Gustafson[46] expressed skepticism about Amdahl's Law and that the maximum speedup of an application is only  $\frac{1}{P_{sequential}}$ , even for an unlimited

(a) Scalability in runtime with fixed problem size depending on the portion of parallel work according to Amdahl's Law[3]

(b) Scalability in problem size with fixed runtime

depending on the portion of parallel work according to Gustafson's Law[46]

Figure 2.4: Application speedup models

number of processing units. He also mentioned that in practice, one would not run a fixed-size problem on machines with a various number of processing units. Instead, the problem size generally expands in order to make use of the additional resources, which increases the parallel portion, because sequential work like initialization is only done once. Therefore, not the problem size, but the runtime is assumed to be constant when estimating the speedup. Figure 2.4b shows the scaled speedup in the problem size for a fixed runtime depending on the parallel portion of an application. The scaled speedup calculates as follows:

$$Speedup_{scaled} = \frac{P_{sequential} + P_{parallel} * n}{P_{sequential} + P_{parallel}} = n + (1 - n) * P_{sequential}$$

(2.3)

Amdahl's Law and Gustafson's Law in the Multi- and Manycore Era Amdahl proposed to connect multiple single-processor systems to a distributed machine in order to cooperatively solve problems. Today, High Performance Computing (HPC) cluster machines are state of the art and even individual nodes contain numerous multi- or Manycore processors, making them a distributed system themselves. So, the scalability models can be applied on inter-node, intra-node, and on-chip levels. However, Amdahl and Gustafson did not take the overhead for, among other things, communication and resource management into account which also limits speedup[50]. Additionally, the software is not just infinitely parallel and sequential, but more complex in its structure. Superlinear speedup due to increased cache and main memory size when using more processing units is not considered as well. Other, more complex scalability models extend Amdahl's Law and Gustafson's Law by considering communication costs and available chip area as a limiting factor in multi-core systems[52]. Nonetheless, those models

only serve as a coarse approximation or an upper bound for the expected speedup, because this highly depends on the individual application and hardware. Often, parallel applications experience a sweet spot at a certain number of processing units and suffer from performance penalties when using more.

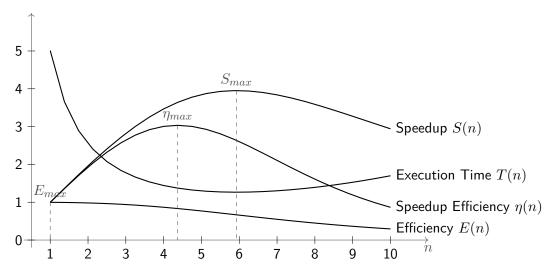

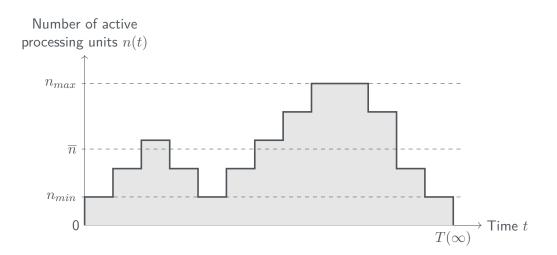

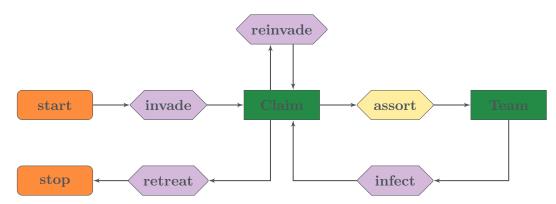

**Speedup Efficiency** Optimizing the number of allocated processing cores of a sub-linearly scaling application according to the shortest execution time maximizes the speedup, but reduces the overall efficiency of the system. The *efficiency*  $E(n) = \frac{S(n)}{n}$  is defined as the normalized speedup divided by number of processors. Maximizing the efficiency and minimizing the execution time results in a conflict of opposing goals. The *speedup efficiency*  $\eta(n) = E(n) * \frac{T(1)}{T(n)} = E(n) * S(n) = \frac{S(n)^2}{n}$  is a compromise for this conflict and describes the ratio of costs  $C(n) = n * \frac{T(n)}{T(1)} = \frac{n}{S(n)}$  and benefits E(n). The maximum speedup efficiency minimizes the cost-benefit ratio and is denoted as *processor working set*[40, 45]. Figure 2.5 illustrates the relationship between execution time, speedup, efficiency, and speedup efficiency.

Figure 2.5: Relationship between execution time, speedup, efficiency, and speedup efficiency

### 2.3.2 Optimization Criteria

As already indicated, pure intra-process parallelism might not be sufficient to efficiently utilize the performance capabilities of future parallel processors. Hence, multiple processes can be executed simultaneously, sharing the same manycore processor. This requires suitable processor allocation management. Thereby, the primary goal of the processor allocation is to ensure the successful execution of all applications, but there are further optimization goals. It is necessary to be specific about the goal in order to make appropriate allocation decisions[36].

**Utilization** The utilization is denoted as the percentage of processor cycles spent for productive computation or rather allocated to user programs. Optimizing only for utilization might lead to a long response time or even to starvation of small jobs, whereas massively parallel and long-running jobs will be preferred because they require a smaller timeshare for administrative overhead. This possibly harms the primary goal and is also limited to the current system load if below a certain saturation point. Additionally, utilization does not consider the efficiency of executing user code that might be able to occupy many resources but spends most processing time for management overhead.

**Throughput** The number of completed jobs per time unit is termed throughput. With an increasing number of jobs completed, more user applications become satisfied. Similarly to utilization, it is limited to the current system load. When saturated, a strictly throughput optimized system prefers short over long-running jobs which harms fairness and might cause starvation as well. Furthermore, the throughput heavily depends on the average size of the available jobs.

**Response Time** For interactive applications, fast feedback to the user is essential. Hence, two measures are relevant and thus serve as the basis for optimization. The *response time* denotes the latency from job submittal until first response to the user whereas the *turnaround time* is defined as the latency to completion. Analogically to throughput, the response time heavily depends on the job size. In addition, not all applications have time requirements and there are thresholds below which the user can no longer detect any improvement.

**Fairness** Resources are allocated fairly to all processes so that no process is permanently neglected. This reduces the average response time and avoids starvation. Fairness can be achieved on the user, process, or thread level.

**Transparency** Multiuser systems or systems on which the number of simultaneously running processes exceeds the hardware parallelism strive to create the illusion of a dedicated machine for each individual process. Being agnostic of other processes eases the software development and is usually achieved using temporal processor multiplexing which is examined in the following.

### 2.3.3 Processor Multiplexing

Modern parallel computer systems usually run multiple applications simultaneously to increase utilization. In order to enable this kind of resource sharing, mechanisms for partitioning the processing hardware are required. Thereby, a distinction between *temporal* and *spatial* processor multiplexing is made. The concepts of both types are depicted in figure 2.6.

Figure 2.6: Types of processor multiplexing

**Temporal Multiplexing** Temporal multiplexing[32], which is also known as *time sharing*, denotes a processor sharing mechanism where multiple applications are allocated to a single processing element. Each application runs for some quantum of time before being preempted in order to allow the next application to run. This mechanism is required in multitasking OSs if the number of concurrently running applications exceeds the amount of available processing elements. Thus, a pseudo-concurrent execution can be achieved and the average response time can be minimized.

The procedure of changing the execution from one application to another is called *context switch* and needs to be performed after each quantum. The size of the quantum depends on the particular scheduling algorithm and the number of threads. Thereby, a too-large quantum time increases the response time which might not be tolerated in interactive environments, but a too small quantum size leads to unnecessarily frequent context switches, that introduce a certain overhead and thus reduce throughput [2].

**Context Switch Overhead** As mentioned before, context switches introduce overhead that reduces the proportion of processing time actually used for productive computation. This overhead arises from multiple sources. The direct overhead of a process context switch includes entering the kernel mode, switching the kernel stack, saving the old thread state, loading the new data into the registers, switching the address space, and refreshing the TLB. Additionally, indirect overhead arises due to missing hotness of the TLB and all levels of caches which slows down the execution of the new process after switching. While the direct overhead takes about tens of processor cycles, the indirect costs can be much higher but are heavily dependent on the hardware platform, application behavior, and data set size[72, 99]. Hence, frequent context switches introduce significant overhead to the actual productive work.

Modern processors contain Process-Context Identifiers (PCIDs) which are used to distinguish information about address translation cached for different address spaces. Thus, when creating entries in the TLB, it associates new entries with the current PCID and only uses matching entries for address translation. So, when switching contexts, the TLB does not have to be flushed and entries of processes might still be present from the previous execution[18]. However, the TLB owns a limited number of entries which are, if using temporal multiplexing, shared between all processes running on this processor and thus displace each other, reducing the hotness of the TLB.

**Spatial Multiplexing** Spatial multiplexing[32, 113], also called *space sharing*, refers to a processor sharing mechanism where the system is partitioned into clusters of processing elements, and each cluster is exclusively allocated to a single application that is allowed to run to completion without being preempted in favor of another application. Compared to temporal multiplexing, this reduces the overhead for context switching and eliminates side-channel effects caused by processor state sharing and thus increases the throughput and predictability of applications. Spatial multiplexing limits the number of simultaneously

running applications to the number of processing elements in the system, but future systems are expected to contain so many processing elements that they will exceed the average number of applications that a user wishes to run simultaneously[94]. Nevertheless, depending on the actual system load, parallel applications may get assigned fewer processing resources than requested. In order to avoid delays in execution, those applications must be able to dynamically adapt to the actual available resources. This property is also referred to as *resource-awareness* and requires applications to be *malleable* which is discussed in the following.

#### 2.3.4 Spatial Processor Partitioning

As examined in section 2.3.1, the intra-program scalability is usually limited by multiple factors so that the speedup increases only sub-linearly with the number of processing elements which decreases the efficiency. So, in order to increase the system efficiency, inter-program scalability can be applied where the available processing resources need to be shared among multiple programs that are executed simultaneously. Spatial partitioning is a processor sharing mechanism where the available processing units are split into contiguous disjoint territories. Thereby, it focuses on the quantitative and qualitative allocation of processing resources to individual applications which are examined in the following[89].

#### **Quantitative Partitioning**

When partitioning a multi- or manycore system, one has to decide, which program obtains how many processors. The number of resources per application is determined by specific allocation strategies that strive to reach the optimization goal. The allocation decision can be made at different points in time.

**Static Partitioning** Using static partitioning, the number of processing units allocated to an application happens before the actual execution and stays constant over the entire runtime. The allocation can either be determined offline by solving user-defined constraints and compiler-generated information about the program structure and data dependencies or at the starting time of the application at which the current system load can be taken into account for decision making. Static partitioning has the advantage that applications can rely on the number of processor cores allocated to them during their entire runtime. Hence,

applications do not have to be able to release or accept additional cores at runtime. However, there are also disadvantages associated with static partitioning. If too many processor cores are currently occupied, additional applications can only be started after the execution of a running application has been completed and its cores become available again. Furthermore, running applications can not take benefit from the allocation of additional, otherwise unused cores. The resource allocation of running applications cannot be redistributed in order to optimize utilization or efficiency.

**Dynamic Partitioning** While in the case of static partitioning the programs were given a fixed number of processor cores over the whole runtime, dynamic partitioning is more flexible and allows additional cores to be allocated to and withdrawn from an application dynamically. So, the resource allocation can be optimized using resource redistribution in order to for instance, archive the highest speedup of individual applications or maximize global efficiency. Thereby, the overhead for profiling, reallocation, and adaption of the application needs to be lower than the expected performance gain. Dynamic partitioning requires co-design of the OS, the runtime system, and the application model. This is examined in the following section.

#### Parallel Application Types

Depending on the programming model, applications are expected to fulfill a resource handling model that meets the convention of the OS. Therefore, applications can be categorized into multiple job types [36] as shown in table 2.2.

**Rigid Jobs** Rigid jobs require a user-defined fixed number of logical processors that are statically requested at the creation time. The job is not able to run with less and cannot make use of additional processors, but it does not need to provide further information to the scheduler for decision making. Rigid jobs are typically applied for applications that are

| Who decides | When is it decided |                  |  |  |

|-------------|--------------------|------------------|--|--|

| who decides | at submittal       | during execution |  |  |

| User        | Rigid              | Evolving         |  |  |

| System      | Moldable           | Malleable        |  |  |

Table 2.2: Parallel job types in terms of processor allocation[36]

written to be compatible with such simple system interfaces or are highly optimized for a fixed number of processors.

**Moldable Jobs** In contrast to rigid jobs, moldable jobs are flexible in the number of processors they require. They allow the scheduler to dictate the number of processors at the beginning of execution under the assumption that additional resources will improve the job's performance. The application automatically configures to the given number of processors and does not allow any reconfiguration of this number during execution. Hence, the scheduler is, based on the current system status, able to set the number of processors which is referred to as *adaptive partitioning*. This allows the system to globally maximize the overall system performance, while rigid jobs would only optimize to run at the sweet spot of their local speedup curve. Moldable jobs might specify individual constraints like a minimum and a maximum number of processors, memory, and response time requirements. A typical use case for moldable jobs is, for example Single Program Multiple Data (SPMD) style applications that can be executed over a wide range of processors.

**Evolving Jobs** Evolving jobs are similar to rigid jobs but may change their resource requirements during execution. Those are usually jobs that are composed of multiple phases with different parallelism properties. For each phase, evolving jobs can only continue execution when the current resource requirements are fulfilled and are not able to take benefit from additional resources.

**Malleable Jobs** Malleable jobs are the most flexible job type because they can adapt to changes in the number of processors during execution. This allows the scheduler to dynamically adjust the processor allocation when system load changes and is called *dynamic partitioning*. A varying number of assigned processor units can also be used to collect scalability information about the job during execution. Malleable jobs are currently only available in some scientific projects[68] but not supported on commercial machines because they require complex interactions between the OS and the runtime system. Most applications and OSs are neither able to express or handle dynamic resource limitations nor resource revocation.

#### **Qualitative Partitioning**

Besides the pure number of processing cores, the actual position in the network and other specific properties of the individual cores matter when allocating them to applications. Hence, qualitative partitioning concerns the question of which program obtains which processors[49].

**Communication Distance** In order to solve computational problems cooperatively, communication between processing units allocated to an application is required. Thereby, the performance depends on the communication delay, which increases with the physical distance and the number of routers that need to forward a message along the shortest path between the interacting processing units. Hence, communicating threads should be placed close together to keep communication delays low.