# Automatisierter Entwurf anwendungsspezifischer VLIW-Prozessoren

Von der Fakultät für Mathematik, Naturwissenschaften und Informatik der Brandenburgischen Technischen Universität Cottbus

zur Erlangung des akademischen Grades

Doktor der Naturwissenschaften (Dr. rer. nat.)

genehmigte Dissertation vorgelegt von

Diplom-Informatiker Mario Schölzel

geboren am 17. November 1975 in Lübben.

Gutachter: Prof. Dr. rer. nat. habil. Peter Bachmann

Gutachter: Prof. Dr. Rolf Drechsler

Gutachter: Prof. Dr.-Ing. Sorin A. Huss

Tag der mündlichen Prüfung: 09.10.2006

#### **Danksagung**

Diese Arbeit ist während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Lehrstuhl von Professor Peter Bachmann entstanden. Bei ihm möchte ich mich für die fachliche Betreuung der Arbeit, seine konstruktive Kritik, die eingeräumten Freiräume und seine entgegengebrachte Geduld insbesondere gegen Ende der Arbeit bedanken. Allen meinen Kolleginnen und Kollegen am Lehrstuhl möchte ich für die angenehme Arbeitsatmosphäre danken.

Professor Vierhaus hat mich durch fachliche Hinweise und durch Diskussionen im Rahmen des gemeinsam durchgeführten Lehrstuhlseminars unterstützt. Dafür danke ich ihm sehr.

Ohne Thomas König und Felix Krüger, die beide den größten Teil der prototypischen Implementierung von DESCOMP durchgeführt haben, hätte die Arbeit nicht gelingen können. Ihnen gilt deshalb mein besonderer Dank. Ebenso Andy Heinig, Sebastian Scholz, Katja Winder, Christian Köhler und Michael Vogel, die durch ihre Studienarbeiten, Diplomarbeiten und ihre Tätigkeit als studentische Hilfskraft Beiträge und Anregungen zu dieser Arbeit geliefert haben.

Besonderer Dank gebührt Susann, die mich in den letzten Monaten so großartig unterstützt hat und mit unendlicher Geduld viele Rechtschreibfehler gefunden hat, die ich zuvor mit großer Sorgfalt eingearbeitet habe.

## Inhaltsverzeichnis

| 1 | Einle | eitung                                          | 1  |

|---|-------|-------------------------------------------------|----|

|   | 1.1   | Einsatzbereiche                                 | 2  |

|   | 1.2   | Motivation                                      | 3  |

|   | 1.3   | Zielstellung                                    | 4  |

| 2 | Mod   | lellbildung                                     | 5  |

|   | 2.1   | Prozessormodell                                 | 5  |

|   | 2.1.1 | Datenpfadmodell                                 | 7  |

|   | 2.1.2 | Pipelinemodell und Bypass                       | 12 |

|   | 2.1.3 | Modell für den Strom- und Platzverbrauch        | 15 |

|   | 2.1.4 | Formales Prozessormodell                        | 18 |

|   | 2.2   | Programmmodell                                  | 20 |

|   | 2.3   | Prinzip der DSE mit DESCOMP                     | 30 |

| 3 | Verv  | wandte Arbeiten                                 | 35 |

|   | 3.1   | High-Level-Synthese                             | 35 |

|   | 3.1.1 | Allgemeines Vorgehen in der High-Level-Synthese | 36 |

|   | 3.1.2 | P. High-Level-Synthesesyteme                    | 39 |

|   | 3.2   | Design-Space-Exploration für VLIWs              | 41 |

|   | 3.2.1 | Manuelle Design-Space-Exploration               | 42 |

|   | 3.2.2 | P CASTLE                                        | 42 |

|   | 3.2.3 | B DSE für den TriMedia64 Prozessor              | 43 |

|   | 3.2.4 | PICO                                            | 45 |

|   | 3.2.5 | 5 DSE nach Lapinskii                            | 46 |

|   | 3.2.6 | 6 MOVE                                          | 47 |

|   | 3.2.7 | Die Lx-Plattform                                | 48 |

|   | 3.2.8 | 3 AutoTIE                                       | 49 |

|   | 3.2.9 | DSE für geclusterte Architekturen               | 49 |

|   | 3.3   | Zusammenfassung                                 | 50 |

| 4 | Loka  | le Optimierung mit DESCOMP                      | <b>53</b> |

|---|-------|-------------------------------------------------|-----------|

|   | 4.1   | Planungsalgorithmus                             | 54        |

|   | 4.1.1 | Prioritätsfunktion                              | 59        |

|   | 4.1.2 | Test auf Zulässigkeit                           | 60        |

|   | 4.1.3 | Zielfunktion                                    | 64        |

|   | 4.1.4 | Minimierung der Ports                           | 65        |

|   | 4.1.5 | Minimierung der Operationstypen                 | 68        |

|   | 4.1.6 | Minimierung von Operatorkonflikten              | 71        |

|   | 4.2   | Ressourcenallokation                            | 80        |

|   | 4.2.1 | Konstruktion des entfalteten Interferenzgraphen | 82        |

|   | 4.2.2 | Färben des entfalteten Interferenzgraphen       | 85        |

|   | 4.2.3 | Knotenauswahl in der Reduktionsphase            | 90        |

|   | 4.2.4 | Behandlung der Knoten in der Färbungsphase      | 90        |

|   | 4.3   | Clusterung                                      | 94        |

|   | 4.3.1 | Clusterung nach der Ablaufplanung               | 95        |

|   | 4.3.2 | Clusterung vor der Ablaufplanung                | 95        |

|   | 4.3.3 | Gekoppelte Clusterung und Ablaufplanung         | 96        |

| 5 | Glob  | ale Optimierung mit DESCOMP1                    | 11        |

|   | 5.1   | Zielprogramme erzeugen                          | .12       |

|   | 5.2   | Optimierung der Portkonfiguration1              | 13        |

|   | 5.2.1 | Optimierung der Registerbankkosten1             | 14        |

|   | 5.2.2 | Optimierung des Stromverbrauchs1                | .20       |

|   | 5.3   | Optimierung der Typkonfiguration1               | .23       |

|   | 5.4   | Abschließende Ressourcenallokation1             | 29        |

| 6 | Erge  | bnisse1                                         | <b>31</b> |

|   | 6.1   | Implementierung und Konfiguration               | .32       |

|   | 6.2   | Benchmarkprogramme und Vergleichbarkeit1        | .34       |

|   | 6.3   | Qualität der lokalen Optimierung1               | 36        |

|   | 6.3.1 | Registerbankkosten ungeclusterter Architektur1  | 36        |

|                        | 6.3.2    | Registerbankkosten geclusterter Architektur | 139 |

|------------------------|----------|---------------------------------------------|-----|

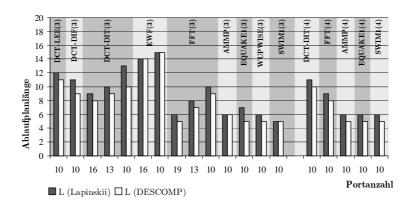

|                        | 6.3.3    | Vergleich der Ablaufplanlängen              | 142 |

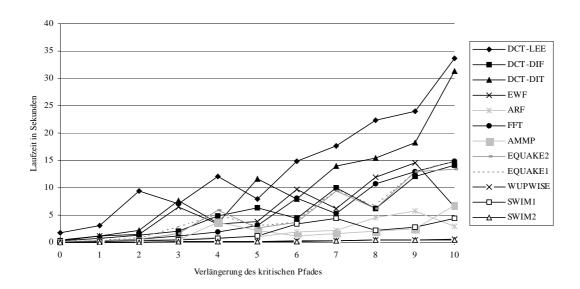

|                        | 6.3.4    | Laufzeit des Planungsalgorithmus            | 144 |

|                        | 6.3.5    | Zusammenfassung                             | 145 |

| 6                      | 6.4 C    | Qualität der globalen Optimierung           | 148 |

|                        | 6.4.1    | Aussagen zur Qualität                       | 148 |

|                        | 6.4.2    | Beispielhafte Design-Space-Exploration      | 152 |

|                        | 6.4.3    | Erweiterungsmöglichkeiten                   | 155 |

| 7                      | Zusam    | menfassung und Ausblick                     | 157 |

| An                     | hang A   |                                             | 161 |

| An                     | hang B   |                                             | 167 |

| An                     | hang C   |                                             | 183 |

| Ab                     | bildung  | sverzeichnis                                | 185 |

| Ta                     | bellenve | erzeichnis                                  | 189 |

| Ab                     | kürzun   | gsverzeichnis                               | 191 |

| $\mathbf{S}\mathbf{y}$ | mbolver  | rzeichnis                                   | 193 |

| Lit                    | eraturv  | erzeichnis                                  | 197 |

## 1 Einleitung

In einigen Einsatzbereichen digitaler Systeme sind die Anforderungen an die Verarbeitungsgeschwindigkeit bei gleichzeitig niedrigem Platz-Stromverbrauch so hoch, dass diese Anforderungen nur durch die Verwendung spezialisierter Hardware erfüllt werden können. Zugleich sind die besonders effizient abzuarbeitenden zeitkritischen Algorithmen in solchen Systemen oft fixiert [39]. Eine spezielle Hardwarelösung für jeden Algorithmus bietet im Allgemeinen die höchste Ausführungsgeschwindigkeit, ist aber unflexibel und sehr zeitintensiv in der Realisierung, was im Widerspruch zu den geforderten kurzen Entwicklungszeiten vieler digitaler Systeme steht. Kleinere Modifikationen an den Algorithmen sind bei einer Hardwarelösung in einer späteren Entwurfsphase des Systems ebenfalls kaum noch möglich. Anwendungsspezifische Prozessoren bieten in dieser Hinsicht einen guten Kompromiss zwischen Flexibilität und Ausführungsgeschwindigkeit [73], da sie in der Lage sind, leicht modifizierte Varianten der zeitkritischen Algorithmen und andere zeitunkritische Teile der Anwendung abzuarbeiten. Die zeitkritischen Algorithmen müssen dabei nicht immer so schnell wie möglich, sondern nur innerhalb gegebener Zeitschranken ausgeführt werden, so dass auch ein Kompromiss zwischen Ausführungsgeschwindigkeit sowie Hardwarekosten und Stromverbrauch des anwendungsspezifischen Prozessors zu finden ist. Die unter diesen Optimierungszielen durchgeführte Bestimmung der Parameter eines Prozessors wird als Design-Space-Exploration (DSE) bezeichnet. Bekannte Verfahren zur DSE weisen eine hohe Komplexität auf, die dadurch entsteht, dass die gegebene Anwendung mit einem Compiler für eine Architektur mit festen Parametern übersetzt wird. Die Parameter der Architektur sowie der Compiler werden bei diesen Ansätzen in einem iterativen Prozess immer wieder modifiziert, um eine geeignete Parameterkonfiguration zu finden. Die so zu untersuchende Menge von Parameterkonfigurationen eines Prozessors ist extrem groß. Der im Rahmen dieser Dissertation entwickelte DESCOMP<sup>1</sup>-Ansatz vermeidet die hohe Komplexität bekannter DSE-Verfahren, indem er die gegebenen Algorithmen wie ein Compiler übersetzt, aber ohne dass die genauen Parameter der Zielarchitektur bekannt sind. Aus dem Zielcode der so übersetzten Algorithmen werden dann die Parameter des anwendungsspezifischen Prozessors, wie beispielsweise die Anzahl der Registerbänke und die Anzahl und Art parallel ausführbarer Operationen, abgeleitet.

<sup>&</sup>lt;sup>1</sup> DESign by COMPilation

## 1.1 Einsatzbereiche

Die Bereiche, in denen anwendungsspezifische Prozessoren eingesetzt werden, sind eingebettete Systeme und SoCs (System on Chip), wie sie beispielsweise in Fahrzeugen, Mobiltelefonen, Geräten für das digitale Fernsehen und der Datenübertragung vorkommen [85] und in denen große Datenmengen zu verarbeiten sind. Diese Systeme werden immer komplexer, da immer höhere Anforderungen an sie gestellt werden [56]. Oft bestehen sie aus mehreren Prozessorkernen mit lokalen und globalen Speichern, die durch Busse verbunden sind. Anwendungsspezifische Prozessoren sind oft nur eine Komponente darin [60, 85]. Vor dem Entwurf solcher Systeme ist das auszuführende Anwendungsspektrum fixiert, so dass der Entwurf unter anderem die Zerlegung der Anwendung in Teile, die durch Hardware bzw. Software zu realisieren sind, umfasst [39]. Weiterhin ist die Auswahl der genutzten Hardwarekomponenten und die Zuordnung der in Software zu realisierenden Teile zu den Prozessorkernen im System zu treffen. Werkzeuge, die den Entwickler bei dieser Arbeit unterstützen sind z. B. in [11, 62, 82] zu finden. Sowohl in eingebetteten Systemen als auch in SoCs werden häufig seriengefertigte Prozessoren verwendet, da diese unmittelbar verfügbar und kostengünstig sind [60, 63, 85]. Entsprechende Prozessoren sind beispielsweise der TMS320C6x, ADSP2106x-SHARC oder TriMedia [1, 3, 31]. Allerdings sind diese Prozessoren in einem großen Anwendungsspektrum einsetzbar, weshalb sie einen relativ großen Funktionsumfang bieten. Da SoCs und eingebettete Systeme sehr häufig in großer Stückzahl gefertigt werden und/oder in mobilen Systemen zum Einsatz kommen, muss beim Entwurf besonders auf einen geringen Platz- und Stromverbrauch geachtet werden. Seriengefertigte Prozessorkerne führen deshalb oft zu einem höheren Platzund Stromverbrauch als erforderlich, da sie nicht optimal Anforderungen der auszuführenden Software angepasst sind.

Der Einsatz von Prozessoren, die sich an die Anforderung der Anwendung anpassen lassen, erlaubt eine hohe Ausführungsgeschwindigkeit und das Einsparen von Platz und Strom. Unter anderem auch deshalb, weil verschiedene Algorithmen, die sonst durch unterschiedliche Komponenten im System abgearbeitet werden, dann auf einem Prozessor ausgeführt werden können, der an die Anforderungen dieser Algorithmen angepasst ist. Somit kann durch Synergieeffekte nicht nur Hardware sondern auch ein Teil des Verbindungsnetzwerkes im SoC eingespart werden. Neben den oben bereits genannten Prozessoren werden von der Industrie auch Prozessorkerne angeboten, deren Busbreite und Registeranzahl angepasst werden kann [27] oder die auch umfangreichere Anpassungen der Architektur zulassen, wie beispielsweise der Tensilica Xtensa LX Prozessorkerne [84] und die Lx-Architektur von Hewlett-Packard und STMicroelectronics [73].

### 1.2 Motivation

Anhand des TriMedia32 Prozessors [2] wird eine Motivation für die Zielstellung dieser Dissertation geliefert. Der Prozessor wurde speziell für Multimediaanwendungen entworfen. Er verfügt insgesamt über 23 Operatoren zum Ausführen von elf verschiedenen Operationstypen. Abhängig vom Typ einer Operationen können bis zu fünf Operationen gleichzeitig ausgeführt werden, jede davon in einer funktionalen Einheit. Die aus [48] entnommene Tabelle 1.1 gibt einen Überblick über die mögliche Anordnung der Operationen in den funktionalen Einheiten.

| Operator-<br>typ | funktionale<br>Einheiten |   | Latenz | Beschreibung |   |    |                                |

|------------------|--------------------------|---|--------|--------------|---|----|--------------------------------|

|                  | 1                        | 2 | 3      | 4            | 5 |    |                                |

| ALU              | X                        | X | X      | X            | X | 1  | Integer- und Bitoperationen    |

| DMem             |                          |   |        | X            | Х | 3  | Lade- und Speicheroperationen  |

| DMemSpec         |                          |   |        |              | Х | 3  | Speicher- und Cache-Management |

| Shifter          | X                        | X |        |              |   | 1  | Schiebe- und Rotieroperationen |

| DSPALU           | X                        |   | X      |              |   | 2  | DSP-Operationen                |

| DSPMul           |                          | X | X      |              |   | 3  | Multiplikation und Addition    |

| Branch           |                          | X | X      | X            |   | 4  | Sprünge                        |

| FALU             | X                        |   |        | X            |   | 3  | Gleitkommaarithmetik           |

| IFMul            |                          | X | X      |              |   | 3  | Gleitkommamultiplikation       |

| FComp            |                          |   | X      |              |   | 1  | Gleitkommavergleiche           |

| FTough           |                          | X |        |              |   | 17 | Division und Wurzelberechnung  |

Tabelle 1.1: Übersicht über die 11 verschiedenen Operatortypen des TriMedia32 Prozessors.

Jede Operation muss von einer funktionalen Einheit ausgeführt werden, in der ein Operator existiert, der die entsprechende Operation ausführen kann, verdeutlicht durch ein Kreuz in der entsprechenden Spalte in Tabelle 1.1. Alle Operatoren in einer funktionalen Einheit verwenden dieselben Lese- und Schreibports der Registerbank. Deshalb kann in jeder funktionalen Einheit nur eine Operation gleichzeitig ausgeführt werden. Einige Kombinationen von Operationen können somit nicht parallel verarbeitet werden, wie beispielsweise zwei Shift- und zwei DSPALU-Operationen. In diesem Fall müsste die funktionale Einheit 1 zwei Operationen gleichzeitig abarbeiten. Der Grund für die in Tabelle 1.1 angegebene Auswahl und Zuordnung von Operatoren zu funktionalen Einheiten ist unter anderem das Anwendungsspektrum, das typischerweise vom TriMedia32 Prozessor ausgeführt wird und für das sich

diese Zuordnung als vorteilhaft erwiesen hat. Es existieren bis zu 216.000 Möglichkeiten, die in Tabelle 1.1 angegebenen Operatoren den fünf funktionalen Einheiten zuzuordnen. Wird nicht festgelegt, in wie vielen funktionalen Einheiten ein Operatortyp vorhanden sein muss, so gibt es sogar bis zu 2<sup>55</sup> Möglichkeiten. Noch mehr Möglichkeiten gibt es, wenn auch die Anzahl der funktionalen Einheiten nicht festgelegt ist. Für den TriMedia64 Prozessor [45] wurde eine Design-Space-Exploration durchgeführt, durch die eine geeignete Zuordnung von Operatoren zu funktionalen Einheiten für ein gegebenes Anwendungsspektrum gefunden werden sollte [30]. Auf den entsprechenden Ansatz für diese sehr komplexe Aufgabe wird im Abschnitt 3.2.3 detaillierter eingegangen.

## 1.3 Zielstellung

In dem vorangegangenen Beispiel wurde angedeutet, wie groß der Suchraum für die DSE eines anwendungsspezifischen Prozessors werden kann. Bekannte DSE-Ansätze nutzen das in der Einleitung beschriebene iterative Vorgehen zur Bestimmung der Prozessorparameter, was neben einem hohen zeitlichen Aufwand oft auch eine Interaktion mit dem Entwickler bedingt, um beispielsweise Bereiche des Suchraums während der DSE auszuschließen. Das Ziel dieser Arbeit ist es, ein methodisches Vorgehen und die dafür benötigten Techniken zu entwickeln, so dass für ein fest vorgegebenes Spektrum von Algorithmen und zugehörigen Zeitschranken die DSE für Prozessoren von datenflussdominierten Anwendungen vollständig automatisiert und ohne mehrfaches Übersetzen der Anwendung durchgeführt werden kann. Der erzeugte Prozessor muss dabei noch flexibel genug sein, um auch andere Algorithmen, für die er nicht optimiert wurde, abzuarbeiten. In Abschnitt 2 werden die genutzten Modelle spezifiziert und der prinzipielle DESCOMP-Ansatz vorgestellt, der sich in eine lokale und globale Optimierungsphase gliedert. Beide Optimierungsphasen werden in den Abschnitten 4 und 5 beschrieben. In Abschnitt 6 wird die Qualität der vorgestellten Techniken durch einen Vergleich mit einem existierenden automatisch arbeitenden DSE-Ansatz überprüft.

## 2 Modellbildung

In diesem Abschnitt wird das Prozessormodell beschrieben, dessen Parameter an eine Anwendung angepasst werden. Die Zusammenhänge, die zwischen Strom- und Platzverbrauch sowie Leistungsfähigkeit eines solchen Prozessors bestehen, werden zueinander in Beziehung gesetzt. Daraus leiten sich die Gründe für die Wahl der in dieser Arbeit verwendeten Optimierungsstrategie ab. Neben der Definition des Prozessormodells wird auch eine formale Definition für Programmdarstellung und Zusammenhang zwischen Programmdarstellung und Prozessormodell gegeben.

#### 2.1 Prozessormodell

Durch die DSE werden die Parameter eines Prozessors so angepasst, dass eine gegebene Anwendung oder Teile davon innerhalb gewisser Zeitschranken ausgeführt werden können. Die Hardwarekosten und/oder der Stromverbrauch des Prozessors sollen dabei minimiert werden. Außerdem muss sich der angepasste Prozessor leicht in Hardware synthetisieren lassen. Es gibt mehrere Möglichkeiten, die erforderliche Ausführungsgeschwindigkeit der Anwendung auf einem Prozessor zu erreichen:

- durch eine Anpassung der Taktfrequenz des Prozessor,

- durch Optimierungen, die vom Prozessor während der Programmabarbeitung durchgeführt werden,

- durch eine Anpassung der Datenwortbreite des Prozessors,

- durch die parallele Ausführung von Operationen.

Der Erhöhung der Taktfrequenz ist durch die Verzögerung in den Pfaden der Prozessorlogik eine Grenze gesetzt. Um die Taktfrequenz darüber hinaus zu erhöhen, müssen die Verzögerungen auf den Pfaden verkleinert werden, was durch kleinere Strukturgrößen oder Pipelines erreicht werden kann. Kleinere Strukturgrößen erlauben schnellere Transistoren, wodurch auf den Pfaden verkleinern Verzögerungen [91]. Allerdings die Strukturgröße ein Parameter der oft vorgegeben ist und nicht im Rahmen einer DSE bestimmt wird. Skalare Architekturen besitzen eine Pipeline, wodurch lange Pfade in der Prozessorlogik in mehrere kurze Pfade zerlegt werden. Dadurch wird die Verzögerungen auf diesen Pfaden verkleinert und die Möglichkeit geschaffen, Operationen überlappend mit einer höheren Taktfrequenz auszuführen. Mit der Verwendung von Pipelines sind auch Änderungen an der Steuerlogik des Prozessors verbunden, um beispielsweise Konflikte innerhalb der Pipelinestufen zu behandeln. Diese Änderungen führen zu einem irregulären Steuer- und Datenpfad des Prozessors. Ebenso wie die folgenden Optimierungen, die viele superskalare Prozessoren, die gewisse Operationen parallel ausführen können, während der Programmabarbeitung durchführen:

- Sprungvorhersagen, um die Instruktionen von der richtigen Programmposition in den Befehlsdekoder zu laden,

- das Umordnen von Operationen während der Programmausführung, um den Datenpfad und vorhandene Pipelines besser auszulasten, und

- die spekulative Ausführung von Operationen, um Zeitverluste bei bedingten Sprüngen und Speicherzugriffen zu verringern.

Alle diese Maßnahmen zur Erhöhung der Ausführungsgeschwindigkeit bedingen einen sehr komplexen und irregulären Steuer- und Datenpfad, womit die automatische Adaption eines solchen Steuer- und Datenpfades an die Anforderungen einer Anwendung sehr schwierig ist.

Eine Anpassung der Datenwortbreite ist eine weitere Möglichkeit, die Leistungsfähigkeit eines Prozessors an die Anforderungen der Anwendung anzupassen [27, 68]. So kann durch die Wahl einer geeigneten Wortbreite die gewünschte Präzision bei arithmetischen Operationen erreicht werden. Allerdings bietet die alleinige Verwendung dieser Art der Adaption nur eine sehr eingeschränkte Möglichkeit zur Anpassung eines Prozessors an die Anforderungen der Anwendung.

Eine Erhöhung der Parallelität im Prozessor kann durch zusätzliche Operatoren, z. B. weitere ALUs (Arithmetic Logical Unit), erreicht werden. Ein Ansatz, der sich mit der Erhöhung der Parallelität in superskalaren Prozessoren beschäftigt, ist in [75] vorgestellt. Allerdings ist, wie oben bereits beschrieben, das Integrieren weiterer Operatoren in einen irregulären Steuerund Datenpfad einer superskalaren Architekturen schwierig. In [63, 64] werden zur Erhöhung der Parallelität zusätzliche Operatoren in den Datenpfad eines skalierbaren DSPs (Digital Signal Processor) eingebunden. Der existierende DSP-Kern wird so durch zusätzliche Hardware für rechenintensive Anwendungen erweitert. In [38] wurde als zusätzlicher Operator ein FPGA (field programmable gate array) in den Datenpfad des LEON2-Prozessors integriert, um durch dynamische Rekonfiguration des FPGAs rechenintensive Aufgaben auf dieses auszulagern. Ansätze, die zusätzliche Operatoren in die Datenpfade vorhandener Prozessorkerne integrieren, können von dem optimierten Prozessorkern profitieren [64], sind aber bei der Bereitstellung zusätzlicher Parallelität begrenzt, weil die zusätzlichen Operatoren an die vorhandene Registerbank und Speicherinterface des Prozessors angebunden werden müssen oder zu sehr Verbindungsnetzwerken führen, die  $_{

m die}$ Nutzbarkeit zusätzlichen Operatoren für andere Algorithmen erschweren. Die Konzeption

einer massiv parallelen Architektur, die die Unterbringung mehrerer Dutzend Prozessorkerne auf einem Chip unterstützt, ist die EDGE-Architektur (Explicit Data Graph Execution) [25]. Diese Architektur ist allerdings eher für ein sehr breites Spektrum von Anwendungen gedacht und somit nicht zur Adaption an eine spezifische Anwendung geeignet. Darüber hinaus wurde in [69] gezeigt, dass Architekturen mit dieser hohen Parallelität bei vielen Anwendungen aus dem Signalverarbeitungsbereich, was ein Haupteinsatzgebiet anwendungsspezifischer Prozessoren ist, nicht zu einer deutlich besseren Ausführungszeit führen, während Architekturen mit weniger Prozessorkernen, die dafür besser an die Anwendung angepasst sind und ein geeignetes Verbindungsnetzwerk besitzen, höhere Ausführungsgeschwindigkeiten erlauben.

## 2.1.1 Datenpfadmodell

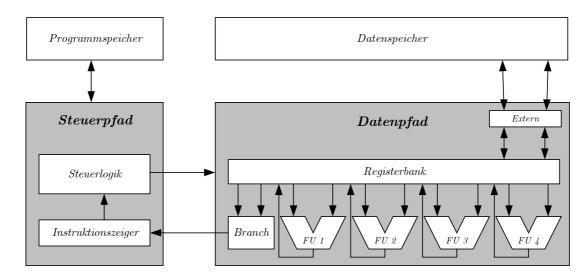

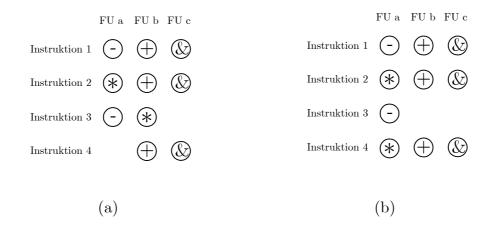

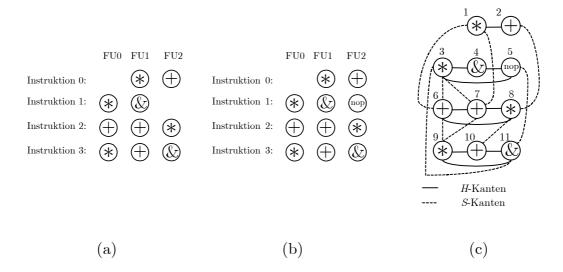

Als Prozessormodell wird in dieser Arbeit ein Very-Long-Instruction-Word-Prozessor (VLIW-Prozessor) gewählt, der sich gut an die algorithmischen Anforderungen einer Anwendung anpassen lässt, indem im Datenpfad die Anzahl der parallel arbeitenden Operatoren und damit die Anzahl der parallel ausführbaren Operationen variiert wird. Außerdem ist der Datenund Steuerpfad dieser Architektur sehr regelmäßig aufgebaut, so dass eine automatisierte Synthese des an eine Anwendung angepassten Steuer- und Datenpfades möglich ist. Wie in [50] beschrieben, kann zur Synthese des Datenpfades beispielsweise auf fertige Komponenten aus einer VHDL-Bibliothek zurückgegriffen werden, aus denen der Datenpfad zusammengesetzt wird. Solche Komponenten sind z. B. Registerbänke, Addierer und Shifter. Die Abbildung 2.1 zeigt den schematischen Aufbau des Steuer- und Datenpfades eines VLIW-Prozessors.

Abbildung 2.1: Steuer und Datenpfad einer einfachen VLIW-Architektur mit einer zentralen Registerbank.

Der Datenpfad enthält eine Registerbank mit allgemeinen Registern. Jede funktionale Einheit (FU) im Datenpfad stellt die Hardware bereit, um gewisse Operationen auszuführen. Die zur Ausführung einer Operation benötigte Hardware in einer FU wird **Operator** genannt. Jeder Operator kann nur Operationen eines bestimmten Typs ausführen, z. B. eine Addition oder eine Multiplikation. Der **Typ** einer Operation v wird mit type(v) bezeichnet. Die Menge aller Operationstypen, für die ein Operator im Prozessor bereitgestellt werden kann, wird  $_{

m mit}$  $\mathcal{O}$ bezeichnet. Für Operationstypen  $t \in \mathcal{O}$  sind die Hardwarekosten opCost(t) bekannt, die zur Implementierung des entsprechenden Operators in Hardware benötigt werden. Diese Hardwarekosten repräsentieren die benötigte Chipfläche, die mit der Anzahl der benötigten Transistoren korreliert. Zur Vereinfachung werden keine Synergieeffekte berücksichtigt. Diese treten beispielsweise auf, wenn in einer FU bereits ein Operator eine Addition implementiert und noch ein Operator für eine Subtraktion implementiert werden soll. Die Subtraktion verursacht dann nur noch geringe zusätzliche Hardwarekosten. Um solche Synergieeffekte zu berücksichtigen, können für die Design-Space-Exploration alle Additions- und Subtraktionsoperationen in Operationen desselben Typs umgewandelt werden, der dann die Kosten des Operators hat, der sowohl eine Addition als auch eine Subtraktion ausführen kann. Jede funktionale Einheiten fasst somit die Operatoren zusammen, die gemeinsam dieselben Ports der Registerbank nutzen<sup>1</sup>. Alle FUs arbeiten parallel und können gleichzeitig auf die Registerbank zugreifen. Jede FU führt aber nur eine Operation gleichzeitig aus. Der Zugriff auf die Registerbank geschieht über die internen Lese- und Schreibports. Jede FU ist durch zwei Leseports und einen Schreibport mit der Registerbank verbunden. Zwei weitere Leseports in der Registerbank werden von der Branch-Einheit verwendet, um abhängig von einem Registerinhalt einen bedingten Sprung durch das Laden eines Wertes in den Instruktionszeiger durchzuführen. Neben den Verbindungen der Registerbank zu den funktionalen Einheiten gibt es auch noch Verbindungen zwischen der Registerbank und externen Speichermedien. Diese greifen über externe Lese- und Schreibports auf die Registerbank zu. In der in Abbildung 2.1 angegebenen einfachen VLIW-Architektur ist das nur der Speicher. Der mit Extern bezeichnete Teil des Datenpfades enthält die benötigten Operatoren für Lese- und Schreibzugriffe auf den Speicher. Dadurch können Daten zwischen der Registerbank und dem Speicher kopiert werden. Es ist zulässig, mehrere Speicherzugriffe gleichzeitig durchzuführen, wie es beispielsweise auch beim Gepard-DSP [27], dem ADSP-21061 [3] und der Lx-Architektur in [73] der Fall ist. Der gleichzeitige Speicherzugriff erfolgt entweder auf getrennte Speicherbänke oder auch auf dieselbe Speicherbank, in der der Daten- und Adressbus mehrfach vorhanden ist. Die Auswahl eines geeigneten Speichermodells wird in dieser Arbeit nicht behandelt.

-

<sup>&</sup>lt;sup>1</sup> In der englischen Literatur auch als *issue slot* bezeichnet.

Gesteuert wird der Datenpfad in jedem Takt durch ein Instruktionswort, wie es in Abbildung 2.2 beispielhaft dargestellt ist.

Abbildung 2.2: Instruktionswort für einen VLIW-Prozessor mit einer Branch-Einheit und vier funktionalen Einheiten im Datenpfad.

In einem solchen Instruktionswort wird an einer festen Position für jede FU im Datenpfad die auszuführende Operation (op1, ..., op4) sowie deren Quellund Zielregister (src, dst) kodiert. Alle Operationen verwenden Prozessorregister als Operanden. Sollen Werte im Speicher manipuliert werden, dann müssen diese über Ladeoperationen zuvor in Register geholt und anschließend zurückgeschrieben werden. Die VLIW-Instruktionen sind statisch geplant. Das bedeutet, dass sie in der Reihenfolge ausgeführt werden, in der sie auftreten. Ein Umordnen der Operationen in den Instruktionen während der Abarbeitung des Programms findet nicht statt. Auch Sprungvorhersagen und die spekulative Ausführung von Operationen werden nicht durchgeführt. Im Steuerpfad des Prozessors müssen die Instruktionen somit nur dekodiert und die Steuersignale an den Datenpfad gegeben werden. Durch die Planung der VLIW-Instruktionen während Operationen inder Erzeugung Zielprogramms durch den Compiler muss sichergestellt sein, dass jede Operation einer FU zugeordnet ist, die sie auch ausführen kann. Da Programm- und Datenspeicher getrennt sind, kann es auch nicht zu Konflikten beim Laden einer Programminstruktion und eines Datums aus dem Datenspeicher kommen. Es entfällt somit ein großer Teil der bei superskalaren Prozessoren notwendigen Steuerlogik. Durch Eigenschaften bietet die VLIW-Architektur gegenüber einer superskalaren Architektur folgende Vorteile:

- Die Ausführungsgeschwindigkeit kann durch zusätzliche FUs im Datenpfad erhöht werden, sofern die Anwendung genügend parallel ausführbare Operationen enthält.

- Daten- und Steuerpfad sind sehr regelmäßig aufgebaut, wodurch sich der angepasste Datenpfad sowie der zugehörige Steuerpfad gut in Hardware synthetisieren lässt.

- Das Zeitverhalten einer statisch geplanten VLIW-Architektur ist gut vorhersagbar, weil die zur Ausführung eines Programms benötigte Anzahl der Takte mit der Instruktionsanzahl korreliert.

Nachteilig wirken sich bei einer statisch geplanten Architektur unvorhersehbare Latenzzeiten von Lade- und Speicheroperationen aus. Beispielsweise wenn ein Wert nicht aus dem Cache geholt werden kann. Dadurch muss die Ausführung aller Operationen – auch der, die nicht datenabhängig von diesem Wert sind – angehalten werden, bis der Wert

verfügbar ist. Aufgrund solcher Verzögerungen kann die Ausführungszeit eines Programms nicht immer exakt aus der Anzahl der abzuarbeitenden Instruktionen bestimmt werden. Das Problem kann aber beispielsweise durch einen an die Speicherzugriffsreihenfolge der Anwendung angepassten Cache oder durch die Unterbringung des Speichers auf dem Chip abgemindert werden [46].

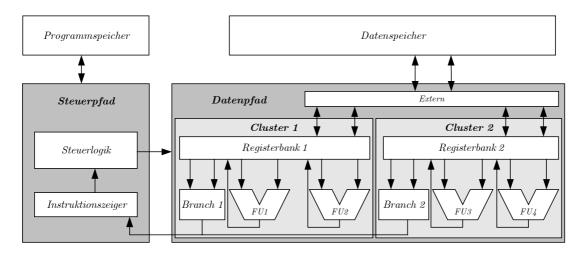

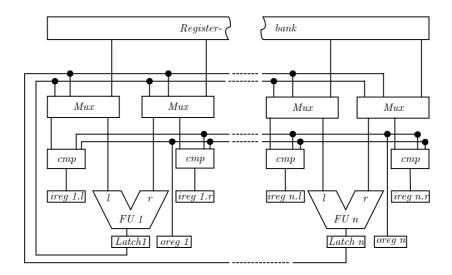

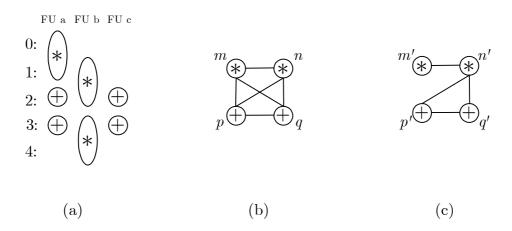

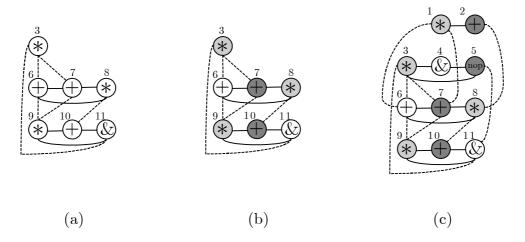

Ein weiteres Problem in VLIW-Architekturen stellt die von der Portanzahl abhängige Komplexität der Registerbank dar, die mit wachsender Parallelität stark zunimmt und den Platz- und Stromverbrauch in einem VLIW-Prozessor dominiert [4, 87]. Um trotz hoher Parallelität die Portanzahl in der Registerbank niedrig zu halten, kann der Datenpfad in Cluster zerlegt werden [49]. Eine schematische Darstellung eines solchen Prozessors ist in Abbildung 2.3 angegeben.

Abbildung 2.3: Steuer- und Datenpfad einer geclusterten VLIW-Architektur.

In einem geclusterten Datenpfad sind die funktionalen Einheiten in Clustern gruppiert. Jeder Cluster besitzt eine lokale Registerbank, auf die nur die funktionalen Einheiten dieses Clusters zugreifen können. Somit bleibt die vom Prozessor bereitgestellte Parallelität hoch, die Anzahl der FUs, die auf dieselbe Registerbank zugreifen, wird aber deutlich reduziert und somit auch die Anzahl der Ports in jeder Registerbank. Der Datenaustausch zwischen verschiedenen Clustern erfolgt über ein Verbindungsnetzwerk, das durch Kopieroperationen gesteuert wird, die im Instruktionswort mit kodiert sind. Da das Kopieren von Daten über dieses Verbindungsnetzwerk Zeit kostet, müssen Operationen in anderen Clustern, die diese Daten benötigen, entsprechend später ausgeführt werden. Somit ist eine geclusterte Architektur nur vorteilhaft, wenn durch die erforderlichen Kopieroperationen die Ausführungszeit der Anwendung nicht beeinträchtigt wird oder die eintretenden Verzögerungen durch eine höhere Taktung des Prozessors ausgeglichen bzw. durch geschickte Anordnung der Kopieroperationen minimiert werden können.

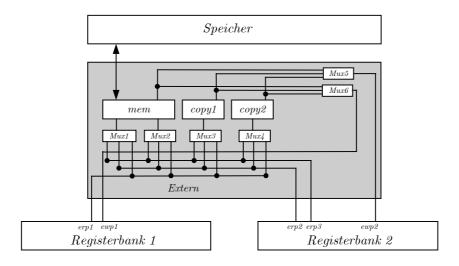

Die Ports der Registerbank, die für den Datenaustausch zwischen den Clustern verwendet werden, sind dieselben, über die auch Speicherzugriffe werden. Die Operatoren für Lade-, durchgeführt Kopieroperationen werden externe Operatoren genannt. Jeder externe Operator bildet eine eigene externe funktionale Einheit. Da die Kopieroperationen in den VLIW-Instruktionen mit kodiert werden, ist es die Aufgabe des Compilers, diese in die VLIW-Instruktionen einzufügen. Wie die externen Ports einer Registerbank durch Speicher- und Kopieroperationen gemeinsam genutzt werden, ist in der Abbildung 2.4 dargestellt. Zugrunde liegt die Idee einer Architektur, die TTA (Transport Triggered Architechture) genannt wird [40, 47]. Ein Port der Registerbank (erp, ewp) ist nicht einem Kopieroperator oder einem Speicheroperator fest zugeordnet, sondern stellt nur den Wert eines Registers bereit.

Abbildung 2.4: Externes Verbindungsnetzwerk für die Kommunikation mit externen Speichermedien und anderen Clustern.

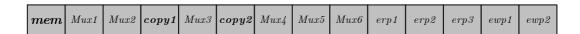

Jeder externe Leseport ist mit allen externen funktionalen Einheiten verbunden, so dass der bereitgestellte Wert von einer oder mehreren externen FUs gleichzeitig verwendet werden kann. Durch einen Multiplexer (Mux) am Eingang jeder externen FU kann der Wert eines Leseports ausgewählt werden. Analog dazu kann durch einen Multiplexer für jeden externen Schreibport der Registerbank ein Wert eines Kopier- oder Speicheroperators ausgewählt werden, der in ein Register geschrieben werden soll. Für jeden externen Port muss die Nummer der anzusprechenden Quell- bzw. Zielregister in der Registerbank kodiert werden. In Abbildung 2.5 ist beispielhaft der Teil des Instruktionswortes dargestellt, der der Steuerung der externen Ports und funktionalen Einheiten dient. Für jede externe FU existieren Operationscodes, die die auszuführende Operation kodieren (mem, copy1, copy2). Zu jedem Operationscode werden die Ports angegeben, von denen die Operanden gelesen werden (Mux1, ..., Mux4) und die externen Operatoren, deren Ergebnisse geschrieben werden sollen (Mux5, Mux6).

Außerdem muss mit jedem externen Leseport (erp1, ..., erp3) und jedem externen Schreibport (ewp1, ewp2) ein Register in der Registerbank assoziiert werden.

Abbildung 2.5: Teil des Instruktionswortes zur Steuerung des externen Verbindungsnetzwerkes.

Für funktionale Einheiten, die nicht gleichzeitig auf dieselbe Registerbank zugreifen oder die eine unterschiedliche Anzahl von Lese- und Schreibports benötigen, ist ein solches auf TTAs basierendes Verbindungsnetzwerk von Vorteil. In diesen Fällen kann derselbe Port in der Registerbank von verschiedenen externen funktionalen Einheiten verwendet werden und nicht jede externe FU benötigt ihre eigenen Ports. Dadurch kann die Anzahl der externen Ports in den Registerbänken verringert werden. Für die Verbindung der internen funktionalen Einheiten mit der Registerbank wird diese Technik nicht genutzt, da gewährleistet sein soll, dass alle FUs gleichzeitig auf die Registerbank zugreifen können und somit die vorhandene Parallelität auch von Anwendungen genutzt werden kann, für die der Prozessor nicht optimiert ist.

## 2.1.2 Pipelinemodell und Bypass

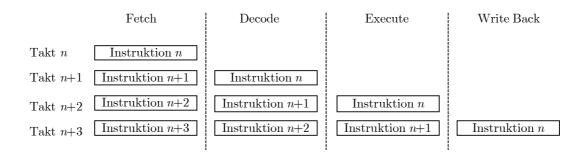

Als Pipelinemodell für den VLIW-Prozessor wird eine einfache 4-stufige Pipeline genutzt, deren Stufen in Abbildung 2.6 dargestellt sind.

Abbildung 2.6: Schematische Darstellung des verwendeten 4-stufigen Pipelinemodells.

In jedem Takt wird die Abarbeitung einer Instruktion in jeder Pipelinestufe abgeschlossen. Eine Instruktion benötigt somit vier Takte um vollständig abgearbeitet zu werden. Aufgrund der vier parallel arbeitenden Pipelinestufen wird im Idealfall pro Takt die Ausführung einer Instruktion beendet. Die vier Stufen der Pipeline sind

- Fetch, zum Laden einer Instruktion aus dem Speicher,

- Decode, zum Dekodieren der Instruktion,

- Execute, zum Ausführen der Operationen durch die FUs und

- Write-Back, zum Zurückschreiben der Ergebnisse der Operationen in die Register.

Die funktionalen Einheiten selbst verfügen nicht über Pipelines. Somit kann eine FU mit der Ausführung einer Operation erst beginnen, wenn die vorangegangene Operation vollständig abgearbeitet wurde. Die Ausführung einer Operation durch eine FU kann mehrere Takte in Anspruch nehmen, wobei die Anzahl dieser Takte als **Latenzzeit** bezeichnet wird. Die Latenzzeit einer Operation ist durch ihren Typ festgelegt und durch die Funktion  $lat: \mathcal{O} \to \mathbb{N}$  gegeben. Führt eine funktionale Einheit eine Operation v mit der Latenzzeit lat(type(v)) aus, dann muss sichergestellt sein, dass in den folgenden lat(type(v)) – 1 Instruktionen diese FU keine weitere Operation ausführen muss. Das sicherzustellen ist ebenfalls eine Aufgabe des Compilers. Dadurch können die folgenden Instruktionen problemlos durch die Pipeline laufen, so dass die übrigen funktionalen Einheiten weiterhin mit Operationen versorgt werden.

Die vorgestellte 4-stufige Pipeline schreibt in der Write-Back-Stufe das Ergebnis einer Operation in die Registerbank zurück. Als Konsequenz kann dieses Ergebnis erst im darauf folgenden Takt als Eingangswert einer FU genutzt werden. Durch diese Restriktion kann sich die Ausführungszeit eines Programms erheblich verlängern. Forwarding ist eine wichtige Technik, um dieses Problem in Pipelinearchitekturen zu vermeiden [48]. Dafür werden mit einem Bypass, wie er in Abbildung 2.7 dargestellt ist, Werte direkt vom Ausgang einer FU an den Eingang einer anderen oder derselben FU weitergeleitet, ohne dass sie zuvor in die Registerbank geschrieben werden müssen. Innerhalb eines Clusters ist immer ein vollständiger Bypass vorhanden. Zwischen FUs verschiedener Cluster gibt es keinen Bypass.

Abbildung 2.7: Schematische Darstellung des Bypasses in einem Cluster.

Im Allgemeinen übernimmt die Hardware des Prozessors die Steuerung des Bypasses. Dafür sind Informationen über die Nummern der Register notwendig, in die die Ergebnisse in der Write-Back-Phase geschrieben und deren Werte gleichzeitig als Operanden in der Execute-Phase benötigt werden. Wird ein Register als Operand benötigt, das gerade erst beschrieben wird, dann muss dieser Wert direkt vom Ausgang zum Eingang der entsprechenden funktionalen Einheiten weitergeleitet werden. Verantwortlich für die Wahl der richtigen Quelle ist ein Multiplexer (Mux) an jedem Eingang einer FU. Um den Multiplexer korrekt zu steuern, wird Hardware (cmp) zum Vergleichen der Registernummern an den linken (l) und rechten (r)Eingängen (ireq) und Ausgängen (oreq) der FUs benötigt. Die Hardware für die Vergleiche kann eingespart werden, wenn der Compiler die Steuerung des Bypasses übernimmt [41, 58]. Voraussetzung dafür ist ein statischer Ablaufplan und die genaue Kenntnis der Pipelinestufen sowie des Bypasses. Der Compiler kann dann für jede Operation festlegen, ob der Quelloperand aus der Registerbank oder dem Latchregister (Latch) am Ausgang einer FU stammt. Die Multiplexer und deren Verdrahtung können dadurch nicht gespart werden.

Eine Pipeline hat auch Auswirkungen auf die Genauigkeit der statischen Laufzeitabschätzung. Bei Sprüngen sind die auf den Sprungbefehl folgenden Instruktionen bereits in die Pipeline geladen worden. Wird der Sprung tatsächlich ausgeführt, müssten diese Instruktionen wieder aus der Pipeline entfernt werden, damit sie nicht ausgeführt werden. Um das zu vermeiden, verarbeitet der Prozessor noch alle Instruktionen, die sich in der Pipeline befinden, und lädt erst nach dem tatsächlichen Ausführen einer Sprungoperation die Instruktionen vom Sprungziel in die Pipeline [27]. Es ist deshalb die Aufgabe des Compilers die Instruktionen unmittelbar nach einem Sprungbefehl mit geeigneten Operationen zu füllen, da diese in jedem Fall noch abgearbeitet werden.

#### 2.1.3 Modell für den Strom- und Platzverbrauch

Wesentliche Optimierungsziele im Bereich der eingebetteten Systeme sind der Strom- und Platzverbrauch. In diesem Abschnitt wird der Zusammenhang zwischen Ausführungsgeschwindigkeit, Platz- und Stromverbrauch eines VLIW-Prozessors beschrieben, woraus sich die während der DSE optimierten Parameter ergeben.

Der Platzverbrauch in einem VLIW-Prozessor wird durch die Registerbänke und den Bypass dominiert und wächst quadratisch mit der Portanzahl in der Registerbank und linear mit der Registeranzahl. Unter der Annahme, dass die Registerbank mindestens so viele Register wie Ports besitzt, ergibt sich ein kubisches Wachstum [87]. Mit steigender Portanzahl in den Registerbänken nimmt im Allgemeinen auch die Anzahl der Operatoren im Prozessor zu, so dass deren Platzbedarf ebenfalls mit wachsender Portanzahl steigt.

Der Stromverbrauch in einer VLIW-Architektur wird im Wesentlichen durch

- den statischen Stromverbrauch,

- den dynamischen Stromverbrauch,

- den Stromverbrauch der Registerbänke und

- die Taktfrequenz

beeinflusst. Auf den statischen Stromverbrauch hat insbesondere bei kleinen Strukturgrößen auch der Platzverbrauch direkten Einfluss. Bei einer 70 Nanometer Technologie entfallen bis zu 50% des Stromverbrauchs in der Schaltung auf statische Leckströme [18], so dass dieser Anteil durch eine Verringerung der Gatter, also des Platzverbrauchs, gesenkt werden kann, wie auch aus der folgenden Formel für den statischen Stromverbrauch hervorgeht [7]:

$$P_{leak} = L_g \cdot V_{dd} \cdot K_3 \cdot e^{K_4 \cdot V_{dd}} \cdot e^{K_5 \cdot V_{bs}} + |V_{bs} \cdot I_{Ju}|. \tag{1.1}$$

In dieser Formel bezeichnet  $L_g$  die Anzahl der Gatter in der Schaltung und  $V_{dd}$  die Versorgungsspannung. Diese beiden Größen können durch die DSE beeinflusst werden.  $V_{bs}$  (body bias voltage),  $I_{Ju}$  (body injunktion leakage) und  $K_i$  (technologieabhängige Konstanten) sind fest vorgegeben. Der dynamische Stromverbrauch  $P_{dyn}$  ist im Wesentlichen von vier Größen abhängig [7]:

$$P_{\rm dyn} = s \cdot C_{\rm eff} \cdot f \cdot V_{\rm dd}^2 \,. \tag{1.2}$$

Hier ist s die Schaltungsaktivität,  $C_{\it eff}$  die umgeladene Kapazität, f die Taktfrequenz des Prozessors und  $V_{\it dd}$  wieder die Versorgungsspannung. Vereinfachend wird angenommen, dass s und  $C_{\it eff}$  für das gleiche Programm konstant sind. Schließlich werden immer dieselben Operationen ausgeführt,

bei verschiedenen VLIW-Architekturen im Allgemeinen in einer unterschiedlichen Reihenfolge. Unter der Annahme, dass der größte Teil der dynamischen Leistungsaufnahme in den funktionalen Einheiten, den Leitungen und der Registerbank auftritt, können die Änderungen in der Schaltungsaktivität, die durch eine andere Abarbeitungsreihenfolge der Operationen entstehen, vernachlässigt werden. Damit ist der dynamische Stromverbrauch von der Taktfrequenz und der Versorgungsspannung abhängig.

Einen sehr hohen Anteil am Stromverbrauch bei VLIW-Architekturen hat die Registerbank des Prozessors. Mit steigender Anzahl der Lese- und Schreibports nimmt der Stromverbrauch und die Zugriffszeit zu [87]. Der Stromverbrauch steigt kubisch mit der Anzahl der Ports in der Registerbank unter der Annahme, dass die Registerbank mindestens so viele Register wie Ports besitzt. Die Abhängigkeit der Zugriffszeit auf die Register von der Anzahl der Ports wird durch die Funktion

$$RFDelay(ports) = ports^{\frac{3}{2}}$$

(1.3)

beschrieben [87]. Die Verzögerungen gehen hauptsächlich auf die Signallaufzeiten in den Leitungen zurück. Diese Laufzeiten treten auch im Bypass des Prozessors auf [98], dessen Größe ebenfalls von der Portanzahl in der Registerbank abhängt. In [96] ist die Abhängigkeit der Verzögerung im Bypass von der Portanzahl als quadratisch angegeben. WDelay(p) soll für die Portanzahl p die größte Verzögerung in der Registerbank bzw. dem Bypass angeben. Die Verzögerungen in den funktionalen Einheiten (FUDelay) entstehen hauptsächlich durch die Verzögerungen in den Gattern. Die größte Verzögerung maxDelay im Prozessor wird somit entweder durch die größte Verzögerung in den funktionalen Einheiten oder die Laufzeiten auf den Leitungen der Registerbank bzw. des Bypasses bestimmt:

$$maxDelay(p) = max(WDelay(p), FUDelay)$$

.

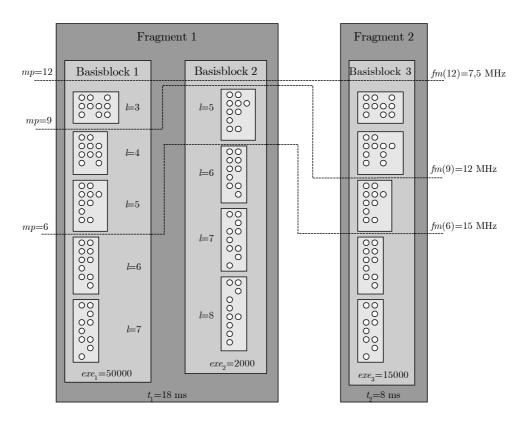

Die maximal mögliche Taktfrequenz eines Prozessors ist umgekehrt proportional zu  $\max Delay(p)$  [97]. Damit lässt sie sich in Abhängigkeit von der Portanzahl einer Registerbank durch die Formel

$$fm(p) = \frac{1}{maxDelay(p)}. (1.4)$$

beschreiben. Dabei berücksichtigt fm die Verzögerungen in den Gattern der FUs, in der Registerbank und dem Bypass. Ab wann die Verzögerung der Registerbank die Verzögerung in den FUs dominiert, hängt wesentlich von der Architektur der funktionalen Einheiten, der Registerbank und der

Fertigungstechnologie ab<sup>1</sup>. Je niedriger die Verzögerung in den Gattern der FUs ist, desto eher dominieren die Signallaufzeiten in der Registerbank. Somit muss eine Erhöhung der Parallelität in der Architektur nicht unbedingt zu einer höheren Ausführungsgeschwindigkeit einer Anwendung führen, weil durch die erhöhte Portanzahl in der Registerbank die maximal mögliche Taktfrequenz des Prozessors sinken kann.

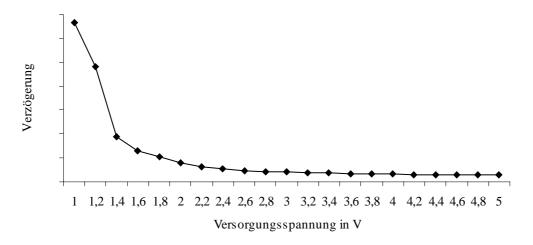

Der Zusammenhang zwischen der Versorgungsspannung  $V_{dd}$  und der Verzögerung in einem Gatter ist durch die folgende Formel aus [97] gekennzeichnet:

$$FUDelay \cong \frac{C_L \cdot V_{dd}}{k_V \cdot W \cdot (V_{dd} - V_T - V_{DSAT})}.$$

(1.5)

$C_L$  bezeichnet die Kapazität.  $k_v$  und W sind Konstanten des Transistors.  $V_T$  (threshold voltage) bewegt sich im Bereich von 0,5V bis 1V.  $V_{DSAT}$  (velocity saturation voltage) ist für  $V_{dd} \geq 2$ V konstant und hat in etwa den Wert von  $V_T$ . Für  $V_{dd} < 2$ V nähert sich  $V_{DSAT}$  asymptotisch dem Wert ( $V_{dd} - V_T$ ) an. Für diese in [97] beschriebenen Zusammenhänge zwischen den Größen ist in Abbildung 2.8 die Abhängigkeit der Verzögerung in den Gattern von der Versorgungsspannung grafisch dargestellt.

Abbildung 2.8: Abhängigkeit der Verzögerung von der Versorgungsspannung.

Mit sinkender Versorgungsspannung nimmt die Verzögerung stark zu. Dieser Zusammenhang zwischen FUDelay und  $V_{dd}$  wird genutzt, um den Stromverbrauch des Prozessors zu verringern [97]. Durch eine erhöhte Parallelität kann die Taktfrequenz abgesenkt werden, weil der Prozessor

\_

<sup>&</sup>lt;sup>1</sup> Die Zusammenhänge zwischen diesen Größen sind vor der Design-Space-Exploration bekannt, weil sie für die Komponenten, aus denen der Datenpfad zusammengesetzt wird, ermittelt wurden [68].

trotzdem die gleiche Menge von Operationen innerhalb eines festen Zeitraums verarbeiten kann. Aufgrund der verringerten Taktfrequenz kann auch die Versorgungsspannung heruntergesetzt werden, weil jetzt eine höhere Verzögerung in den FUs akzeptiert werden kann. Insbesondere das Absenken der Versorgungsspannung geht quadratisch in die Verringerung des dynamischen Stromverbrauchs  $P_{dyn}$  ein. Durch die erhöhte Parallelität wächst aber der Platz- und Stromverbrauch in den Registerbänken kubisch. Außerdem steigt der Platzverbrauch durch zusätzliche Operatoren und damit auch  $P_{leak}$ . Es ist deshalb nur sinnvoll, die Parallelität solange zu erhöhen, bis die Verringerung des dynamischen Stromverbrauchs geringer ist als die Erhöhung des statischen Stromverbrauchs und des Stromverbrauchs in den Registerbänken. Außerdem darf die Parallelität nur solange erhöht werden, wie trotz der dadurch sinkenden maximal möglichen Taktfrequenz des Prozessors die geforderten Ausführungszeiten eingehalten werden.

Der Platzverbrauch, Stromverbrauch und die Taktfrequenz eines VLIW-Prozessors hängen somit wesentlich von der Portanzahl in seinen Registerbänken ab, genauso wie die verfügbare Parallelität, da die Anzahl der parallel arbeitenden FUs in direktem Zusammenhang mit der Portanzahl in den Registerbänken steht. Die in dieser Arbeit gewählte Optimierungsstrategie konzentriert sich deshalb auf die Minimierung der Ports in den Registerbänken und besonders auf die Minimierung der maximalen Portanzahl der Registerbänke.

## 2.1.4 Formales Prozessormodell

Aufgrund der Unterscheidung von internen und externen Ports in der Registerbank werden auch die Operatoren unterschieden, die über die internen bzw. externen Ports mit der Registerbank verbunden sind. Interne Operatoren haben nur auf die internen Ports der Registerbank Zugriff und externe Operatoren nur auf die externen Ports. Entsprechend werden die funktionalen Einheiten, die nur interne Operatoren besitzen dürfen, interne funktionale Einheiten genannt. Die Typen der mit den internen Operatoren ausführbaren Operationen werden mit  $\mathcal{O}_I$  bezeichnet.  $\mathcal{O}_E$  bezeichnet die Typen der durch die externen Operatoren ausführbaren Operationen. Es gilt  $\mathcal{O}_{I} \cap \mathcal{O}_{E} = \varnothing \quad \text{und} \quad \mathcal{O} = \mathcal{O}_{I} \cup \mathcal{O}_{E}, \quad \text{wobei} \quad \mathcal{O}_{E} = \{\mathit{copy}, \quad \mathit{load}, \quad \mathit{store}\} \quad \text{und}$  $\{nop\} \subset \mathcal{O}_{I}$ , copy ist der Typ des Operators, der einen Registerinhalt aus einem Cluster in einen anderen Cluster kopiert. load und store bezeichnen die Typen der Operatoren zum Laden und Speichern von Werten aus dem bzw. in den Arbeitsspeicher und nop ist der Typ einer Operation ohne Wirkung. Die Latenzzeiten der externen Operatoren modellieren die Speicherzugriffszeit und die Zeit zum Kopieren von Werten zwischen verschiedenen Clustern. Ein geclusterter VLIW-Prozessor wird durch das Tupel

$$(C, \mathcal{F}, cf, ft, rz, rpc)$$

beschrieben. Es ist

- $\mathcal{C} \neq \emptyset$  die Menge der Cluster, auch **Prozessorcluster** genannt, und

- $\mathcal{F} \neq \emptyset$  die Menge der funktionalen Einheiten im Prozessor.

- $cf: \mathcal{C} \to \wp(\mathcal{F})$  modelliert den Datenpfad, indem den internen Clustern eine Menge interner funktionaler Einheiten zugeordnet wird und genau einem Cluster die Menge der externen funktionalen Einheiten. Verschiedene Cluster c und c' bestehen aus disjunkten FU-Mengen:

$$cf(c) \cap cf(c') \neq \emptyset \Rightarrow c = c'.$$

- $ft: \mathcal{F} \to \wp(\mathcal{O})$  ordnet jeder internen FU eine Menge von internen Operationstypen zu, wodurch die in jeder FU implementierten Operatoren festgelegt sind und jeder externen FU eine Einermenge von Operationstypen. Diese Zuordnung wird **Ressourcenallokation** genannt und legt den Typ ft(f) einer FU f fest. Eine FU enthält für jeden Operationstypen höchstens einen Operator.

- $rz: \mathcal{C} \to \mathbb{N}$  beschreibt die Anzahl der Register in den Registerbänken der einzelnen Cluster und

- $rpc: \mathcal{C} \to \mathbb{N} \times \mathbb{N} \times \mathbb{N}$  modelliert die **Portkonfiguration** der Registerbank eines Clusters. Dadurch ist die Anzahl der internen Ports (ip) sowie der externen Lese-(rp) und Schreibports (wp) durch rpc(c) = (ip, rp, wp) in einem Cluster c festgelegt.

Die Anzahl der internen Ports entspricht dem Dreifachen der FU-Anzahl im Cluster. Auf die Modellierung der Branch-Einheit wird im Weiteren verzichtet, da diese in jedem Cluster zwei Ports benötigt. Ein Drittel der internen Ports sind Schreibports und zwei Drittel Leseports. Der Cluster e, der ausschließlich externe Operatoren enthält, besitzt keine Registerbank. Somit sind rpc(e) = (0, 0, 0) und rz(e) = 0. Ein Prozessor  $(\mathcal{C}, \mathcal{F}, cf, ft, rz, rpc)$  kann mehrere identische Cluster und jeder Cluster mehrere identische funktionale Einheiten besitzen. Die Menge aller so beschreibbaren Prozessoren zu einer festen Operationstypenmenge  $\mathcal{O}$  bildet den Suchraum, in dem durch die Design-Space-Exploration ein geeigneter Prozessor für eine gegebene Anwendung gesucht wird.

Die Hardwarekosten eines VLIW-Prozessors  $P = (\mathcal{C}, \mathcal{F}, cf, ft, rz, rpc)$  setzen sich aus zwei Komponenten zusammen:

$$VLIWCost(P) = DPCost(P) + RFCost(P)$$

. (1.6)

Die **Datenpfadkosten** *DPCost* ergeben sich aus den Datenpfadkosten der Cluster in der Architektur und umfassen nur die Kosten, die durch die Operatoren in den FUs entstehen:

$$DPCost((C, \mathcal{F}, cf, ft, rz, rpc)) = \sum_{c \in C} ClusterCost(c, cf, ft).$$

(1.7)

ClusterCost summiert die Kosten der funktionalen Einheiten in einem Cluster c auf:

$$ClusterCost(c, cf, ft) = \sum_{f \in cf(c)} FUCost(f, ft).$$

(1.8)

Durch den Ausschluss von Synergieeffekten werden die Kosten einer funktionalen Einheit f durch die Summe der Kosten der in f implementierten Operatoren berechnet:

$$FUCost(f, ft) = \sum_{o \in ft(f)} op Cost(o).$$

(1.9)

Diese Formel beschreibt annähernd die Hardwarekosten eines Prozessors, der aus Hardwaremodulen zusammengesetzt wird [50]. Wie in 2.1.3 bereits erläutert, sind die Kosten einer Registerbank quadratisch von der Anzahl der Ports (ip + rp + wp) und linear von der Anzahl der Register regs [87] abhängig. Damit können die Hardwarekosten einer Registerbank mit regs vielen Registern und der Portkonfiguration (ip, rp, wp) durch

$$RFCCost(regs,(ip,rp,wp)) = \rho \cdot (ip + rp + wp)^2 \cdot regs$$

berechnet werden, wobei  $\rho$  die Kosten einer Registerbank mit einem Register und einem Port sind. Da eine Registerbank in der Praxis mindestens so viele Register wie Ports bereitstellt, wächst RFCCost mindestens kubisch. Die Gesamtkosten aller Registerbänke sind dann

$$RFCost((\mathcal{C}, \mathcal{F}, cf, ft, rz, rpc)) = \sum_{c \in \mathcal{C}} RFCCost(rz(c), rpc(c)). \tag{1.10}$$

Die Hardwarekosten für das Verbindungsnetzwerk zwischen den Clustern sowie den Clustern und dem Arbeitsspeicher hängen von der Anzahl der externen Operatoren ab. Die dadurch anfallenden Kosten für das Verbindungsnetzwerk werden in den Kosten der entsprechenden Operationstypen mit berücksichtigt und gehen somit durch die Kostenfunktion (1.9) in den Wert von *VLIWCost* ein.

## 2.2 Programmmodell

Nachdem im vorangegangenen Abschnitt das Prozessormodell vorgestellt wurde, dessen Parameter durch die Design-Space-Exploration angepasst werden, wird in diesem Abschnitt das Modell eingeführt, mit dem die Anwendung, an die der Prozessor angepasst werden soll, beschrieben wird. Ziel ist es, bereits durch die Formalisierung den Grundgedanken des DESCOMP-Ansatzes zum Ausdruck zu bringen, nämlich dass aus der Anwendung ein dafür speziell geeigneter Prozessor abgeleitet wird. Deshalb sollen die im vorangegangenen Abschnitt angegebenen Parameter des Prozessors auch mittels des Programmmodells beschreibbar sein.

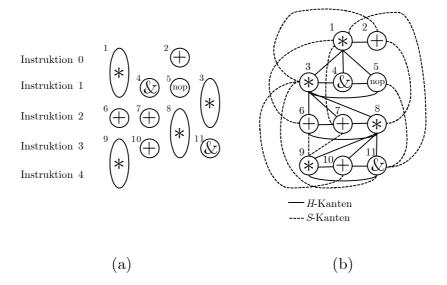

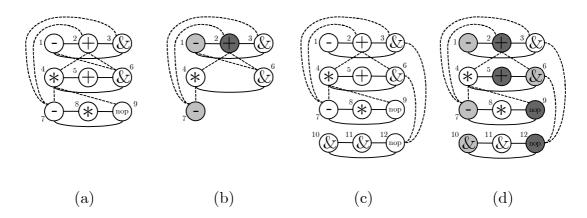

Die Anwendung besteht aus einer Menge von Basisblöcken [8]. Weil die Leistungsfähigkeit eines VLIW-Prozessors überwiegend davon abhängt, wie gut er sich zur parallelen Abarbeitung der Operationen in den einzelnen Basisblöcken eignet, wird er für die Abarbeitung dieser Basisblöcke optimiert. Die Abarbeitungsreihenfolge der Basisblöcke wird während der DSE mit DESCOMP vernachlässigt. Es werden nur Informationen über die Ausführungshäufigkeiten der einzelnen Basisblöcke benötigt, die in einer vorangegangenen Simulationsphase ermittelt wurden. Obwohl nur Basisblöcke modelliert werden, können Basisblocktransformationen zur Erhöhung der Parallelität, wie z. B. das Entrollen von Schleifen [8] oder das Bilden von Basisblockketten, sogenannter Traces, wie beim Trace-Scheduling [51], vorher durchgeführt werden. Der Prozessor kann dann für die Basisblöcke optimiert werden, die aus den entsprechenden Transformationen entstanden sind. Ein Basisblock ist eine Menge von Operationen aus dem Quellprogramm, die beim Betreten des Basisblocks alle abgearbeitet werden. Die Reihenfolge, in der die Operationen eines Basisblocks abgearbeitet werden, ist im Allgemeinen nur partiell festgelegt. Zur Darstellung wird deshalb ein gerichteter azyklischer Graph genutzt, der die partielle Ordnung über den Operationen modelliert.

### Definition 2.1 (Basisblock)

Ein Basisblock b = (V, E, type) ist ein gerichteter azyklischer Graph mit der Knotenmenge V, der Kantenmenge  $E \subseteq V \times V$  und der Beschriftungsfunktion  $type: V \to \mathcal{O}$ .

Ein Knoten  $v \in V$  wird auch **Operationsknoten** (oder kurz Operation) genannt. Operationen können direkt von einer FU des Prozessors ausgeführt werden. In der gesamten Arbeit werden V und E für die Knoten- bzw. Kantenmenge eines Basisblocks verwendet. Um zu verdeutlichen, dass V oder E zu einem Basisblock b gehören, werden beide Mengen bei Bedarf mit bindiziert. Der Operationstyp eines Operationsknotens v ist durch type(v)bestimmt. Die Kantenmenge E ist die Vereinigung zweier disjunkter Kantenmengen D und A. Durch D werden **Datenabhängigkeiten** dargestellt. Eine Kante  $(u, v) \in D$  gibt es genau dann, wenn die Operation v das Ergebnis der Operation u benötigt. Dieser Wert muss in einem Register gehalten werden. Es kann im Programm aber noch Reihenfolgebedingungen zwischen Speicher- und Leseoperationen geben, die nicht durch eine Datenabhängigkeit verursacht werden. So muss z. B. eine Leseoperation nach einer Speicheroperation ausgeführt werden, wenn beide Operationen auf denselben Speicherplatz zugreifen und die Leseoperation den von der Speicheroperation geschriebenen Wert lesen soll. Analog dazu muss die Reihenfolge zweier Speicheroperationen beachtet werden, wenn diese denselben Speicherplatz beschreiben, damit nach der letzten Schreiboperation der richtige Wert im Speicher steht. Diese Abhängigkeiten in der Reihenfolge werden durch Kanten in der Menge A modelliert. Ein Knoten v ist abhängig vom Knoten w, falls  $(w, v) \in E^+$ , wobei  $E^+$  der transitive Abschluss der Relation E ist. v wird auch **Nachfahre** von w und w **Vorfahre** von v genannt. Für  $(w, v) \in E$  wird v **Nachfolger** von w und w **Vorgänger** von v genannt.

#### Definition 2.2 (Pfad)

Ein Pfad  $\pi = v_1...v_n$  im Basisblock b = (V, E, type) mit  $n \ge 1$  ist eine Folge von Knoten, so dass  $\forall i \in \mathbb{N} : 1 \le i < n \Rightarrow (v_i, v_{i+1}) \in E$ .

## Definition 2.3 (Pfadlänge)

Die Länge eine Pfades  $\pi=v_1...v_n$  im Basisblock ist die Summe der Latenzzeiten seiner Operationen und ist definiert als

$$pl(\pi) = \sum_{i=1}^{n} lat(type(v_i)).$$

## Definition 2.4 (kritischer Pfad, kritische Pfadlänge)

Ein Pfad  $\pi$  ist ein kritischer Pfad im Basisblock b, falls für alle Pfade  $\pi'$  in b gilt:  $pl(\pi') \leq pl(\pi)$ . Die Länge eines kritischen Pfades  $\pi$  wird kritische Pfadlänge von b genannt, kurz cp(b).

#### Definition 2.5 (Instruktion)

Eine Menge von Operationen  $i \subseteq V$  wird Instruktion genannt.

### Definition 2.6 (Ablaufplan)

Ein Ablaufplan der Länge l zu einem Basisblock b ist eine Folge von Instruktionen. Diese Folge wird durch eine Funktion  $\alpha: \{0, ..., l-1\} \to \wp(V_b)$  beschrieben, die den folgenden Bedingungen genügen muss:

- $\bullet \quad V_{{\boldsymbol b}} = \bigcup_{0 \le i < l} \alpha(i) \,,$

- $\forall i \in \{0,...,l-1\} \Rightarrow \alpha(i) \neq \emptyset$ .

- Jede Operation v kommt in genau lat(type(v)) vielen Instruktionen vor:  $\forall v \in V_b : \left|\left\{ \begin{array}{cc} i & | & i \in \{0,\dots,l-1\} \land v \in \alpha(i) \right\} \right| = lat(type(v)). \end{array} \right.$

- Diese Instruktionen müssen aufeinander folgend sein:

$$\forall v \in V_b \max \{i \mid v \in \alpha(i)\} - \min \{i \mid v \in \alpha(i)\} = lat(type(v)) - 1.$$

• Die Abhängigkeiten im Basisblock b werden durch den Ablaufplan berücksichtigt, d. h.,

$$\forall u,v \in V: (u,v) \in E \Rightarrow \max \left\{ j \middle| \ u \in \alpha(j) \right\} < \min \left\{ i \middle| \ v \in \alpha(i) \right\}.$$

Für die Instruktion  $\alpha(i)$  wird auch kurz i geschrieben. Die Länge des Ablaufplans  $\alpha$  wird auch mit  $|\alpha|$  bezeichnet. Gemäß dem Prozessormodell wird in jeder Pipelinestufe in jedem Takt eine Instruktion abgearbeitet. Ein Ablaufplan der Länge l kann mit dem vorgestellten Prozessormodell somit in genau l+3 Takten abgearbeitet werden, wenn sich die erste Instruktion des Ablaufplans noch nicht in der ersten Pipelinestufe befindet. Befinden sich bei einer zyklischen Abarbeitung des Basisblocks die ersten drei Instruktionen bereits in der Pipeline, so werden genau l Takte zur Abarbeitung von  $\alpha$ benötigt. Von diesem Fall wird bei den weiteren Betrachtungen ausgegangen, da das vorgestellte Pipelinemodell dem Compiler erlaubt, Sprungoperation folgenden Instruktionen zur Planung von Operationen zu nutzen. Eine Instruktion entspricht somit genau einem Takt. Auf die Modellierung einer Sprungoperation, die im Allgemeinen einen Basisblock abschließt, wurde verzichtet, weil sie keinen wesentlichen Einfluss auf die DSE hat. Es muss lediglich sichergestellt sein, dass die Sprungoperation immer in der Instruktion l-3 beginnt. Dann entspricht die Länge des Ablaufplans der benötigten Taktanzahl für seine Abarbeitung, auch wenn durch die Sprungoperation eine Verzweigung an eine andere Programmposition erfolgt. Der in Abschnitt 4.1 vorgestellte Planungsalgorithmus unterstützt die Erzeugung eines Ablaufplans, der die Sprungoperation an einer festen Position enthält.

Die Länge eines längsten Ablaufplans  $\alpha$  zu einem Basisblock b wird mit lp(b) bezeichnet und ist definiert als  $pl(v_1...v_m)$ , wobei  $V_b = \{v_1, ..., v_m\}$ . Einem Basisblock b können Ablaufpläne mit den Längen cp(b) bis lp(b) zugeordnet werden. Kürzere Ablaufpläne existieren für b nicht, da dann die Datenabhängigkeiten im Basisblock nicht beachtet werden können. Längere Ablaufpläne existieren ebenfalls nicht, da es dann eine leere Instruktion i gäbe. Die Latenzzeit einer Operation wird im Ablaufplan dadurch modelliert, dass die betreffende Operation in lat(type(v)) vielen aufeinander folgenden Instruktionen enthalten ist. Das bedeutet aber nicht, dass in jeder dieser Instruktionen mit der Ausführung der Operation begonnen wird. Vielmehr wird dadurch modelliert, dass in jeder der Instruktionen eine FU mit der Ausführung dieser Operation beschäftigt ist. Gleichzeitig ist dadurch sichergestellt, dass diese FU keine weitere Operation ausführen kann.

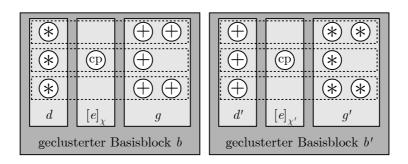

Um die Cluster eines VLIW-Prozessors zu modellieren, wird die Knotenmenge V eines Basisblocks durch eine Äquivalenzrelation  $\chi \subseteq V \times V$ in Äquivalenzklassen zerlegt. Zwei Knoten u und v stehen genau dann in Relation, wenn sie von der Zielarchitektur im selben Cluster ausgeführt werden sollen. Die Zerlegung  $V/\chi$  wird Clusterung genannt. Jede Äquivalenzklasse  $[v]_{\chi} \in V/\chi$  entspricht einem Cluster im Prozessor und wird deshalb ebenfalls als Cluster oder auch als Basisblockcluster bezeichnet. Um Daten zwischen zwei Clustern auszutauschen, ist eine explizite Kopieroperation im Basisblock erforderlich. Kopieroperationen werden im Basisblock durch entsprechende Knoten v mit type(v) = copy modelliert. Alle Kopier-, Lese- und Speicheroperationen des Basisblocks werden in einer Klasse zusammengefasst. Um zu einem Basisblock b den um die Kopieroperationen erweiterten Basisblock  $b_{\chi}$  zu konstruieren, muss beachtet werden, dass derselbe Wert nicht mehrmals in denselben Cluster kopiert werden soll, wenn er dort von mehreren Operationen benutzt wird. Es wird deshalb die Relation  $\sim_u \subseteq V \times V$  definiert, die zwei Knoten v und w aus demselben Cluster genau dann in Relation setzt, wenn sie einen gemeinsamen Vorgänger u in einem anderen Cluster haben:

$$w \sim_u v :\Leftrightarrow [w]_\chi = [v]_\chi \wedge \exists u \in V : [u]_\chi \neq [w]_\chi \wedge (u,w) \in D \wedge (u,v) \in D \ .$$

Die Menge

$$[u,v]_{\sim} := \{w | v \sim_u w\}$$

enthält alle Knoten, die paarweise durch  $\sim_u$  in Relation gesetzt werden und modelliert somit genau eine Kopieroperation. Der um die Kopieroperationen erweiterte Basisblock  $b_{\chi}$  wird geclusterter Basisblock genannt und geht aus b hervor, indem zwischen zwei Knoten  $(u, v) \in D$ , die sich in unterschiedlichen Clustern befinden, der Kopierknoten  $[u, v]_{\sim}$  eingefügt wird.

#### Definition 2.7 (geclusterter Basisblock)

Ein geclusterter Basisblock  $b_{\chi} = (V', E', type')$  entsteht aus dem Basisblock b = (V, E, type) mit  $E = D \cup A$  und der Clusterung  $\chi$ , indem

• V um die Menge der benötigten Kopieroperationen erweitert wird:

$$V' = V \cup \left\{ [u, v]_{\sim} \,\middle|\, (u, v) \in D \text{ und } (u, v) \not\in \chi \right\} \text{ und}$$

$$type'(v) = \begin{cases} type(v), \text{ falls } v \in V \\ copy, \text{ sonst} \end{cases}$$

• und die Kante  $(u, v) \in E$  entfernt wird, wenn  $[u]_{\chi} \neq [v]_{\chi}$  und die Datenabhängigkeit zwischen u und v über den eingefügten Kopierknoten  $[u, v]_{\sim}$  hergestellt wird:

$$E' = E - \left\{ (u, v) \middle| \ u, v \in V \text{ und } [u, v]_{\sim} \in V' \right\} \cup$$

$$\left\{ (u, [u, v]_{\sim}) \middle| \ u, v \in V \text{ und } [u, v]_{\sim} \in V' \right\} \cup$$

$$\left\{ ([u, v]_{\sim}, w) \middle| \ [u, v]_{\sim} \in V' \land w \in [u, v]_{\sim} \right\}.$$

Jeder Wert wird so nur einmal kopiert. Alle eingefügten Kopieroperationen werden bei den folgenden Betrachtungen wie normale Operationsknoten behandelt. Die Ausführungszeit einer Kopieroperation wird durch ihre Latenzzeit modelliert. Dadurch ist sichergestellt, dass das Kopieren eines Wertes in einen Cluster abgeschlossen ist, bevor er dort verwendet wird. Der Begriff des Ablaufplans und der Instruktion lässt sich somit ohne Probleme auf geclusterte Basisblöcke anwenden. Allerdings muss die Clusterung  $\chi$  für

den Basisblock b auf die Kopieroperationen im geclusterten Basisblock ausgeweitet werden. Alle Kopieroperationen werden zusammen mit den loadund store-Operationen in dem Cluster für externe Operationen ausgeführt. Es ergibt sich somit die erweiterte Clusterung:

$$\chi := \chi \cup \{(u,v) | u,v \in V' \land type(u), type(v) \in \mathcal{O}_E \}.$$

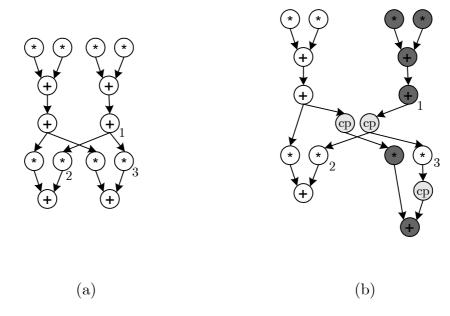

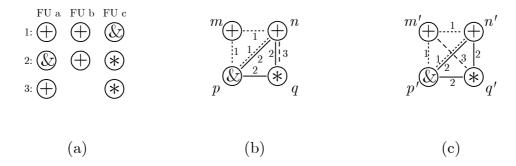

Der so modellierte Cluster, der alle externen Operationen des Basisblocks enthält, wird mit  $[e]_{\chi}$  bezeichnet. Wenn in dem geclusterten Basisblock keine Lade-, Speicher- oder Kopieroperationen auftreten, dann ist die Menge  $[e]_{\chi}$  leer und nicht in der Zerlegung  $V/\chi$  enthalten. Ein Beispiel ist in der folgenden Abbildung 2.9 angegeben.

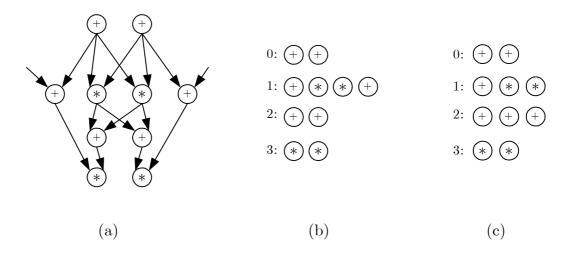

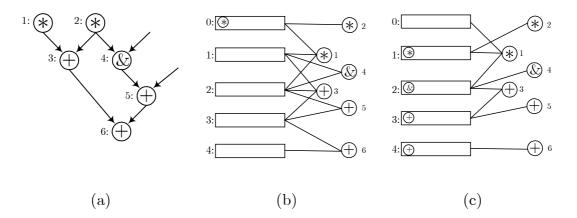

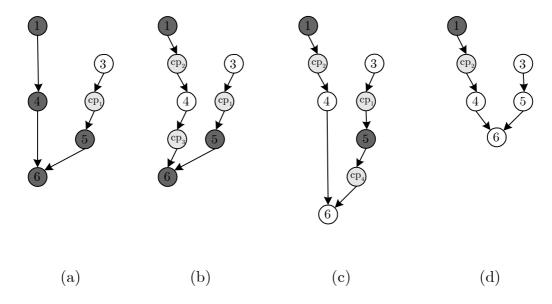

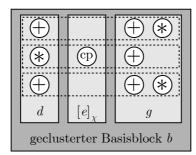

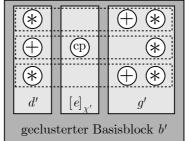

Abbildung 2.9: (a) Nicht geclusterter Basisblock; (b) Geclusterter Basisblock mit eingefügten Kopieroperationen.

In Abbildung 2.9 (a) ist ein nicht geclusterter Basisblock dargestellt. In Abbildung 2.9 (b) ist derselbe in zwei Cluster zerlegte Basisblock dargestellt. Durch  $\chi$  sind alle gleichfarbigen Knoten miteinander in Beziehung gesetzt. Kanten, die zwei Knoten aus verschiedenen Clustern verbinden, wurden entfernt und durch Kopieroperationen (cp) ersetzt. Die Kopieroperationen bilden selbst einen eigenen Cluster. Der Wert, der durch die Operation 1 erzeugt wird, wird nur einmal kopiert. Es ist deshalb  $[1,2]_{\sim} = [1,3]_{\sim} = \{2,3\}$  der entsprechende Kopierknoten. Die kritische Pfadlänge des Basisblocks in (b) ist in dem angegebenen Beispiel um die Latenzzeit von zwei Kopieroperation angewachsen.

Analog zur Clusterung wird jetzt die Zuordnung der Operationen zu funktionalen Einheiten modelliert. Durch die Relation  $\phi \subseteq V \times V$  werden zwei Knoten u und v genau dann in Relation gesetzt, wenn sie in der

Zielarchitektur von derselben funktionalen Einheit ausgeführt werden sollen. Alle Knoten einer Äquivalenzklasse  $[v]_{\phi} \in V/\phi$  sind bei ihrer Ausführung an die gleiche funktionale Einheit gebunden. Die Zerlegung  $V/\phi$  wird deshalb auch **Bindung** genannt. Da jede Äquivalenzklasse  $f \in V/\phi$  einer funktionalen Einheit im Prozessor entspricht, wird der Begriff funktionale Einheit auch für die Äquivalenzklasse f verwendet. Da Operationen, die der gleichen FU zugeordnet sind, auch im gleichen Cluster liegen, gilt  $\phi \subseteq \chi$ .

Bereits aus einer Clusterung und einem Ablaufplan lassen sich Mindestanforderungen an die Parameter eines Prozessors, der den Ablaufplan abarbeiten soll, ableiten. So kann neben der Anzahl der internen Cluster, die  $|V/\chi - \{[e]\}_{\chi}|$  beträgt, die Anzahl der durch eine Instruktion  $\alpha(i)$  beanspruchten funktionalen Einheiten in jedem Cluster  $c \in V/\chi$  durch die Instruktionsbreite

$$FUCIWidth(\alpha(i), c) = |c \cap \alpha(i)|$$

bestimmt werden. Daraus lässt sich die **Clusterbreite** berechnen, die durch die größte Instruktionsbreite in einem Cluster festgelegt ist:

$$FUCWidth(\alpha, c) = \max \left\{ FUCIWidth(\alpha(i), c) | \ 0 \le i < |\alpha| \right\}.$$

Als **Ablaufplanbreite** wird die größte Anzahl funktionaler Einheiten in einem Cluster bezeichnet:

$$FUWidth(\alpha, \chi) = \max \left\{ FUCWidth(\alpha, c) \middle| c \in (V / \chi - \{[e]_{\chi}\}) \right\}.$$

Aus der Clusterbreite lässt sich auch unmittelbar die Anzahl der benötigten internen Lese- und Schreibports in der Registerbank, die **interne Registerbankgröße**, des Clusters c

$$iPCWidth(\alpha, \chi, c) = \begin{cases} 3 \cdot FUCWidth(\alpha, c), \text{ falls } c \neq [e]_{\chi} \\ 0, \text{ sonst} \end{cases}$$

ableiten. Die **Größe einer Registerbank** PCWidth eines Clusters berücksichtigt auch noch die Anzahl der externen Lese- und Schreibports erPWidth und ewPWidth in der Registerbank:

$$PCWidth(\alpha, \chi, c) = iPCWidth(\alpha, \chi, c) + erPWidth(\alpha, \chi) + ewPWidth(\alpha, \chi).$$

Obwohl die Architektur eine unterschiedliche Anzahl externer Lese- und Schreibports in jeder Registerbank zulässt, wird diese Eigenschaft nicht genutzt, da das Verbindungsnetzwerk dadurch unflexibler und irregulär wird. Jede Registerbank stellt deshalb dieselbe Anzahl externer Lese- (erPWidth) und Schreibports (ewPWidth) zur Verfügung, die sich aus der maximal verwendeten Anzahl externer Lese- (rPC) bzw. Schreibports (wPC) in einer der Registerbänke ergibt:

$$erPWidth(\alpha, \chi) = \max \{ rPC(\alpha, \chi, c) | c \in V / \chi - \{ [e]_{\chi} \} \}$$

und

$$\mathit{ewPWidth}(\alpha,\chi) = \max \left\{ \mathit{wPC}(\alpha,\chi,c) \middle| \ c \in V \, / \, \chi - \{[e]_\chi\} \right\}.$$

Die von  $\alpha$  maximal verwendete Anzahl externer Lese- und Schreibports in der Registerbank des Clusters c ist

$$rPC(\alpha, \chi, c) = \max \{rPCI(\alpha(i), \chi, c) | 0 \le i < |\alpha| \} \text{ und}$$

(1.11)

$$wPC(\alpha, \chi, c) = \max \left\{ wPCI(\alpha(i), \chi, c) | 0 \le i < |\alpha| \right\}, \tag{1.12}$$

wobei rPCI und wPCI die Anzahl der benötigten externen Lesebzw. Schreibports in der Instruktion i im Cluster c ist. Die Anzahl der in Instruktion i gleichzeitig benutzten externen Leseports in der Registerbank des Clusters c kann aus den Operationen, die in dieser Instruktion im externen Cluster ausgeführt werden und einen Wert aus dem Cluster c lesen, durch

$$rPCI\left(\alpha\left(i\right),\chi,c\right) = \sum_{u \in \left(\alpha\left(i\right) \cap [e]_{\chi}\right) \land \atop \exists w \in c: \left(w,u\right) \in D} readPorts\left(type\left(u\right)\right)$$

berechnet werden, wobei readPorts(t) die Anzahl der von einer Operation des Typs t verwendeten externen Leseports ist. Jede Kopieroperation benötigt dabei einen Lese- und einen Schreibport. Zur Ausführung einer load-Operation wird ebenfalls ein Leseport, zum Laden der Speicheradresse aus einem Register, und ein Schreibport, zum Speichern des gelesenen Wertes in ein Register, benötigt. Eine store-Operation dagegen benötigt keinen Schreib-, dafür aber zwei Leseports, um die Adresse und den zu schreibenden Wert aus der Registerbank zu lesen. Es ist deshalb

readPorts(copy) = writePorts(copy) = readPorts(load) = writePorts(load) = 1 und

$$readPorts(store) = 2$$

und  $writePorts(store) = 0$ .

Analog zur Anzahl der Leseports wird die Anzahl der externen Schreibports in Instruktion i im Cluster c berechnet:

$$wPCI(\alpha(i), \chi, c) = \sum_{\substack{u \in (\alpha(i) \cap [e]_{\chi}) \land \\ \exists w \in c: (u, w) \in D}} writePorts(type(u)).$$

Die insgesamt vorhandene Anzahl externer Lese- und Schreibports in jeder Registerbank wird mit

$$ePWidth(\alpha, \chi) = erPWidth(\alpha, \chi) + ewPWidth(\alpha, \chi)$$

bezeichnet. Die Portanzahl in der größten Registerbank des Prozessors ist

$$PWidth(\alpha, \chi) = \max \left\{ PCWidth(\alpha, \chi, c) \middle| c \in V / \chi - \left\{ [e]_{\chi} \right\} \right\}.$$

Daraus lässt sich die maximal mögliche Taktfrequenz, mit der ein Ablaufplan  $\alpha$  abgearbeitet werden kann, durch

$$fm(PWidth(\alpha, \chi))$$

berechnen. Die Kosten der Registerbänke im Prozessor sind ebenfalls durch den Ablaufplan  $\alpha$  und die Clusterung  $\chi$  festgelegt:

$$RBCost(\alpha, \chi) = \sum_{c \in (V/\chi - \{[e]_\chi\})} RBCCost(\alpha, \chi, c)$$

.

Dabei bezeichnet RBCCost die Kosten der Registerbank im Cluster c unter der Annahme, dass jede Registerbank mindestens so viele Register wie Ports besitzt:

$$RBCCost(\alpha, \chi, c) = RFCCost(PCWidth(\alpha, \chi, c), (PCWidth(\alpha, \chi, c), 0, 0)).$$

Die Anzahl der Operationen des Typs t, die in einer Instruktion i in einem Cluster  $c \in V/\chi$  gleichzeitig ausgeführt werden, ist

$$TICWidth(\alpha(i), c, t) = \left| \left\{ w \mid w \in (\alpha(i) \cap c) \land type(w) = t \right\} \right|.$$

Es müssen also mindestens

$$TCWidth(\alpha, c, t) = \max \{TICWidth(\alpha(i), c, t) | 0 \le i < |\alpha| \}$$

viele funktionale Einheiten den Operationstypen t im Cluster c implementieren. Aus diesen Werten für jeden Cluster und jeden Operationstypen ergibt sich eine untere Schranke für die Datenpfadkosten des Prozessors, der benötigt wird, um  $\alpha$  abzuarbeiten:

$$\sum_{t \in \mathcal{O}} \sum_{c \in V/\chi} op Cost(t) \cdot TCWidth(\alpha, c, t). \tag{1.13}$$

Ein Tripel  $(\alpha, \chi, \phi)$  bestehend aus einem Ablaufplan, einer Clusterung und einer Bindung wird **Zielprogramm** genannt. Ein solches Tripel stellt bis auf die Registerallokation das vom Prozessor auszuführende Programm dar. Aus ihm lassen sich die Mindestanforderungen an die Parameter eines VLIW-Prozessors, der dieses Zielprogramm abarbeiten kann, herleiten. Einem Zielprogramm  $(\alpha, \chi, \phi)$  wird ein VLIW-Prozessor  $(\mathcal{C}, \mathcal{F}, cf, ft, rz, rpc)$  zugeordnet mit:

- $\mathcal{C} := V / \chi$ ,

- $\mathcal{F} := V/\phi$ ,

- $\forall c \in \mathcal{C} : cf(c) := c/(\phi \cap (c \times c)),$

- $\forall f \in \mathcal{F} : ft(f) := \{type(v) | v \in f\},$

- $\forall c \in \mathcal{C}$ :

$$rpc(c) = \begin{cases} (0,0,0), & \text{falls } c = [e]_{\chi} \\ (PCWidth(\alpha,\chi,c), erPWidth(\alpha,\chi), ewPWidth(\alpha,\chi)), & \text{sonst.} \end{cases}$$

Die Anzahl rz(c) der mindestens benötigten Register in der Registerbank eines Clusters c wird während der DSE nicht minimiert. Sie kann aus der maximalen Anzahl gleichzeitig lebendiger Werte in einer Instruktion im Cluster c berechnet werden. Im Ablaufplan  $\alpha$  und Cluster c ist die Anzahl der in Instruktion i gleichzeitig lebendigen Werte

$$|\{v \mid \exists (v, w) \in D \ \exists j, k \in \mathbb{N} : j \le i < k \land v \in \alpha(j) \land v \notin \alpha(i+1) \land w \in \alpha(k) \land (v \in c \lor w \in c)\}|.$$

Weiterhin müssen noch Register zum Speichern globaler Werte vorhanden sein. Diese globalen Werte werden in dem Basisblockmodell nicht dargestellt und es wird vorausgesetzt, dass genügend Register vorhanden sind, um diese Werte zu speichern. Sollten dafür nicht genügend Register vorhanden sein, dann wäre Programmcode zum Ein- und Auslagern von Registerwerten erforderlich. Dieser zusätzliche Programmcode erhöht im Allgemeinen die Ausführungszeit des Programms, weswegen es nicht sinnvoll ist, ihn in die Ablaufpläne von zeitkritischen Basisblöcken einzufügen. Die Konsequenz ist, dass die Registerbänke des Prozessors genügend Register zur Verfügung stellen müssen, um Auslagerungscode zu vermeiden und das Speichern globaler Werte in Registern während der Abarbeitung der zeitkritischen Basisblöcke zu ermöglichen.

Mit diesem Programmmodell können die Parameter eines VLIW-Prozessors vollständig durch ein für ihn erzeugtes Zielprogramm beschrieben werden. Das grundsätzliche Vorgehen bei der DSE mit DESCOMP wird im folgenden Abschnitt beschrieben.

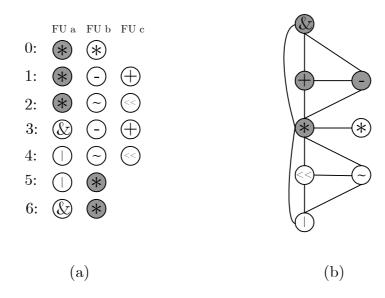

# 2.3 Prinzip der DSE mit DESCOMP

Mit DESCOMP können vollständig automatisiert die folgenden Parameter eines geclusterten VLIW-Prozessors bestimmt werden:

- Die Anzahl der Cluster,

- für jeden Cluster eine geeignete FU-Anzahl und

- für jede FU die bereitzustellenden Operatoren.

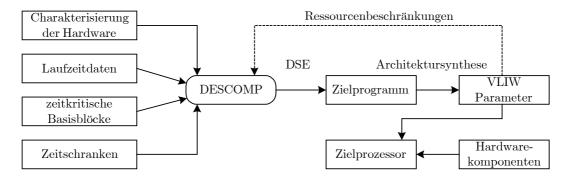

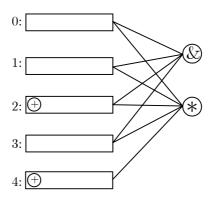

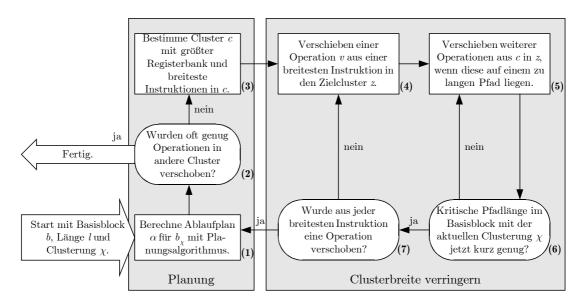

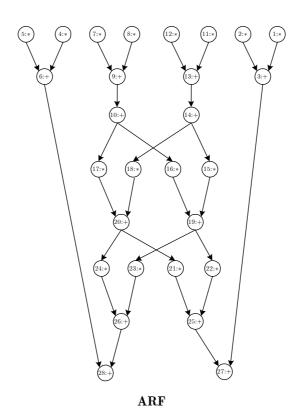

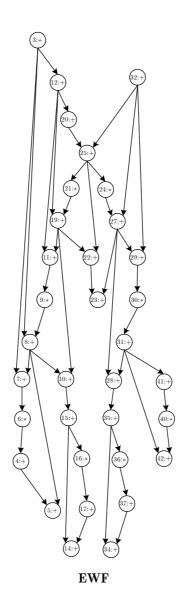

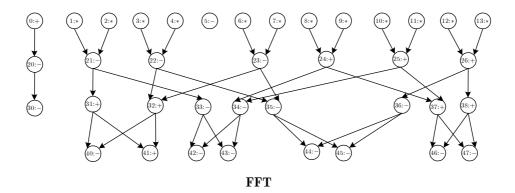

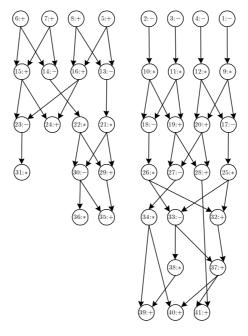

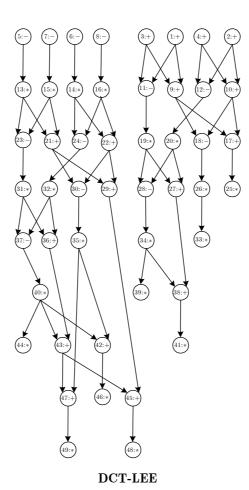

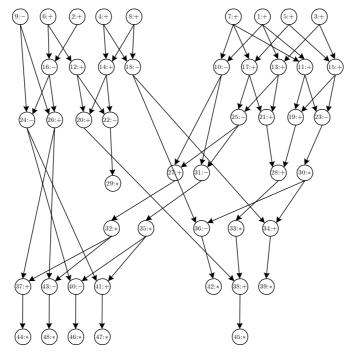

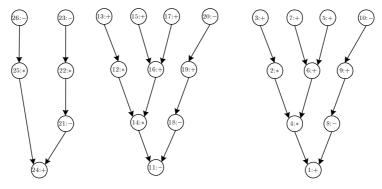

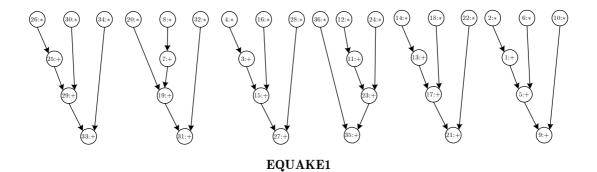

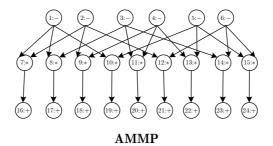

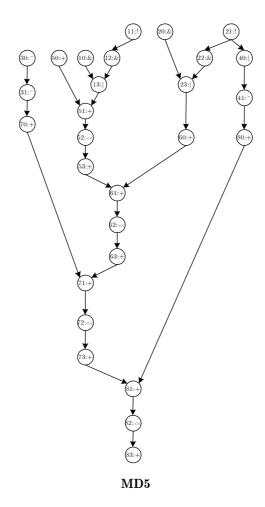

Das schließt die Kopieroperatoren mit ein, da diese zum externen Cluster gehören. Der prinzipielle Ablauf der DSE mit den erforderlichen Eingaben, um diese Parameter zu bestimmen, ist in Abbildung 2.10 dargestellt.

Abbildung 2.10: Prinzip der Architekturoptimierung mit DESCOMP.