# Material Science for high performance SiGe HBTs: Solid-Phase Epitaxy and III-V/SiGe hybrid approaches

Von der Fakultät für Mathematik, Naturwissenschaften und Informatik der Brandenburgischen Technischen Universität Cottbus

zur Erlangung des akademischen Grades

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigte Dissertation

vorgelegt von

Diplom-Chemiker Oliver Skibitzki

geboren am 23. Februar 1982 in Oldenburg (Oldb.)

Gutachter: Prof. Dr. Thomas Schröder

Gutachter: Prof. Dr. Bernd Tillack

Gutachter: Prof. Dr. William Ted Masselink

Tag der mündlichen Prüfung: 21. November 2013

## **Acknowledgements**

At this point I would like to thank all people who contributed over the past four years to the preparation and success of this dissertation. First and foremost I want to express my gratitude to Prof. Dr. Hans-Joachim Müssig and Prof. Dr. Thomas Schroeder for offering me the possibility to work in the Materials Research Department at IHP and to accomplish my Ph.D. in the field of semiconductor science. I would like to thank especially my supervisor Prof. Dr. Thomas Schroeder for his scientific expertise, steady encouragement and fair guidance during the entire time; without whose support this dissertation would have never reached this level. Special gratitude goes also to Prof. Dr. Bernd Tillack and Dr. Yuji Yamamoto for giving me the opportunity to learn about SiGe epitaxy, to gain cleanroom experience and to carry out experiments as a member of the epitaxy team in the Technology Department at IHP. Furthermore, I want to acknowledge the support and engagement of our partners Prof. Dr. William Ted Masselink and Dr. Fariba Hatami at the Humboldt University Berlin in terms of III/V-deposition, semiconductor physics and exchange of scientific expertise.

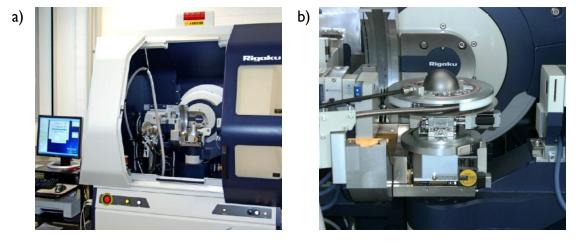

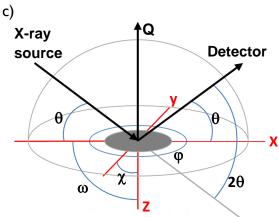

In addition, I would like to thank Dr. Peter Zaumseil at IHP for aid and discussion regarding the x-ray diffraction technique, Dr. Markus Andreas Schubert at IHP and Dr. Achim Trampert at Paul-Drude-Institute for solid-state electronics in Berlin for their work and expertise in the transmission electron microscopy technique, and Dr. Bernd Heinemann for introducing me into HBT process development and integration at IHP.

Further thanks go to my collaborators at IHP Dr. Thomas Bertaud, Dr. Pauline Calka, Dr. Ioan Costina, Dr. Jaroslaw Dabrowski, Dr. Alessandro Giussani, Dr. Canan Baristiran Kaynak, Dr. David Kot, Dr. Grzegorz Kozlowski, Dr. Gunther Lippert, Dr. Mindaugas Lukosius, Dr. Grzegorz Lupina, Dr. Lidia Lupina, Dr. Gang Niu, Dr. Olaf Seifarth, Dr. Christian Walczyk, Dr. Christian Wenger, Tomasz Grzela, Yvonne Heier, Udo Kaletta, Max Klingsporn, Klaus Köpke, Rainer Krups, Jana Matejova, Gabriele Morgenstern, Malgorzata Sowinska, Hans-Jürgen Thieme, Damian Walczyk and Marvin Zoellner who were always open to assist me with personal and scientific problems and created in this way a friendly and pleasant atmosphere over the past four years.

Last but not least, I would like to express my deepest gratitude towards my parents and my wife Pia for everything they have given to me over my entire life. Their strong faith, their never-ending support and their unconditional love have always accompanied me and gave me the personal strength to accomplish this chapter of my life.

# **D**edication

I dedicate this dissertation to my beloved son, Lio Maximilian, heralding one new exciting chapter of my life.

#### **Abstract**

After the age of microelectronics was launched in Bell Labs by Bardeen and Brattain on 23<sup>rd</sup> December 1947, the constant miniaturization of silicon (Si) transistors and circuits up to today led to a unique success story. At its peak are now standing small, fast and reliable multifunctional device systems, which accompany and simplify a great part of our everyday life. However, the complexity of today's microelectronic circuitry is not only driven by complementary metal oxide semiconductor (CMOS) scaling, but also by integration of high performance modules for various applications. One example is given by mixed signal circuitries for wireless and broadband communication systems. These mixed signal circuitries are build up by combining digital CMOS technology with analog silicon-germanium-carbon (SiGe:C) hetero-bipolar transistors (HBT) known as SiGe:C BiCMOS technology. State-ofthe-art SiGe:C BiCMOS technologies achieve up to the 500 GHz today. Nevertheless, Si as semiconductor material is approaching more and more its physical limits, whereby novel approaches have to be found to ensure the future development of SiGe:C HBT BiCMOS technology in order to push the maximum frequency further into the Terahertz regime. Based on this task, two novel material science strategies are investigated in this Ph.D. thesis in terms of material growth and defect studies:

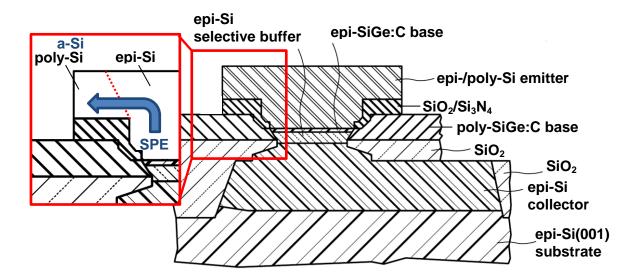

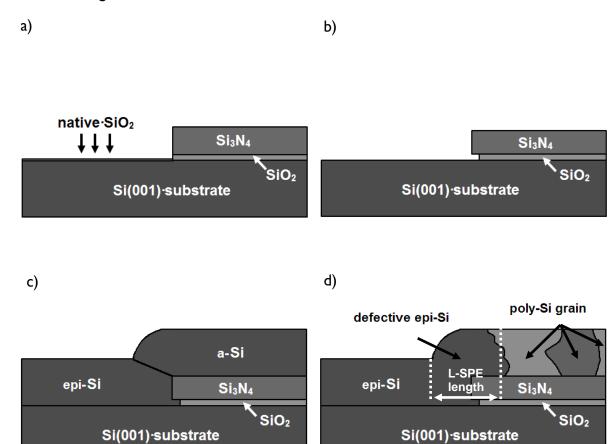

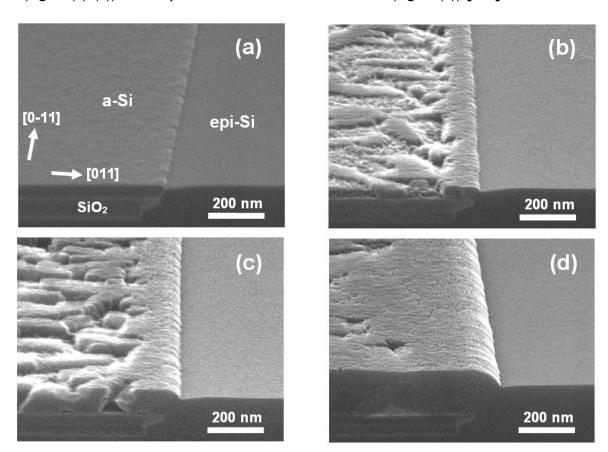

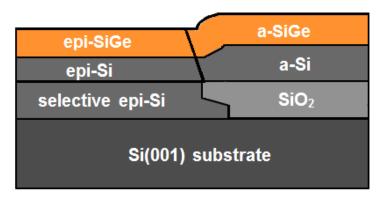

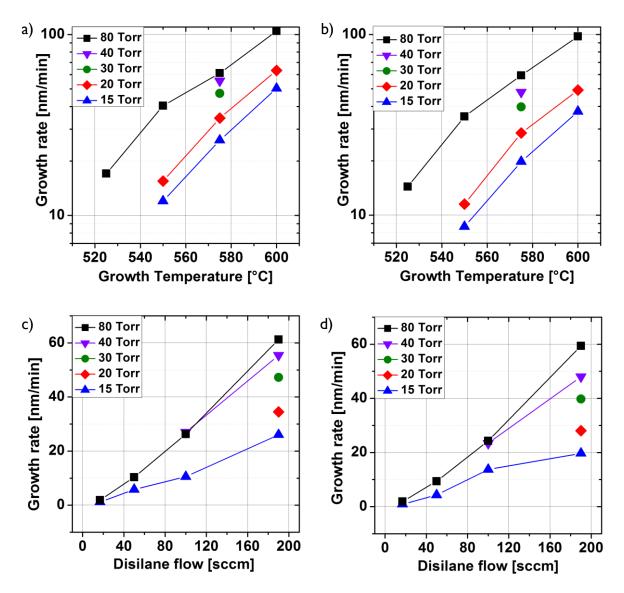

- **A.)** Solid-phase epitaxy (SPE) for emitter and base resistivity: This technique has been investigated for local engineering of crystallinity in emitter and base layer of already established SiGe:C HBT device technology in order to improve the speed performance. By introducing disilane as new gas source with respect to standard used silane, it is possible to reduce the chemical vapor deposition growth temperature for Si, enabling in turn a differential growth of epitaxial-Si (epi-Si) on Si and amorphous Si (a-Si) on the silicon dioxide (SiO<sub>2</sub>) and silicon nitride (Si<sub>3</sub>N<sub>4</sub>) masks. The so produced requirement for SPE treatments is evaluated for two possible areas of application: **A1.**) Emitter region and **A2.**) Base region. In both cases, SPE techniques are applied to change the standard polycrystalline-Si (poly-Si) emitter and base link area on the SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> masks to a fully epi-Si area in order to lower emitter and base resistivity, respectively.

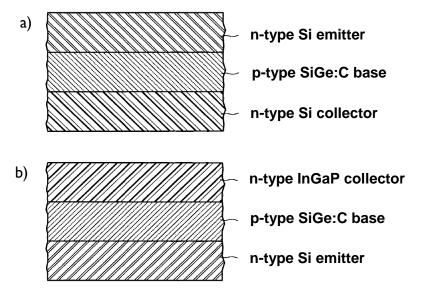

- **B.)** *III-V/SiGe hybrid device:* The ternary compound semiconductor Indium gallium phosphide ( $In_{1-x}Ga_xP$  [x = 0 I]) is introduced as potential new collector material as part of an advanced III-V/SiGe hybrid HBT device. With InP having a three times higher saturation velocity than Si, and GaP having a two times bigger bandgap than Si, this approach offers the possibility to adjust speed and power performance of HBTs in a flexible way as a function of the  $In_{1-x}Ga_xP$  collector chemical composition x.

The material growth and defect studies in this Ph.D. thesis produced insights, which lead to the following results for future device application:

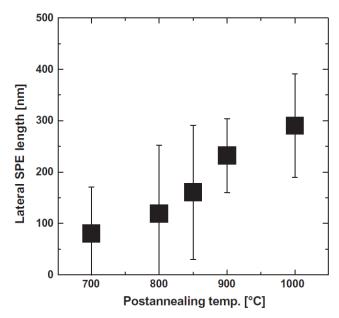

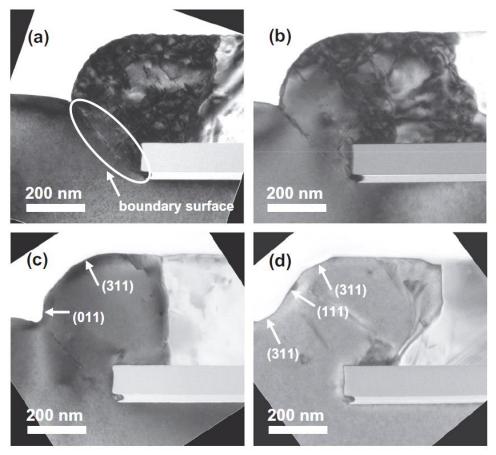

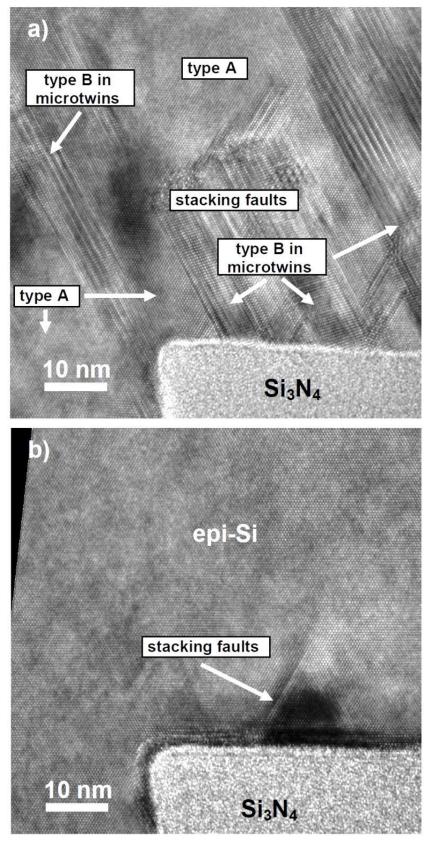

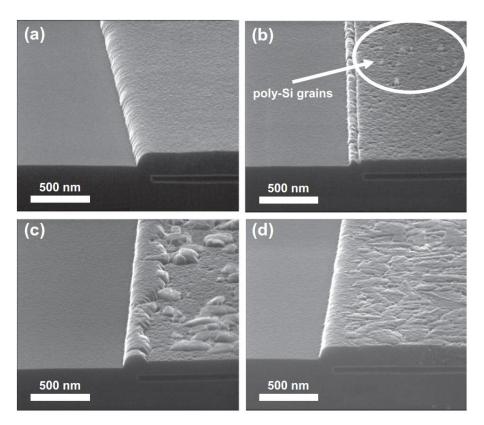

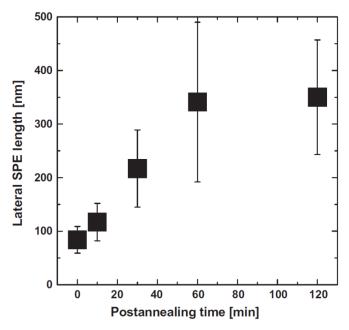

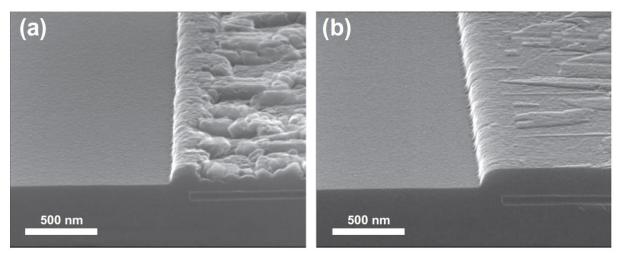

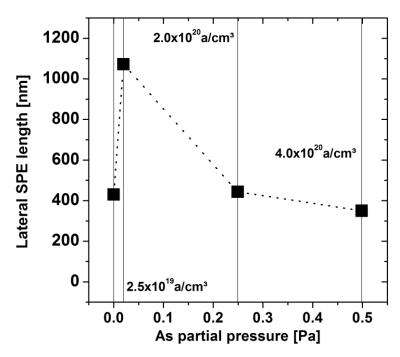

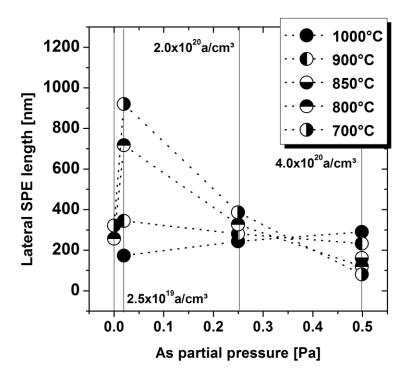

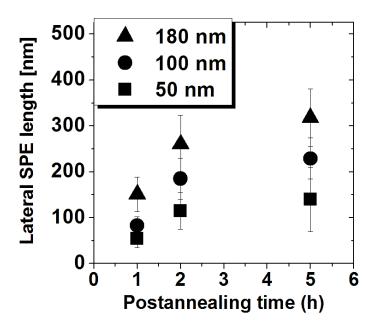

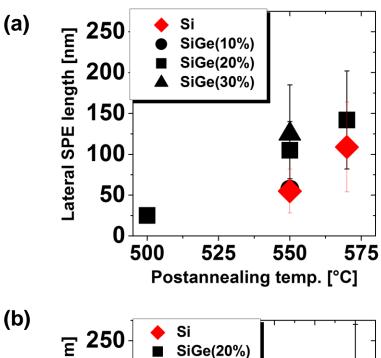

- A1.) SPE for emitter region: After investigating the temperature, time and doping concentration dependence on lateral SPE length of in-situ annealed As-doped epi-Si/a-Si test structures, it was possible to crystallize up to 500 nm of a-Si on SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> masks to epi-Si with low defect densities by a combination of 575 °C and 1000 °C postannealing.

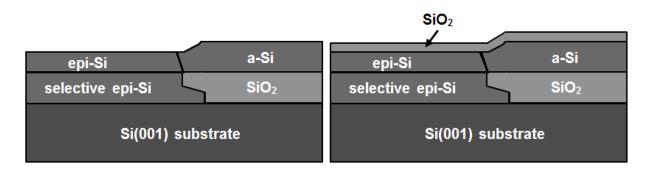

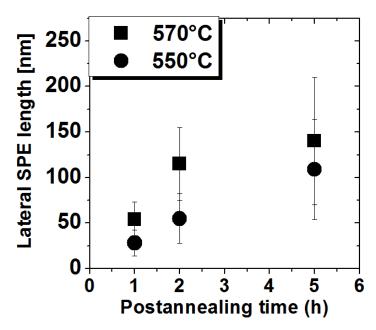

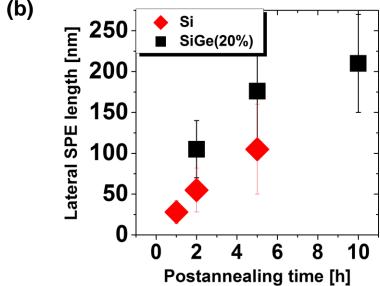

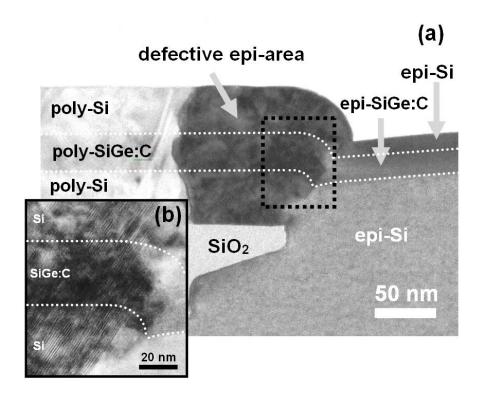

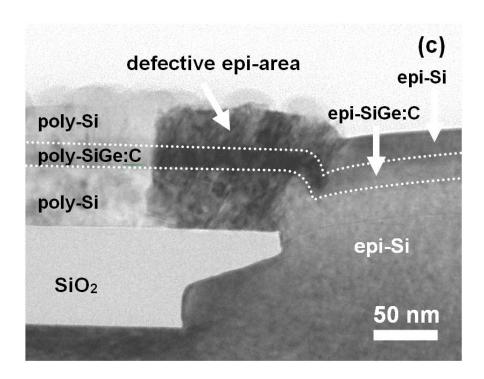

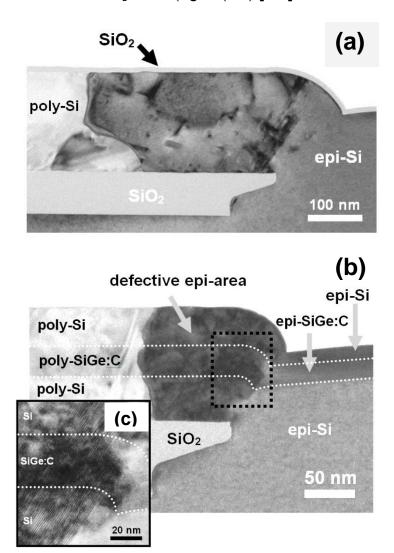

- **A2.) SPE** *for base region:* After studying the dependence of time, temperature, thickness, SiO<sub>2</sub>-capping and Ge incorporation on lateral SPE length of in-situ annealed undoped epi-Si/a-Si test structures, it was possible to crystallize up to 450 nm of SiO<sub>2</sub>-capped undoped a-Si on SiO<sub>2</sub> mask to low-defective epi-Si by 570 °C postannealing. Finally, this technique is applied in a SiGe:C base model structure in order to show the possibility to widen the monocrystalline region around the bipolar window, which results in a possibly improved base resistivity.

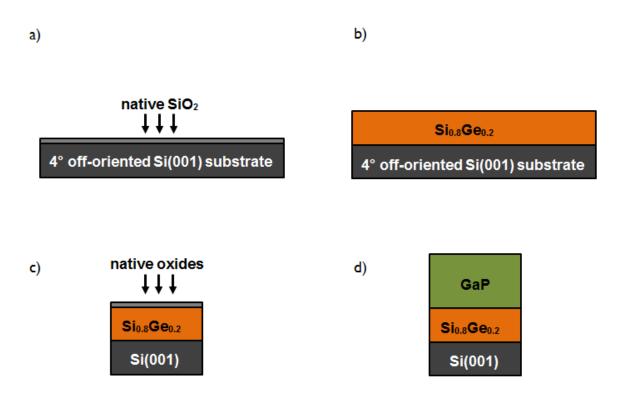

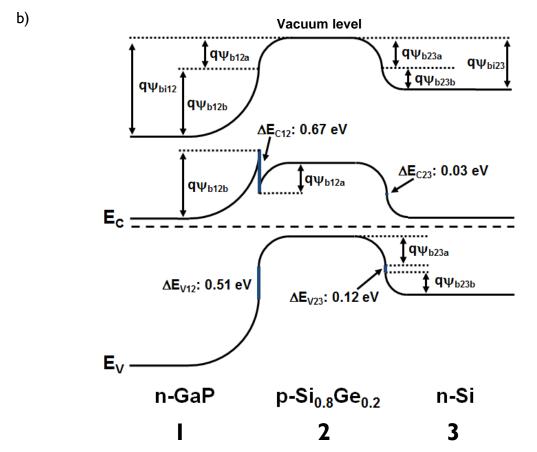

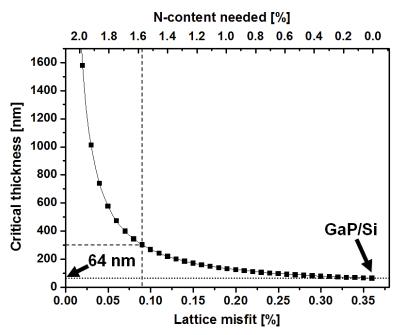

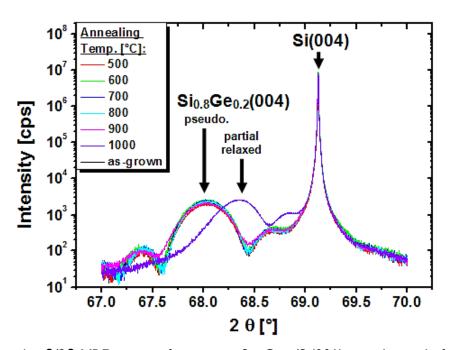

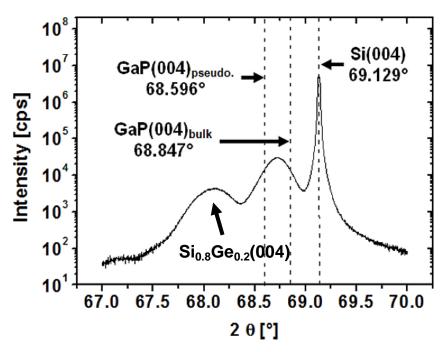

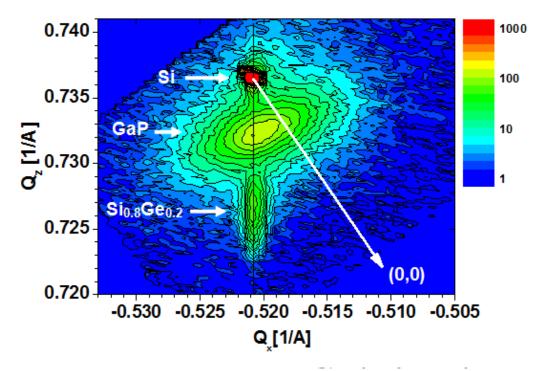

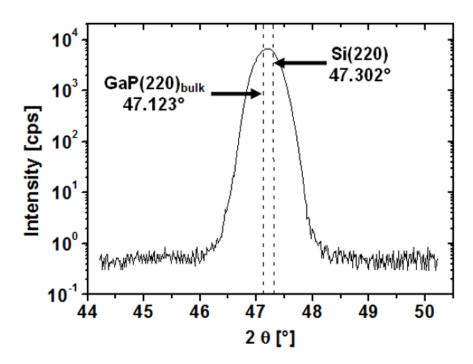

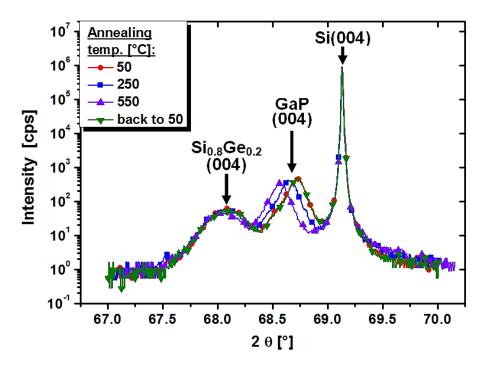

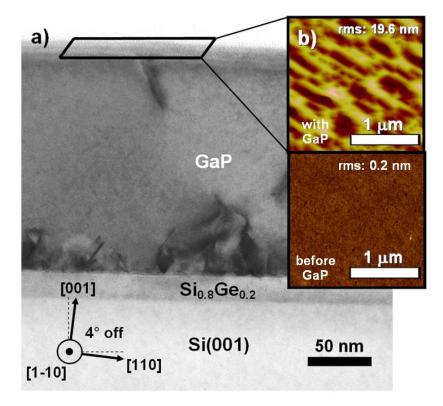

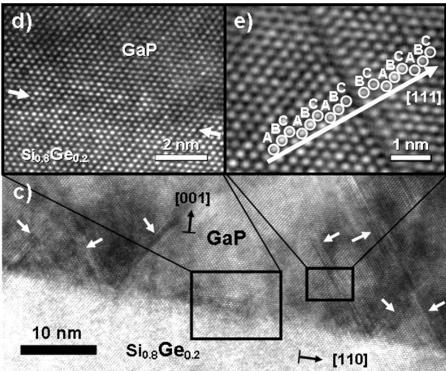

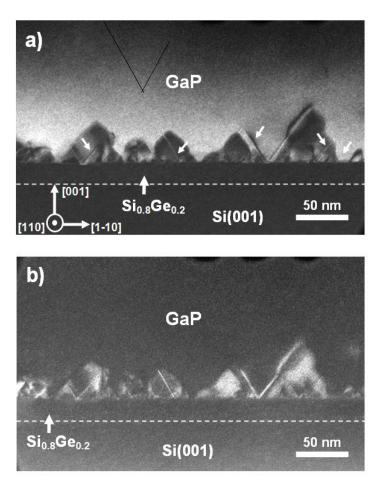

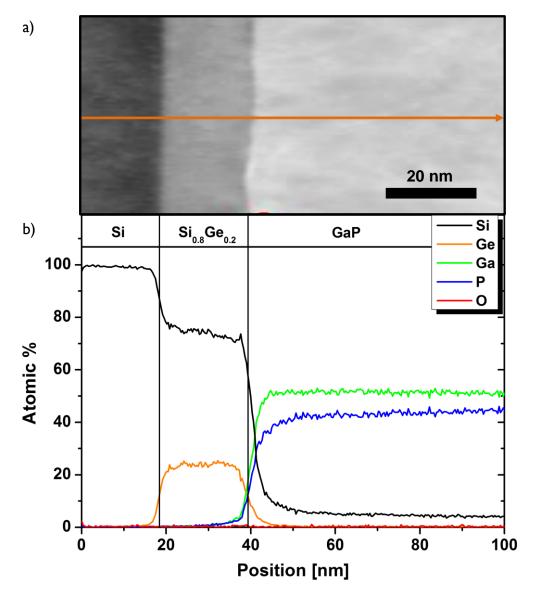

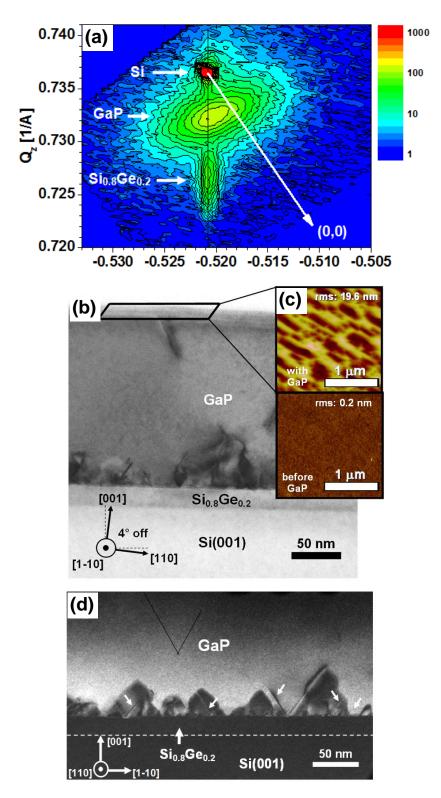

- **B.)** *GaP/Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) heterostructure:* For pseudomorphic GaP/Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) heterostructure growth, the critical thickness of GaP on Si and maximum thermal budget for GaP deposition is evaluated. A detailed structure and defect characterization study by x-ray diffraction (XRD), atomic force microscopy (AFM), and transmission electron microscopy (TEM) is reported on single crystalline 170 nm GaP/20 nm Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) heterostructure. Results show that 20 nm Si<sub>0.8</sub>Ge<sub>0.2</sub> on Si(001) can be overgrown by 170 nm GaP without affecting the pseudomorphism of the Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) systems. The GaP layer grows however partially relaxed, mainly due to defect nucleation at the GaP/Si<sub>0.8</sub>Ge<sub>0.2</sub> interface during initial island coalescence. The achievement of 2D GaP growth conditions on Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) systems is thus a crucial step for achieving fully pseudomorphic heterostructures. Anti-phase domain-free GaP growth is observed for film thicknesses beyond 70 nm. In addition, no detrimental impurity diffusion could be found in the GaP/Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) heterostructure.

Finally, it is to mention that further investigation and efforts are still needed to push these new approaches to full integration into SiGe:C HBT BiCMOS technology concepts:

- **A.)** For SPE application: Electrical studies are needed in frame of full processed devices to evaluate the value and required modifications for process integration.

- **B.)** For III-V/SiGe hybrid device: Future work has to focus on improved 2D GaP layer conditions (before introducing InP) in order to prepare truly pseudomorphic  $GaP/Si_{0.8}Ge_{0.2}/Si(001)$  heterostructures with low defect densities. For this purpose, selective GaP growth studies in local HBT  $Si_{0.8}Ge_{0.2}/Si(001)$  mesa structures are the next step.

## Zusammenfassung

Nach Beginn der Mikroelektronik-Ära in den Bell Labs durch Bardeen und Brattain am 23. Dezember 1947 sorgte die Miniaturisierung von Si-Transistoren und Schaltungen bis heute für eine einzigartige Erfolgsgeschichte. Obenauf stehen nun kleine, schnelle und zuverlässige Multifunktionsbauteile, welche uns alltäglich begleiten und helfen. Allerdings macht die CMOS-Skalierung nicht ausschließlich die Komplexität heutiger mikroelektronischer Schaltungen aus, sondern wird ergänzt durch Integration von Hochleistungsmodule für verschiedene Anwendungen. Als Beispiel kann man die Mischsignalschaltungen für drahtlose und Breitband-Kommunikationssysteme benennen, welche durch die Kombination von digitaler CMOS- mit analoger SiGe:C HBT-Technologie (auch bekannt als SiGe:C BiCMOS –Technologie) aufgebaut werden und heute bis zu 500 GHz erreichen. Da allerdings Si als Halbleitermaterial mehr und mehr an seine physikalischen Grenzen stößt, müssen neue Ansätze gefunden werden, um eine weitere Entwicklung der SiGe:C HBT BiCMOS-Technologie in Richtung Terahertz-Regime zu gewährleisten. Basierend auf dieser Aufgabe werden zwei neuartige Materialstrategien im Rahmen dieser Doktorarbeit in Form von Materialwachstums- und Defektstudien untersucht:

- **A.)** Festphasenepitaxie (SPE): SPE gestattet das lokale Verändern der Kristallinität in Emitter- und Basisschichten von bereits etablierten SiGe:C HBT-Technologien, um deren Geschwindigkeit zu verbessern. Die Einführung des Prozessgases Disilan anstatt des sonst verwendeten Silan ermöglicht die Senkung der CVD-Wachstumstemperatur für Si, wodurch ein differentielles Wachstum von epi-Si auf Si und a-Si auf SiO<sub>2</sub>- und Si<sub>3</sub>N<sub>4</sub>-Masken erfolgt. Diese Voraussetzung zur SPE-Anwendung wird an zwei möglichen Anwendungsbereichen evaluiert: **A1.)** Emitterbereich und **A2.)** Basisbereich. In beiden Fällen wird die SPE angewendet, um die standardmäßigen poly-Si-Bereiche auf den SiO<sub>2</sub>- und Si<sub>3</sub>N<sub>4</sub>-Masken in epi-Si umzuwandeln, was zum Ziel hat, den Emitter- bzw. Basiswiderstand zu senken.

- **B.)** *III-V/SiGe Hybridbauteil:* Der ternäre Verbindungshalbleiter  $In_{1-x}Ga_xP$  [x = 0 1] wird als potentielles neues Kollektormaterial im Rahmen eines III-V/SiGe Hybridansatzes eingeführt. Mit InP, welches eine dreimal höhere Sättigungsgeschwindigkeit als Si, und GaP, welches ein zweimal größere Bandlücke als Si hat, bietet dieser Ansatz die Möglichkeit, Geschwindigkeit und Leistung des HBTs flexibel als Funktion der chemischen Zusammensetzung x des  $In_{1-x}Ga_xP$  anzupassen. Die Materialwachstums- und Defektstudien in dieser Doktorarbeit erbrachten folgende Ergebnisse:

- A1.) SPE für den Emitterbereich: Nach der Untersuchung der Temperatur-, Zeitund Dotierungskonzentrationsabhängigkeit auf die laterale SPE-Länge von in-situ

getemperten, As-dotierten epi-Si/a-Si – Teststrukturen war es möglich, 500 nm a-Si auf den  $SiO_2$ - und  $Si_3N_4$ -Masken zu epi-Si mit geringen Defektdichten zu kristallisieren, indem man eine Temperkombination aus 575 °C und 1000 °C verwendete.

- A2.) SPE für den Basisbereich: Nach dem Studium der Zeit-, Temperatur-, Dicken-, SiO<sub>2</sub>-Bedeckungs- und Ge-Einlagerungsabhängigkeit auf die L-SPE-Länge von in-situ getemperten, nicht dotierten epi-Si/a-Si-Teststrukturen war es möglich, bis zu 450 nm des SiO<sub>2</sub>-bedeckten, undotierten a-Si auf der SiO<sub>2</sub>-Maske zu epi-Si mit geringen Defektdichten zu kristallisieren, indem man eine Temperung bei 570 °C verwendete. Abschließend wurde mittels einer SiGe:C Basis-Modellstruktur gezeigt, dass SPE die Möglichkeit bietet, den monokristallinen Bereich um das Bipolar-Fenster zu erweitern, was in einer möglichen Verbesserung des Basis-Widerstandes resultieren kann.

- **B.)** *GaPlSi<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) Hetero-Struktur:* Fürs pseudomorphe GaP/Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) Hetero-Strukturwachstum wurde die kritische GaP-Schichtdicke auf Si und das maximale thermale Budget für die GaP-Beschichtung ermittelt. Eine einkristalline 170 nm GaP/20 nm Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) Hetero-Struktur wird in Bezug auf Struktur und Defekte charakterisiert durch XRD, AFM und TEM. Die Ergebnisse zeigen, dass 20 nm Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) mit 170 nm GaP überwachsen werden kann, ohne den Pseudomophismus des Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001)-Systems zu beeinflussen. Jedoch kommt es durch Zusammenwachsen der anfänglichen GaP-Inseln zu Defektnukleation an der GaP/Si<sub>0.8</sub>Ge<sub>0.2</sub>-Grenzschicht, wodurch GaP teilweise relaxiert aufwächst. Daher bildet das erfolgreiche 2D GaP-Wachstum auf Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001)-Systemen den entscheidenden Schritt, um eine völlig pseudomorphe Hetero-Struktur zu bilden. Des Weiteren konnte die Abwesenheit von Anti-Phasen-Domänen ab einer GaP-Schichtdicke von 70 nm und keine schädliche Diffusion innerhalb der GaP/Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) Hetero-Struktur beobachtet werden.

Abschließend ist zu erwähnen, dass weiter Untersuchungen und Anstrengungen unternommen werden müssen, um diese neuen Ansätze zur Reife einer Integrationsvariante in der SiGe:C HBT BiCMOS-Technologie zu bringen:

- **A.)** Für SPE-Anwendungen: Elektrische Studien in Rahmen eines voll prozessierten Bauteils werden benötigt, um den Wert für die Prozessintegration zu bewerten.

- **B.)** *III-V/SiGe Hybridbauteil:* Zukünftige Arbeiten müssen sich (bevor man InP hinzufügt) auf die Verbesserung der 2D GaP-Schichtnukleation fokussieren, um eine wirklich pseudomorphe GaP/Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) Hetero-Struktur mit geringen Defektdichten herzustellen. Hierzu sind selektive GaP-Wachstumsstudien in lokalen Si<sub>0.8</sub>Ge<sub>0.2</sub>/Si(001) Mesa-Strukturen der nächste Schritt.

# Index

| Ac  | knowle   | dgements                                                    | 3  |  |  |

|-----|----------|-------------------------------------------------------------|----|--|--|

| De  | dication | າ                                                           | 5  |  |  |

| Αb  | stract   |                                                             | 7  |  |  |

| Zu  | sammer   | nfassung                                                    | 9  |  |  |

| Inc | lex      |                                                             | 11 |  |  |

| ١.  | Introd   | uction                                                      | 13 |  |  |

|     | 1.1.     | "More than Moore" vs. "More Moore" research                 | 13 |  |  |

|     | 1.2.     | Closing the THz gap                                         | 14 |  |  |

|     | 1.3.     | SiGe:C BiCMOS technology                                    | 16 |  |  |

|     |          | I.3.1. CMOS Device Physics                                  | 20 |  |  |

|     |          | I.3.2. HBT Device Physics                                   | 23 |  |  |

|     | 1.4.     | Goals of this thesis                                        | 36 |  |  |

|     |          | I.4.1. Solid-phase epitaxy for emitter and base resistivity | 38 |  |  |

|     |          | I.4.2. III-V/SiGe hybrid device: In I -xGaxP collector      | 39 |  |  |

| 2.  | Experi   | mental part                                                 | 41 |  |  |

|     | 2.1.     | . Thin film growth techniques                               |    |  |  |

|     | 2.2.     | Characterization techniques                                 |    |  |  |

|     | 2.3.     | Sample preparation                                          | 57 |  |  |

|     |          | 2.3.1. SPE growth studies                                   | 57 |  |  |

|     |          | 2.3.2. In <sub>1-x</sub> Ga <sub>x</sub> P growth studies   | 62 |  |  |

| 3.  | Result   | part                                                        | 66 |  |  |

|     | 3.1.     | Solid-phase epitaxy for emitter and base resistivity        | 66 |  |  |

|     |          | 3.1.1. Solid-phase epitaxy                                  | 66 |  |  |

|     |          | 3.1.2. Experimental studies for emitter application         | 69 |  |  |

|     |          | 3.1.3. Experimental studies for base application            | 79 |  |  |

|     | 3.2.                  | III-V/SiG     | Ge hybrid device: In <sub>I-x</sub> Ga <sub>x</sub> P collector            | 90  |  |

|-----|-----------------------|---------------|----------------------------------------------------------------------------|-----|--|

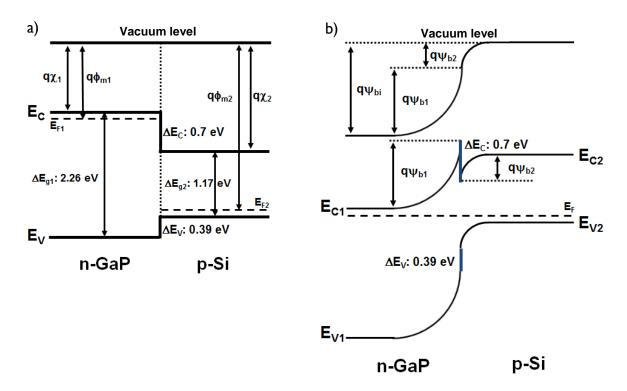

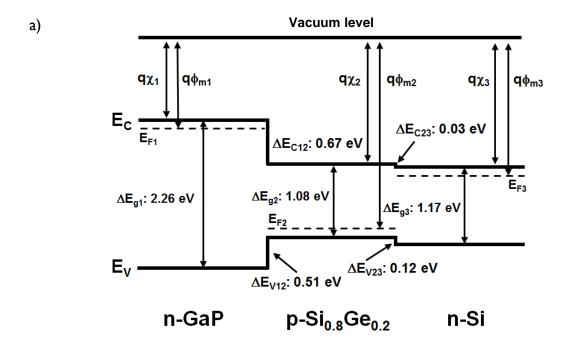

|     |                       | 3.2.1.        | Semiconductor Physics of In <sub>1-x</sub> Ga <sub>x</sub> P HBT collector | 90  |  |

|     |                       | 3.2.2.        | General aspects of III-V heteroepitaxy on silicon                          | 101 |  |

|     |                       | 3.2.3.        | Special aspects of GaP/SiGe/Si(001) heteroepitaxy                          | 109 |  |

|     |                       | 3.2.4.        | Experimental studies                                                       | 113 |  |

| 4.  | Summ                  | ary & Ou      | tlook                                                                      | 131 |  |

| 5.  | Scienti               | ific visibili | ty                                                                         | 137 |  |

| Lis | _ist of abbreviations |               |                                                                            |     |  |

| Bib | liograp               | hy            |                                                                            | 148 |  |

| Ар  | pendix                | •••••         |                                                                            | 158 |  |

#### I. Introduction

#### 1.1. "More than Moore" vs. "More Moore" research

This thesis was prepared at IHP, the Leibniz institute for innovative microelectronics in Frankfurt (Oder), Germany. IHP is an internationally recognized competence center for Silicon-Germanium (SiGe) technologies and performs research and development in the following fields: 1) Silicon (Si)-based systems, 2) Highest-frequency integrated circuits (IC), 3) Technologies for wireless and broadband communication, and 4) Materials for micro- and nanoelectronics.

These research programs are combined in a so called vertical approach; namely the four departments at IHP (Material, Technology, Circuit and System) collaborate and share their expertise within these research topics. The focus of research at the institute is oriented towards solutions relevant for the following applications [1]:

1) Telecommunications, 2) Semiconductor industries, 3) Automotive and aerospace industries, 4) Biotechnology and Telemedicine, and 5) Security and automation technologies.

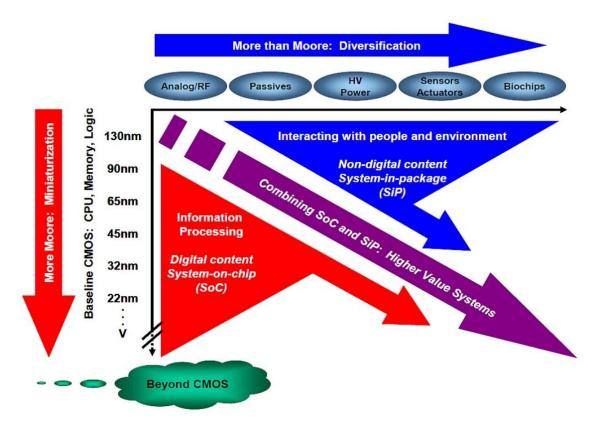

The research pursues consequently a "More than Moore" strategy referring to the ITRS (International Technology Roadmap for Semiconductors) depicted in Fig. I [2]. According to this, IHP does not focus on challenges in miniaturization of Complementary metal oxide semiconductor (CMOS) technologies (known as "More Moore" approach) [3], but on research and development of technology modules for diversification of the existing CMOS technology platform, which considerably extend the functionality to create higher value systems (known as "More than Moore" approach) [4]. Some selected examples for module groups in focus of IHP's "More than Moore"-strategy are listed in the following:

### Radio frequency (RF):

SiGe:C hetero-bipolar transistors (HBT) and Graphene base transistor (GBT) as well as Filters, Antennas, Modulators, Demodulators and RF Micro-electromechanical systems (MEMS) switches [5-11]

#### **Photonics:**

Waveguides, Photodiodes, Modulators, Light-emitting diodes (LEDs) and Lasers [12-15]

#### **Biomedical:**

Glucose sensors and Surface acoustic wave (SAW) filters [16, 17]

**Fig.1** The combined need for digital and non-digital functionalities in an integrated system is translated as a dual trend in the ITRS: miniaturization of the digital functions ("More Moore") and functional diversification ("More than Moore") [2].

## 1.2. Closing the THz gap

To follow the "More than Moore"-strategy, a monolithic integration approach is pursued at IHP: the integration of modules into 0.25 µm and 0.13 µm SiGe:C Bipolar CMOS (BiCMOS) base technologies [1]. This approach allows the combination of high frequency/high performance electronics with the functionality of integrated modules for system-on-chip applications [18]. It is to mention here that different methodologies and techniques exist to achieve full system integration. The two "schools" in microelectronic industry are:

**System-on-chip (SoC):** SoC is a system integration concept that seeks to create numerous system functions (i.e. processors, memory, etc.) by integrating the required active and passive components (i.e. antennas, filter, etc.) onto a single chip. In this way, SoC promises to achieve highest performance and most compact, lightweight systems for industrial mass-production. Nevertheless, challenges like long design times (due to

integration complexities) and high costs (due to integration of active but disparate devices) exist [19].

**System-in-package (SiP):** SiP is a system integration concept using advanced semi-conductor packaging to integrate a number of system functions enclosed in a single package. It consists of two or more vertically stacked dies, which can contain several chips (i.e. processor, memories, etc.) combined with other components (i.e. passives, filters, etc.) and assembled on the same substrate. For interconnection of components and dices, fine wires connected to the package and standard off-chip wire bonds or solder bumps are used. SiP is typically applied in systems where space is limited (like mobile phones) or where a monolithic integration is not possible yet. This technique, based on the stacking of various chips, is very flexible and will thus be intensively pursued in future [19].

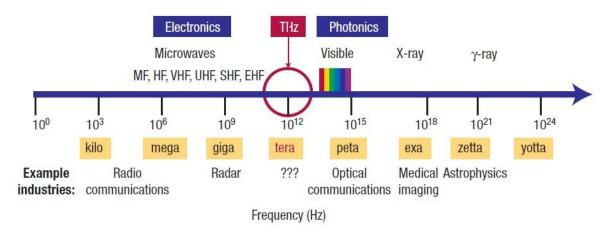

Following the SoC concept, new network architectures, distributed low resource middleware concepts, new energy-efficient protocols for media access as well as energy-efficient transceivers are investigated and realized at IHP with the goal to enable reliable wireless high-speed data transfer and sensor networks in the future [1]. With this motivation, SiGe:C BiCMOS base technology is constantly moving further towards higher frequencies, approaching step by step the Terahertz (THz) range (between 0.5 up to >1 THz) of the electromagnetic spectrum (Fig. 2) [6, 20-22].

Fig.2 Sketch of the electromagnetic spectrum indicating the THz range [20].

It is noted that, in order to reach the THz range in the electromagnetic spectrum (red circle in Fig. 2), two different technology approaches are actively pursued in worldwide research and development:

<u>Electronic technology approach:</u> This approach tries to close the THz gap from the electronic side of the electromagnetic spectrum by frequency enhancement. Current technological examples in this field are: I) HBT oscillators and amplifiers [23-25], 2) THz tunnel diodes [26-28], and 3) Schottky diodes [29-31].

<u>Photonic technology approach:</u> This approach tries to close the THz gap from the photonic side of the electromagnetic spectrum by frequency reduction. Current technological examples in this field are: I) Optically Pumped THz Lasers [22, 32, 33], 2) Quantum Cascade Laser [22, 34, 35], and 3) Photomixing [22, 36, 37].

Along with the daunting microelectronic challenge of our twenty-first century - to fulfill the vision of faster and faster wireless broadband communication with more and more operation range supporting large information exchange between people or devices in a minimum of time on a global scale [18] – additional driving forces fueling THz-research exist. Inspiring applications with high impact on a variety of industries are currently discussed [20-22]: 1) Spectroscopic analysis of pharmaceutical products (e.g. composition studies), 2) Detection of explosives and illegal materials (e.g. scanners for airports), 3) Non-hazardous determination of disease (e.g. cancer), 4) Industrial-process monitoring (e.g. quality checks), and 5) Biomolecule detection (e.g. characteristic molecule fingerprints of proteins).

# 1.3 SiGe:C BiCMOS technology

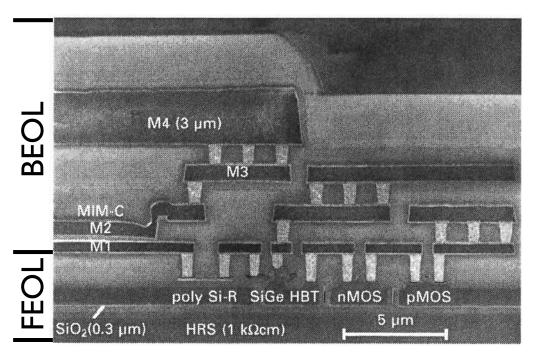

To meet the demand for wireless and broadband communication, both high-speed digital operation and high-frequency analog operation with sophisticated functions must be implemented simultaneously. From this point of view, the SiGe:C BiCMOS technology has developed from its first appearance in 1987 at IBM [18] today to one of the most promising and evolved concepts to fulfill this requirement. Figure 3 shows exemplary a SEM cross-section image of a typical integrated SiGe:C BiCMOS structure [38]:

**Front-end-of-line (FEOL):** FEOL labels in microelectronics the first part of IC fabrication where the individual devices (transistors, capacitors, resistors, etc.) are patterned on the Si wafer. FEOL generally covers everything up to (but not including) the deposition of the first metal interconnect layer (MI) [39]. In Figure 3 (from left to right), the polycrystalline (poly-) Si resistor (Si-R), the SiGe:C HBT and the CMOS (including n-channel Metal—oxide—semiconductor (nMOS) and p-channel Metal—oxide—Semiconductor (pMOS)) parts are shown on a 200 mm Silicon-on-Insulator (SOI) wafer, representing

**Fig.3** Cross-sectional SEM image of 0.2 μm self-aligned SiGe HBT, CMOS transistor and polycrystalline (poly-) Si resistor on 200 mm Silicon-on-Insulator (SOI)(I μm-thick Si on 0.3 μm-thick insulator) wafers on high-resistivity substrate (HRS). Four-level metal (MI-M4) layer structure is used for interconnection [38].

a typical example of a possible FEOL architecture in BiCMOS technology. Device concepts are typically realized in FEOL whenever high quality crystalline material is needed to realize high performance devices (i.p. transistors). Drawback is that expensive Si chip area is consumed.

**Back-end-of-line (BEOL):** BEOL is the second part of IC fabrication where the individual devices of FEOL get interconnected with wiring on the Si wafer. BEOL generally begins when the first layer of metal (MI) is deposited on the wafer. It includes contacts, insulating layers (dielectrics), metal levels, and bonding sites for chip-to-package connections [39]. In Figure 3, four-level metal (MI-M4) layer structures including a Metal-Insulator-Metal capacitor (MIM-C) representing as an example a possible BEOL setup in BiCMOS technology. Furthermore, BEOL integration of full functional modules (e.g. embedded memories, biosensors...) is of increasing interest to push the application of Si microelectronics to new fields. The benefit of BEOL integration is given by the fact that 3D integration does not consume expensive Si chip area. However, only amorphous or polycrystalline material can thus be realized and only a limited thermal budget can be applied.

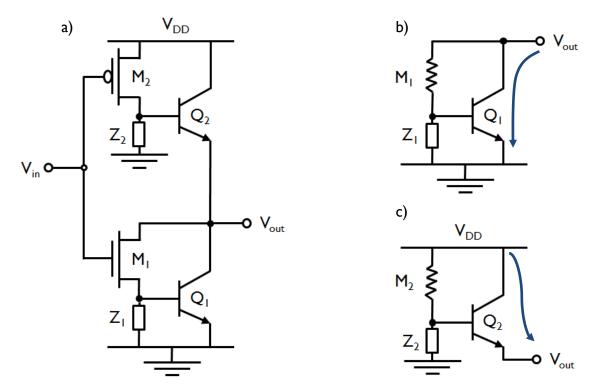

**Fig.4** Sketch of a generic BiCMOS inverter (a) and equivalent circuit with high input signal  $V_{in}$  (b) and with a low input signal  $V_{in}$  (c) [41, 42].

Basically, the SiGe:C BiCMOS technology combines CMOS and SiGe:C HBT technology in a single IC on the same chip [40]. A generic BiCMOS inverter, which forms the basic circuit for the development of a generalized BiCMOS logic family, is shown in Figure 4(a). The circuit in Figure 4(a) consist of a nMOS and pMOS transistor (MI and M2), two n-p-n-SiGe:C HBTs (QI and Q2) and two impedances operating as loads (ZI and Z2). A first observation reveals that both the digital input and the logic operation are realized in CMOS technology. However, SiGe:C HBTs are used for the analog output signal. The functioning of the circuit is as follows:

- When input  $V_{in}$  is high (logic I, i.e. +5 V (supply voltage  $V_{DD}$ )),  $M_2$  is off so that  $Q_2$  will be non-conducting (Fig. 4(b)). But  $M_1$  turns on and supplies current to the base of  $Q_1$  which conducts and acts as a current sink to the load between  $V_{out}$  and ground (GND) which discharges through it to 0 volts. The  $V_{out}$  falls to 0 volts (GND) plus the saturation voltage  $V_{CE,sat}$  between collector and emitter of  $Q_1$ . In conclusion, a high  $V_{in}$  has been translated to a low  $V_{out}$  [41, 42].

- In the opposite way, with input  $V_{in}$  is low (logic 0, i.e. 0 V (GND)),  $M_1$  is off which keeps  $Q_1$  non-conducting (Fig. 4(c)). However,  $M_2$  is on and supplies base current to  $Q_2$  which conducts and acts as a current source to charge the load between  $V_{out}$  and

GND towards +5 V ( $V_{DD}$ ). The output  $V_{out}$  goes to +5 V less the base to emitter voltage ( $V_{BE}$ ) drop of  $Q_2$ . In conclusion, a low  $V_{in}$  has been translated to a high  $V_{out}$  [41, 42].

In steady-state operation,  $Q_1$  and  $Q_2$  never turn on or off simultaneously, so that lower power consumption is guaranteed. This also results in a push-pull bipolar output stage. The transistors  $M_1$  and  $M_2$ , on the other hand, work furthermore as a phase-splitter, which creates higher input impedance. The impedances  $Z_1$  and  $Z_2$  are used to bias the base-emitter junction of the bipolar transistor and to ensure that base charge is removed when the transistors turn off. For practical designs, the use of resistive elements, shown in Figures 4, are very disadvantageous due to their size. Because of this, slightly modified BiCMOS circuits are normally used where the passive impedances ( $Z_1$  and  $Z_2$ ) are replaced by active impedances (e.g. nMOS transistors) or by a resistor in combination with only one impedance [41, 42].

Due to the intersection of CMOS and SiGe:C HBT technology, the emerged SiGe:C BiCMOS technology gains benefits from both transistor technologies [38, 40, 41]:

<u>Advantages contributed by CMOS:</u> 1) Low-power consumption, 2) Low-power dissipation, 3) Low noise margins, 4) High packing density, and 5) Integration of large complex functions with high yields.

Advantages contributed by SiGe:C HBT: 1) High switching speed at large values of capacitive loads, 2) High current drive per unit area, 3) Good noise performance, 4) High analog output capability, and 5) High input/output speed.

Despite of all these remarkable benefits in SiGe:C BiCMOS technology, there are still disadvantages arising especially from [40, 41]: 1) Speed degradation in the low voltage region, and 2) High production costs due to added process complexity.

Nevertheless, it is difficult (or almost impossible) to meet all above listed performance criteria and to satisfy all market requirements in the same time by one SiGe:C BiCMOS technology. Despite the constantly accompanied trade-off between high-performance versus cost-performance [18], there is not only one BiCMOS process which can address all applications. Each application requires different CMOS/SiGe:C HBT integration concepts to achieve an effective functionality, as described by *N. Stogdale and P. Hunt* in detail [41, 43]:

- Good current drive capability: for application to bipolar buffered BiCMOS gates and output stages:

- o Good current drive capability low collector series resistance, buried layers.

- Good performance in analog applications:

- High precision analog components, resistors, capacitors, etc.

- Well controlled device characteristics: Gain, Early voltage, Noise, etc.

- o Tight control of parameters with temperature and operating current.

- Operating Voltage < 5V.</li>

- o High dynamic range.

- <u>High-speed performance: For applications in Emitter-coupled logic (ECL) bipolar transistors</u>

<u>are specifically optimized for low power high speed performance:</u>

- Very low gate delays and low power delay product.

- Minimized parasitic resistances and capacitances.

- o Highly advanced processing techniques for minimization of feature sizes.

- Highly optimized emitter base structure with low transit time.

- Good performance in power switching, smart power applications etc.:

- Low series resistances; low sensitivity buried layers.

- High junction breakdown voltage characteristics.

- Good performance at high currents.

In conclusion, the BiCMOS technology is fundamentally linked to the two device concepts of CMOS and SiGe:C HBT. To gain a full understanding of BiCMOS technology, it is therefore necessary to know the individual transistor physics concepts and their unique characteristics. For this reason, these topics are briefly discussed in the following subsections.

# **I.3.1 CMOS Device Physics**

Looking at history, the basic idea to use a field-effect transistor (FET) as a solid-state amplifier, dates back to Julius Edgar Lilienfeld in 1925 and to Oskar Heil in 1934, who first patented separately from each other the similar FET device. Considering today's overwhelming dominance of CMOS technology in the electronics industry, it occurs somehow ironically, that the practical demonstration of the Bipolar-junction transistor (BJT)

in 1951 preceded that of the metal-oxide-semiconductor field-effect transistor (MOSFET) in 1960 by nine years. The reason for this slow development of a functional FET was due to the large problems in obtaining decent dielectric materials in the Si system. Despite Si has a huge natural advantage in comparison to other semiconductors in this respect, namely to form a very stable oxide, clean-room techniques had to mature to deal with ionic contamination, deionized water, fixed oxide charge and surface state passivation. When in the 1950's high-quality SiO<sub>2</sub> could be produced on an industrial level and raised as a robust gate dielectric, the MOSFET was presented soon in 1960. Finally, the connection between pMOS and nMOS created in 1963 the famous CMOS, which paved the way to the high-volume, low-power, low-cost, highly integrated microprocessor and the enormous variety of computational engines that exist today [18, 44, 45].

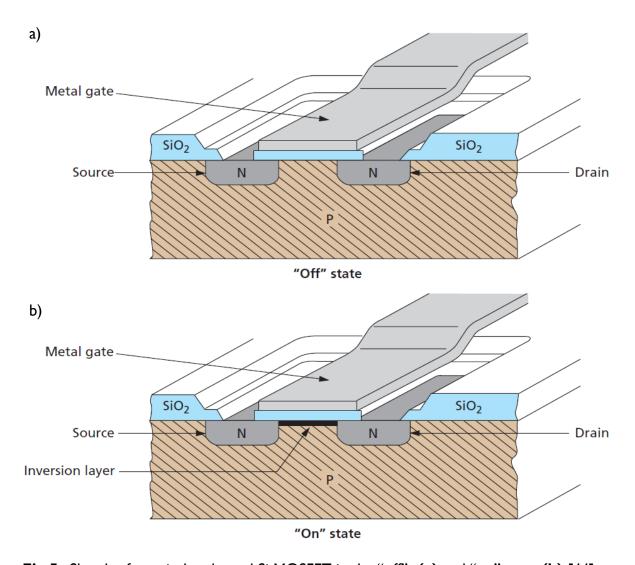

Fig.5 Sketch of a typical n-channel Si MOSFET in the "off"- (a) and "on"-state (b) [44].

CMOS technology consists of both nMOS and pMOS devices, which belong as MOSFETs to the group of FETs. The FET is a unipolar transistor device, which applies an electric field to control the shape and therefore also the conductivity of a channel of only one type of charge carrier (electrons (n) or holes (p)) in a semiconductor material. Figure 5 shows for instance a typical Si nMOS in the "off"- (a) and "on"-state (b). The base structure of the Si MOSFET consist of two isolated pn-junctions in a Si surface, overlaid first with a thin SiO<sub>2</sub> insulator and then with a conducting metal layer (gate). Most of the FETs are fourterminal electronic devices (one exception is e.g. the Junction-FET (JFET)). The three terminals, called source, drain and gate correspond figuratively to the emitter, collector and base of BJT. The fourth terminal, called the body (or also base, bulk or substrate), is used to bias the transistor into operation. For better  $I_{ON}/I_{OFF}$  ratio, FETs are used in CMOS not in accumulation, but in the inversion regime (Fig. 5(b)). This means that, due to field effect by applying the right voltage polarity, an n-conducting inversion channel conducts the current between source and drain in a p-doped Si(001) substrate. To initiate the field effect, the gate is insulated from the active channel, what causes that no current flows over this terminal. The so created gate potential (or electric field) controls the conductivity of the charge carriers in the active channel and finally the drain current I<sub>D</sub> [44-46]. Therefore, I<sub>D</sub> indicates how fast the load of the circuit can be charged or discharged stating the conclusion that high speed performance in MOSFET technology relies on high ID. This figure of merit is given by equation [45]:

$$I_{D} = \frac{W_{Z}}{L} \mu_{n} C_{ox} \left( V_{G} - V_{T} - \frac{F_{Nd} V_{D}}{2} \right) V_{D}$$

(I)

where  $W_Z$  is the channel width, L is the channel length,  $\mu_n$  is the charge carrier mobility,  $C_{ox}$  is the insulator capacitance in inversion,  $V_G$  is the gate voltage,  $V_T$  is the threshold voltage,  $V_D$  is the drain voltage and  $F_{Nd}$  is a function of doping concentration and oxide thickness. Regarding these parameters in equation (I), different approaches can be considered to improve  $I_D$ :

### Higher voltage levels (V<sub>G</sub> and V<sub>D</sub>):

The industrial need for low power devices for mobile technology [18, 47] and the increased electrical breakdown of highly scaled electronics [45, 46] make this approach less attractive for further MOSFET development.

## Raise channel width W<sub>z</sub>:

The major industrial disadvantage in this approach is the accompanying higher cost of valuable chip area by increasing the channel width [18]. One promising way to counteract this problem are three-dimensional gate transistor approaches instead of traditional planar MOSFET technologies [45, 48].

#### • Increase majority charge carrier mobility μ<sub>n</sub>:

To achieve higher majority charge carrier mobilities, worldwide research and development is focusing now on promising approaches like strained Si- [49], SiGe channel-[50] and III/V channel-technology [51].

#### Transistor scaling to reduce channel length L:

This miniaturization approach has been for a long time the primary mean in Si microelectronic industry (More Moore) [3, 18]. Nevertheless, it has to be kept in mind that scaling reduces transistor area A and therefore the gate oxide capacitance  $C_{ox}$  simultaneously [52]:

$$C_{ox} = \varepsilon_r \varepsilon_0 \frac{A}{d} \tag{2}$$

where  $\varepsilon_r$  is the relative permittivity of the material and  $\varepsilon_0$  is the vacuum permittivity. The long-established counteraction for this unfavourable fact was the constant reduction of insulator thickness d. Now, the scaling reaches their limits in form of high leakage currents [53]. Over the years, the introduction of high-k dielectric material as gate oxide has been found as an adequate method to control this issue [52, 54].

## 1.3.2 SiGe:C HBT Device Physics

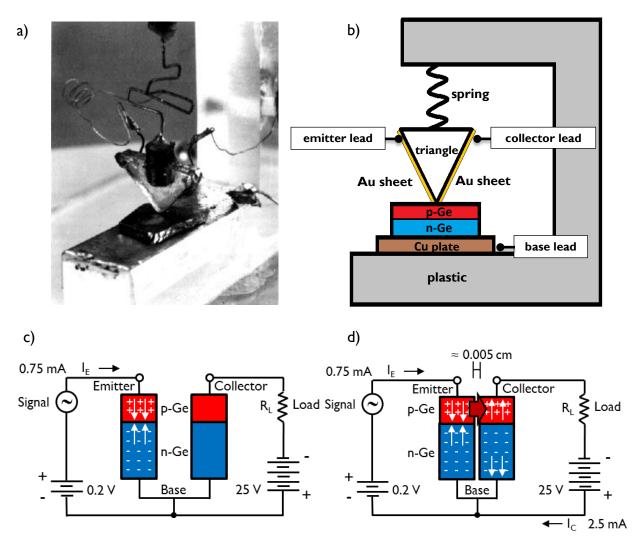

**Point-contact transistor:** Looking at history, it is to mention that the first worldwide built transistor was the bipolar Point-contact transistor realized by Bardeen and Brattain in 1947. This earliest transistor was the precursor of the subsequently-developed BJT in 1951 and SiGe HBT in 1987 [18]. Figure 6 depicts this first bipolar electric device and its operation method [55]:

**Fig.6** Photograph **(a)** and sketch **(b)** of the first bipolar point-contact transistor invented by Bardeen and Brattain in Bell Labs 1947. Point-contact transistor circuits with broad **(c)** and short **(d)** distance between the two Ge pn-junctions [55-57].

This transistor construction (visible in Fig. 6(a)-(b)) consisted of a plastic triangle with a thin gold (Au) sheet attached to both side surfaces. The Au sheet was split in two pieces to create at the bottom a gap in between. The plastic triangle itself was pressed with a spring on a chunk of electron-rich Ge (n-Ge), which was the reason to call this device the Point-contact transistor. Finally, this used chunk of n-Ge was located on a copper (Cu) plate with a voltage source. As the Ge crystal with the Cu-plate forms the base of this point contact device, this electrode was named later on the base electrode contact. In that way, this device construction produced two electrically isolated Au contacts very close to each other on the surface of the n-Ge crystal. Since n-Ge crystal surfaces were rather defective back in these days, bulk electrons could be easily trapped by a large numbers of surface states, creating

thus a thin p-type inversion layer (p-Ge) next to the surface of the n-Ge chunk. Figuratively spoken, the two Au electrodes contacted in this way two pn-junctions: One was named the emitter-base (EB) and the other was called the collector-base (CB) circuit (Fig. 6(c)). If now the distance between these two pn-junctions was large, these two circuits would act independently (Fig. 6(c)). During operation, the EB circuit was forward-biased with a small current (e.g. 0.75 mA) by applying a small positive potential (e.g. 0.2 V) at the emitter contact. Otherwise, the CB circuit was in the same time reversed-biased (i.e. no current flows) by applying a bigger positive potential (e.g. 25 V) between collector and base contact. However, since the two Au sheets were very close to each other (about 0.005 cm in the classical device), the two existing circuits influenced each other (Fig. 6(d)). In the forwardbiased EB circuit, holes injected into p-Ge traveled partly over the adjacent p-type inversion layers into the p-Ge of the reversed-biased CB circuit. These additional positive charge carriers cause a reduction in the effective negative collector voltage and thus the band bending of the pn-junction there. In consequence, due to the bigger potential drop (e.g. 25 V) in the reversed-biased CB circuit, a bigger current (e.g. 2.5 mA) to flow. In other words, a small current (e.g. 0.75 mA) controls a bigger one (e.g. 2.5 mA). This amplification effect is the fundamental mechanism in bipolar transistor devices. For example, a small EB current form microphone can drive a light bulb in the CB circuit to follow the music [45, 46, 55-57].

Hetero-bipolar transistor: It is to mention that, Ge was used at first as semiconductor material of choice back in the days, due to the possibility to grow Ge crystals with high purity. Furthermore, due to the extraordinarily large diffusion length of minority carriers in Ge, it allowed to prepare functional devices despite the large device dimension in early days. Even though the first transistor was fabricated in Ge, Si emerged very fast as the dominant semiconductor material after having improved Si crystal growth methods and Si microstructure processing [18, 44]. Already in 1954, the first Si BJT was presented by Teal [18]. The first diffused Si BJT followed in 1956, and the first epitaxial grown Si BJT was finally reported in 1960 [58, 59]. Since 1987, there was a renaissance of Ge in form of the first functional SiGe HBT demonstrated by IBM [60]. These pioneering works opened the way to the further evolution of HBT devices: From the first SiGe HBT demonstrated using chemical vapor deposition (CVD) growth technique in 1989 [61], over the discovery in 1996 that incorporating small amounts of carbon (C) into a SiGe base epitaxial layer strongly retards the diffusion of the Boron (B) doping during subsequent thermal cycles [62],

up to the first high-performance, fully integrated SiGe:C HBT technology reported in 1999 [63]. In the following, bipolar device physics is reviewed to set the basis for the approaches used in this thesis to improve HBT performance.

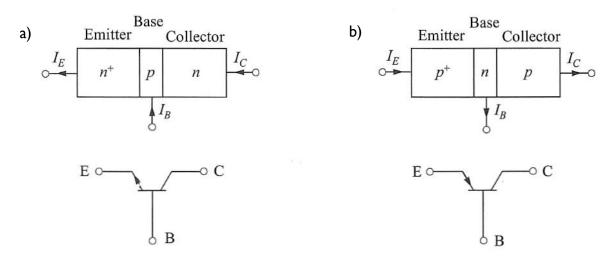

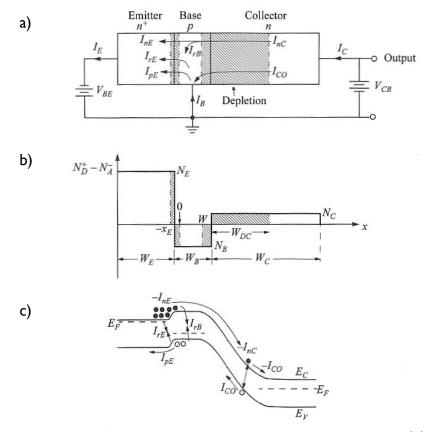

**Device Physics:** There are two kinds of bipolar devices conceivable: the n-p-n type which has a p-type base and n-type emitter and collector, and the p-n-p type which has an n-type base and p-type emitter and collector [45, 46]. Figure 7 depict the symbols and nomenclatures for both bipolar transistor types:

Fig.7 Symbols and nomenclatures of (a) n-p-n transistor and (b) p-n-p transistor.  $I_E$ ,  $I_B$  and  $I_C$  are the emitter, base and collector current, respectively [45].

The arrows indicate the conventional technical direction of current flow under normal operation condition, i.e. a forward-biased EB junction and a reverse-biased CB junction. In this section, only the standard n-p-n type bipolar transistor will be considered here, because the vertical n-p-n type is predominantly used today in all high-speed digital circuits. The reason for this is given by the much higher charge carrier mobility of electrons in contrast to

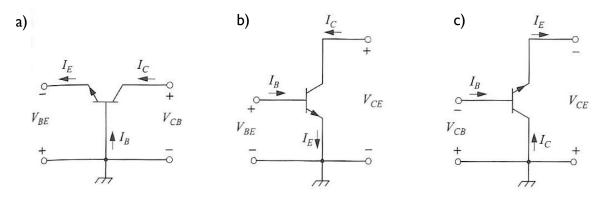

Fig.8 Three circuit configuration of n-p-n transistors in normal mode: (a) common-base, (b) common-emitter, and (c) common-collector [45].

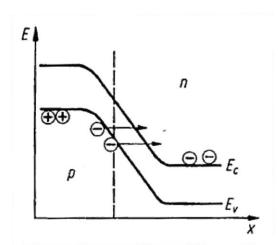

**Fig.9** An n-p-n type HBT biased in the normal operating condition. **(a)** Concentration and biases in common-base configuration. **(b)** Doping profiles and critical dimensions with abrupt impurity distribution. **(c)** Energy-band diagram. Current components are shown in **(a)** and **(c)**. Note that in **(c)**, flow of electrons is negative current because of negative charge [45].

holes in Si-based materials [18, 45, 46]. Depending on which lead is common to input and output circuits, three circuit configurations are known to connect a bipolar transistor: common-base, common-emitter and common-collector configuration (visible in Fig. 8).

Figure 9 shows interrelated sketches of an n-p-n type bipolar transistor, displaying connection and biases in common-base configuration (a), doping profiles and critical dimensions with abrupt impurity distributions (b) and the band diagram (c) [45]. In order to define the three terminal currents  $I_E$ ,  $I_B$  and  $I_C$ , it is helpful to describe first the different current components existing in the normal operation condition:

Electron injection current from the emitter into the neutral base ( $I_{nE}$ ): Simply spoken, a bipolar transistor device consists of two interconnected pn-junctions, over which an electron current flows from the emitter through the base into the collector. Due to the electron transport over the p-type base, the BJT is also classified as a minority carrier

device. Based on this, one important diffusion electron current component is  $I_{nE}$  between x = 0 and x = W (visible in Fig.9(a)-(b)). The other one, known as  $I_{nC}$ , consequently is the amount of electrons actually reaching the collector in the end. The ratio between  $I_{nE}$  and  $I_{nC}$  is called the base transport factor  $\alpha_T$ . It is defined as [45]:

$$\alpha_T = \frac{I_{nC}}{I_{nE}} \tag{3}$$

Assuming no current loss through recombination in the neutral base ( $I_{rB}$ ), it can be estimated that  $I_{nE} \approx I_{nC}$ , or  $\alpha_T \approx I$ . In this case  $I_{nE}$  and  $I_{nC}$  can be defined as [45]:

$$I_{nE} \approx I_{nC} \approx \frac{2A_E D_n Q_B}{W^2} \tag{4}$$

where  $A_E$  is the cross-sectional area of the EB junction,  $D_n$  is the diffusion coefficient for electrons and W is the natural base thickness.  $Q_B$  is the injected excess charge in the base and defined as [45]:

$$Q_{B} = q \int_{0}^{W} \left[ n_{p}(x) - n_{p0} \right] dx \approx \frac{qW n_{p0}}{2} e^{\frac{qV_{EB}}{kT}}$$

(5)

where q is unit electron charge,  $n_p$  is the electron concentration in p-type semiconductor (minority carriers), and  $n_{p0}$  is  $n_p$  in thermal equilibrium.

In Si bipolar transistor technique, there are two common ways known to improve  $\alpha_T$  towards unity in order to increase  $I_{nC}$  [18, 45, 46, 64]: I) Replacing the uniform doping in the base layer by a graded one, and 2) Introducing Ge content with different profiles into the base layer.

Because of this, the electronic band structure in the base layer can be engineered so that an additional built-in electric field is created there, enhancing the electron transport by extra drift action [45, 46]. Because introducing Ge into the base changes the built-in drift field in the base more effectively than a graded doping profile and allows in addition to reduce the conduction band offset between emitter and base, this technique paved the way for the HBT success over the BJT. For reasons of clarity, these important aspects of HBTs will be discussed at the end of this section in more detail.

Hole injection current from the base into the emitter ( $I_{pE}$ ): In reality,  $\alpha_T$  is usually smaller than unity due to  $I_{rB}$ , and other current components (beside  $I_{nE}$  and  $I_{nC}$ ), which also have to be taken into account. One of this components is the hole diffusion current  $I_{pE}$ , which is the main component of  $I_{B}$ . Its equation follows the hole distribution and current of a regular pnjunction [45]:

$$I_{pE} = \frac{A_E D_{pE} p_{n0E}}{W_E} \left[ e^{\frac{qV_{EB}}{kT}} - 1 \right]$$

(6)

where  $D_{pE}$  is the diffusion coefficient for holes in the emitter,  $p_{n0E}$  is the hole concentration in n-type emitter (minority carriers) in thermal equilibrium, and  $W_E$  is the total emitter width. It is to note here that  $I_{pE}$  corresponds well to the I-V characteristic of a typical pnjunction and is very much determined by the parameters of the receiving side (in this case the emitter side).

Recombination current at EB junction ( $I_{rE}$ ): Another component for base current is the recombination current  $I_{rE}$ . This current is proportional to [45]:

$$I_{rE} \propto \frac{1}{\tau} e^{\frac{qV_{EB}}{m_f kT}} \tag{7}$$

where  $m_f$  is a fitting factor (usually close to two). The factor  $I/\tau$  is the effective minority-carrier lifetime in n-type emitter. This term combines the (in indirect semiconductor dominating) Shockley-Read-Hall electron-hole generation-recombination process and the Auger recombination, which occurs when holes are injected into an  $n^+$ -doped emitter and recombine there by transferring the energy to another free electron [45, 46].

Reverse current at CB junction ( $I_{C0}$ ): Finally, we consider the reverse  $I_{C0}$ , which is given by [45]:

$$I_{C0} \approx A_C q \left( \frac{D_{pC} p_{n0C}}{W_C - W_{DC}} + \frac{D_n n_{p0}}{W} \right)$$

(8)

where  $A_C$  is the CB cross-sectional area,  $D_{pC}$  is the diffusion coefficient for holes in the collector,  $p_{n0C}$  is the hole concentration in n-type collector (minority carriers) in thermal equilibrium,  $W_C$  is the total collector width, and  $W_{DC}$  is the depletion width of the collector side.

<u>Current Gain:</u> After consideration of all different current components, the three terminal currents  $I_E$ ,  $I_B$  and  $I_C$  can be formulated with the help of Fig. 9 and Kirchhoff's law (equation (9)) as follows [45]:

$$I_E = I_C + I_B \tag{9}$$

$$I_E = I_{nE} + I_{rE} + I_{pE} (10)$$

$$I_B = I_{pE} + I_{rE} + (I_{nE} - I_{nC}) - I_{CO}$$

(II)

$$I_C = I_{nC} + I_{CO} (12)$$

After determining the terms for all terminal currents, it is possible to introduce two more important parameters: The common-base current gain  $h_{FB}$  (or  $\alpha_0$ ) and the common-emitter current gain  $h_{FE}$  (or  $\beta_0$ ), which express the unique amplifying feature of bipolar transistors (remember the point contact transistor part). Both values are roughly given by [45, 46, 64]:

$$h_{FB} \equiv \alpha_0 \equiv \gamma \alpha_T = \frac{I_{nE}}{I_E} \frac{I_{nC}}{I_{nE}} \approx \frac{I_C}{I_E} \tag{13}$$

$$h_{FE} \equiv \beta_0 \equiv \frac{\alpha_0}{1 - \alpha_0} \approx \frac{I_C}{I_B} \tag{14}$$

where  $\gamma$  is the emitter injection efficiency. Targeting in today's well-designed bipolar transistor a value of  $\alpha_0$  close to unity, values for  $\beta_0$  are much larger than one. For example if  $\alpha_0$  is 0.99,  $\beta_0$  is 99; and if  $\alpha_0$  is 0.998,  $\beta_0$  is 499 [45].

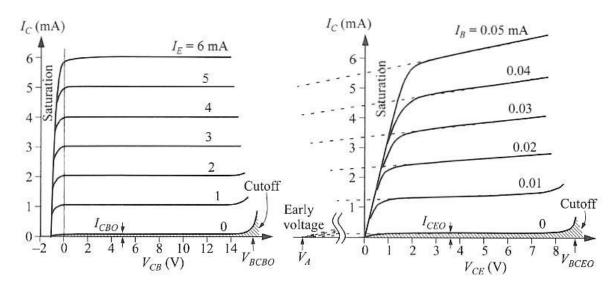

<u>Output Characteristics:</u> Next, we take a closer look on Fig. 10, which depict the I-V characteristics of an n-p-n bipolar transistor connected in two different circuit configurations:

First, we start with the idealized *common-base configuration* (see Fig. 8(a), Fig. 10(a)), where  $I_C$  is practically equal  $I_E$ , because  $\alpha_0$  is close to unity. Additionally,  $I_C$  does not change over a wide range of  $V_{CB}$  values (this means that all electrons from the emitter are effectively injected in the collector over wide  $V_{CB}$  range) and does not even vary down to zero volts for  $V_{CB}$ . This means that, even at zero volts for  $V_{CB}$  (but a finite  $V_{BE}$  value), excess electrons from the base are still extracted by the collector. For negative  $V_{CB}$ , the CB junction switches from reverse biased to forward biased, letting the bipolar transistor enter the saturation mode.

**Fig. 10** Output characteristic of an n-p-n bipolar transistor in **(a)** common-base configuration, and **(b)** common-emitter configuration. Breakdown voltage and Early voltage V<sub>A</sub> are indicated [45].

In this mode, the electron concentration at x = W (remember Fig. 9(b)) increases strongly up to a level at x = 0, reducing significantly the diffusion current through the neutral base and causing  $I_C$  to drop rapidly to zero. The collector saturation current  $I_{CB0}$  is measured with the emitter open-circuit, which means that the emitter junction is short-circuited ( $V_{BE} = 0$ ). In this state,  $I_E$  is zero that reduces the amount of electrons at x = 0 and the electron gradient towards x = W. This is the reason why  $I_{CB0}$  is smaller than the ordinary reverse current of a pn-junction (whose value is given by equation (8)). As  $V_{CB}$  increases to the collector-base open-emitter breakdown voltage  $V_{BCB0}$  value,  $I_C$  starts to increase rapidly due to the avalanche breakdown of the CB junction. For a very narrow base width or a base with relatively low doping, the breakdown may also occur by the punch-through effect. This means that the neutral base width is reduced to zero and the collector depletion region is in direct contact with the emitter depletion region. At this point, the collector is effectively short-circuited to the emitter and a large current can flow [45, 46, 64].

Now, we consider the idealized *common-emitter configuration* (see Fig. 8(b), Fig. 10(b)). In this case, the voltage  $V_{CE}$  is divided between two junctions to give the EB junction a smaller forward bias, and the CB junction a larger reverse bias in normal operation mode. Due to large reversed biased CB junction, the excess electron density at x = W is very low. Otherwise at x = 0, the excess electron density reaches very large values due to (even small) forward biased EB junction. Because of the exponential dependence, even small changes in

$V_{BE}$  (or better  $I_B$ ) are enough to change the excess electron density at x=0 and subsequently increase/decrease  $I_C$  by a large value (corresponding to  $\beta_0$  above). Remarkably,  $I_C$  increases slightly by raising  $V_{CE}$ . This observable effect is called the *Early-Effect* and originated from the enlargement of CB depletion region with increasing  $V_{CE}$ . As the result, the neutral base width W decreases, causing on the one hand a lesser chance for recombination within the base and on the other hand an increased electron gradient across the base. Both factors results in both higher  $I_C$  and higher  $\beta_0$ , simultaneously. For a bipolar transistor with base width  $W_B$  much larger than the depletion region in the base, the Early voltage is given by [45, 46, 64]:

$$V_{A} \approx \frac{q D_{n}(W_{B}) n_{i}^{2}(W_{B}) W_{B}}{\varepsilon_{S}} \int_{0}^{W_{B}} \frac{N_{B}(x)}{D_{n}(x) n_{i}^{2}(x)} dx$$

$$\approx \frac{q N_{B} W_{B}^{2}}{\varepsilon_{S}}$$

(15)

for a uniform base (where  $\epsilon_s$  is the permittivity of the semiconductor and  $n_i$  the intrinsic carrier concentration). The Early voltage  $V_A$  can be determined by extrapolating to the point where the output curves meet (visible on the left in Fig. 10(b)). However, when  $V_{CE}$  is decreased below a certain value (  $\approx$  I V for Si BJTs),  $I_C$  falls rapidly to zero. Similar to the common-base configuration, the CB junction will switch from reverse bias to forward bias and drive the bipolar transistor into saturation mode, if  $V_{CE}$  is further reduced. The collector saturation current  $I_{CE0}$  is measured with the base open-circuit, which is the  $I_C$  with zero base current. Here,  $I_{CE0}$  is much larger than  $I_{CB0}$ , because the open base physically floats to a slightly positive potential, increasing the electron concentration and its diffusion gradient in the base. Similar to the common-base configuration, an avalanche breakdown appears in the CB junction after reaching a certain high  $V_{CE}$  value ( $V_{BCE0}$ ). Interestingly,  $V_{BCE0}$  is much smaller than the junction breakdown voltage  $V_{BCB0}$ , due to the positive feedback from the bipolar gain [45].

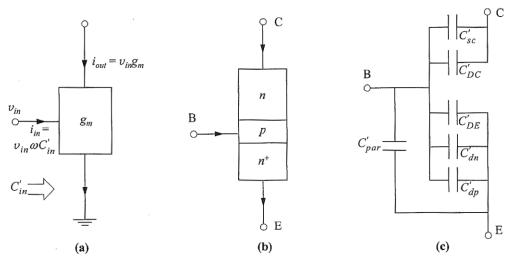

High frequency properties: Next, we present shortly the main aspects of the microwave characteristics for bipolar transistors. One of the most important parameter is the transit cutoff frequency  $f_T$ . This parameter can be defined as the frequency at which  $\beta_0$  is unity. For any transistor using the equivalent circuit of Fig. 11(a),  $f_T$  can be described by the following expression [45]:

$$f_T = \frac{g_m}{2\pi C_{in}} \tag{16}$$

where  $g_m$  is the transconductance and  $C'_{in}$  the total input capacitance. In BJT (Fig. 11(b)-(c)), the components of  $C'_{in}$  are represented by the sum of [45]:

$$C_{in}^{'} = C_{par}^{'} + C_{dn}^{'} + C_{dp}^{'} + C_{DE}^{'} + C_{DC}^{'} + C_{sc}^{'}$$

(17)

where  $C'_{par}$  is the parasitic capacitance,  $C'_{dn}$  is the diffusion capacitance due to electrons in the base,  $C'_{dp}$  is the diffusion capacitance due to holes into emitter,  $C'_{DE}$  is the emitter-base depletion capacitance,  $C'_{DC}$  is the collector-base depletion capacitance and  $C'_{sc}$  is the space-charge capacitance in the collector due to the injected electrons. Considering the transit time  $\tau$  as the individual charging time or delay time associated with each capacitance  $C'/g_m$ ,  $f_T$  can be rewritten as [45, 64]:

$$f_T = \frac{1}{2\pi \sum (C'/g_m)} = \frac{1}{2\pi \sum \tau}$$

(18)

revealing  $f_T$  as inverse of the sum of transit times which takes an electron to travel from the emitter to the collector contacts. Entering the equations for  $C'_{dn}$ ,  $C'_{dp}$  and  $C'_{sc}$  from the literature, the overall transit cutoff frequency can be finally defined as [45]:

$$f_{T} = \left\{ 2\pi \left[ \frac{kT \left( C_{par} + C_{DE} + C_{DC} \right)}{qI_{C}} + \frac{W^{2}}{\eta D_{n}} + \frac{W_{E}W}{\theta D_{n}} + \frac{W_{DC}}{2 v_{sat}} + R_{C}C_{DC} \right] \right\}^{-1}$$

(19)

where  $\eta$  and  $\theta$  are design parameters, W is the natural base width, W<sub>E</sub> is the emitter width, W<sub>DC</sub> is the collector-base space charge width, v<sub>sat</sub> is the saturation velocity in W<sub>DC</sub> and R<sub>C</sub> is the total collector resistance [18, 46, 65].

**Fig. 11** Schematic circuits to analyse  $f_T$ : (a) A transistor having  $g_m$  and  $C'_{in}$ . (b) Representation of n-p-n HBT, and (c) its input capacitance components [45].

Another important figure-of-merit which characterizes the speed of the transistor is the maximum frequency of oscillation  $f_{max}$  and is defined as [45]:

$$f_{max} = \sqrt{\frac{f_T}{8\pi R_B C_C}} \tag{20}$$

with  $R_{\scriptscriptstyle B}$  being the total base resistance and  $C^{\,\prime}_{\scriptscriptstyle \, C}$  the total collector capacitance [64].

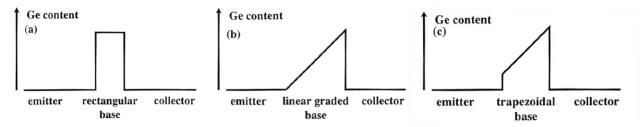

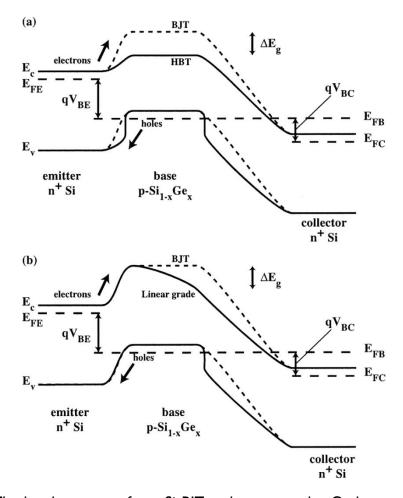

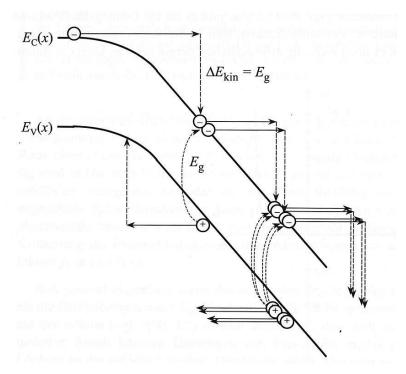

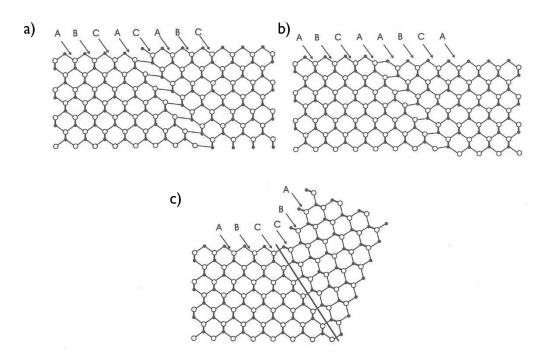

<u>SiGe HBT versus Si BJT:</u> Up to this point, the presented theoretical background corresponds to both BJT and HBT. To explain the historical success of the HBT over the BJT, we have finally to consider the effects of introducing Ge into the base layer, creating in this way a hetero-junction bipolar transistor device. In general, three main designs of adding Ge into the base of a HBT exist, as depicted in Fig. 12: The rectangular or box SiGe base (a), the linearly graded SiGe base (b) and the trapezoidal SiGe base (c), which is a compromise between the two designs named in advance [64]:

Fig. 12 The three main Ge base profiles for SiGe HBTs. (a) the rectangular or box SiGe base, (b) the linearly graded SiGe base and (c) the trapezoidal SiGe base [64].

Depending on the used Ge profiles, the main parameters of the HBT will be modified in different ways, creating individual benefits for the operation of the device. In Fig. 13, the band structure modifications of both rectangular (a) and the linearly graded (b) Ge profiles are shown [64]. The most obvious advancement by using a rectangular Ge base profile with respect to a standard BJT is the decrease in height of the conduction band in the base (see Fig 13(a)). This results in a reduced potential barrier at EB and CB junction, increasing  $I_C$ ,  $V_A$  and emitter transit time  $\tau_E$  by a factor  $e^{\frac{\Delta E_g}{k_B T}}$  [64]. Certainly,  $\Delta E_g$  depends on the Ge content x, and is given at low Ge content by [64]:

$$\Delta E_a = 0.0206x^2 - 0.43x [eV] \tag{21}$$

**Fig.13** (a) The band structure for a Si BJT and a rectangular Ge base profile HBT. (b) The band structure for a Si BJT and a linearly Ge graded SiGe HBT [64].

Unlike the Ge rectangular profile HBT, the linearly graded Ge base profile (see Fig. 13(b)) introduces a slanting base conduction band, creating an additional built-in drift field that accelerates the electrons across the base, reducing the base transit time  $\tau_B$ , improving  $\alpha_T$  and increases the bipolar gains ( $\alpha_0$  and  $\beta_0$ ). To benefit from both lower base conduction band and the additional built-in electric drift field, modern SiGe:C HBTs often use a trapezoidal base profile, which is simply a compromise of the Ge rectangular profile and the linearly graded Ge base profile (see Fig. 12(c)). However, process engineers often trade off the enhanced  $\beta_0$  and  $I_C$  for higher base doping concentration  $N_B$ , which allows thinner  $W_B$  and reduced  $R_B$ . Thereby,  $\tau_B$  will be reduced, what increases again in turn  $f_T$  and  $f_{max}$  [64].

## I.4. Goals of this thesis

Todays high-speed SiGe:C HBT BiCMOS technology can be fabricated up to  $f_T/f_{max}/common$ -emitter breakdown voltage ( $V_{BCE0}$ ) values of 300 GHz/500 GHz/1.6 eV and a minimum Current Mode Logic ring oscillator gate delay of 2.0 ps [25]. In order to fulfill the constant needs for ever faster SiGe:C HBTs with an adequate high power performance, it can be expected that future developments will further improve the frequency values entering into the THz regime [18, 23-25]. At the moment, different possible approaches are known which focus on fulfilling these tasks. Some of them are listed in the following [18]:

**Scaling of emitter area:** Aggressively scaling of the emitter area  $(W_E)$ , and therefore  $C_{BE}$  ( =  $C'_{par}$  +  $C'_{dn}$  +  $C'_{DE}$  (Fig. 11)), results by the following equation

$$\tau_E = \frac{kT}{q} \frac{C_{BE}}{I_C} \tag{22}$$

in a reduced emitter delay  $\tau_E$ . Considering equation (18) and the fact that  $W_E$  can be relatively easily scaled, it can be postulated that this mean will be used in future for  $f_T$  improvement [18].

**Base optimization:** The base transit time  $\tau_B$  is limited by the transit across W and the velocity of carriers to exit the base at the CB space charge region ( $v_{exit}$ ). Considering the following equation

$$\tau_B = \frac{kT}{\Delta E_{Ge}} \left( \frac{W^2}{\eta D_n} + \frac{W}{v_{exit}} \right) \tag{23}$$

where  $\Delta E_{Ge}$  is the grading in the base bandgap energy due to the introduced Ge content,  $\tau_B$  can be reduced by continuous shrinking of W using new process techniques (e.g. a combination of reduced thermal cycle) and by increased Ge content in the base to enhance the additional built-in electric drift field. This modification opens also the opportunity to improve  $f_T$  following equation (18) [18, 67].

Reducing collector– base capacitance  $C_{CB}$ : Considering the collector delay  $\tau_C$  component, given by

$$\tau_C = \left(R_E + R_c + \frac{kT}{qI_C}\right)C_{BC} \tag{24}$$

and equation (18), it is possible to improve  $f_T$  by reducing  $C_{CB}$  ( =  $C'_{sc}$  +  $C'_{DC}$  (Fig. 10)) by scaling the active CB capacitance area using todays improved device geometry and using structures like the raised extrinsic base to reduce the CB capacitance per unit area [18, 67].

Increasing collector doping  $N_c$ : Considering again equation (24), it is also favorable to increase  $N_c$  by e.g. vertical collector scaling in order to increase  $I_c$  and to push out the Kirk effect<sup>1</sup> what also reduces  $R_c$ . In consequence,  $\tau_c$  can be reduced and  $f_T$  increased following equation (18) [18].

Increasing saturation velocity  $\nu_{sat}$ : The transit time  $\tau_{CB}$  through the CB space charge region  $W_{DC}$  is given by

$$\tau_{CB} = \frac{W_{DC}}{2 v_{sat}} \tag{25}$$

It is a significant impediment for improving speed performance of future SiGe:C HBT's. Because  $v_{sat}$  is a material property and not easily influenced by the production process, SiGe:C HBT device designers are limited by the given carrier mobility for both electrons and holes in Si. Therefore, new ways towards new materials (i.e. III-V-HBTs) are under investigation to overcome this fundamental limit in speed performance [18].

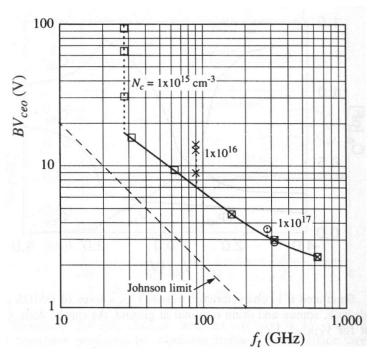

**Fig. 14** A plot showing the Johnson limit and the revised fundamental limit on  $f_T$  and  $V_{BCEO}$  for modern bipolar devices. Dotted lines represent regimes where collector depletion width  $(X_C)$  < collector width  $(W_C)$  when unbiased (so  $f_T$  is constant), but  $X_C > W_C$  (reach through) at breakdown. Solid line represents regimes where  $X_C > W_C$  (reach through) for both biased and unbiased [66].

\_

$<sup>^{1}</sup>$  High-field-relocation phenomenon in modern HBTs with lightly doped collector region, where the high-field region moves from the CB junction towards the collector  $n^{+}$ -substrate under high-current condition [45].

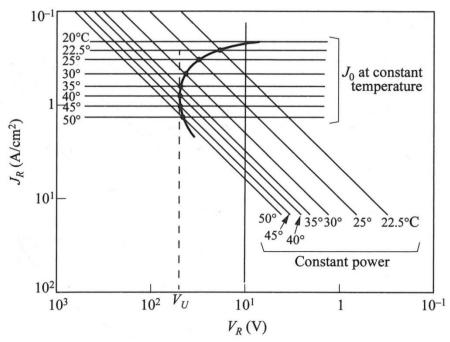

At the end, it is also to mention that another major problem still remains in SiGe:C HBT device technology, which will become more and more dominant with increasing speed performance. The three important parameters  $f_T$ ,  $V_{BCE0}$  and  $V_A$  are closely linked in form of a reciprocal relationship between the  $f_T$  and both  $V_{BCE0}$  and  $V_A$ . If the base and emitter profile of a HBT is constant,  $f_T$  can be improved by increasing  $N_C$  as well as making the collector shorter by decreasing the collector epitaxial layer thickness. Both of these methods result in a favorable delay of the Kirk effect onset [45, 67]. However, a disadvantage of increasing N<sub>C</sub> lies in the decrease of V<sub>A</sub> due to increased base-width modulation and the increase of impact ionization which lowers consequently  $V_{\text{BCE0}}$ . In addition, the reduction in collector epi-layer thickness also increases impact ionization due to the higher electrical field from the same voltage over a shorter distance. This shown trade-off behavior between  $f_T$  and both  $V_{BCEO}$  and V<sub>A</sub> has been first characterized as the Johnson Limit [66-68, 88]. Figure 14 show the revised fundamental limit on  $f_T$  and  $V_{BCEO}$  for modern bipolar devices, where for a fixed  $N_C$ , as the collector width is reduced,  $V_{\text{BCE0}}$  decreases and  $f_{\text{T}}$  increases [66]. This material related characteristic makes it difficult to combine high-speed with high-power performance for pure SiGe:C HBTs for future improvements and developments.

For this reason, the goal of this thesis is to find novel approaches to ensure further improvement of the SiGe:C HBT technology towards high-speed and high-power performance in order to close the THz gap. Based on this task, two strategies were investigated in this work:

# 1.4.1 Solid-phase epitaxy for emitter and base resistivity

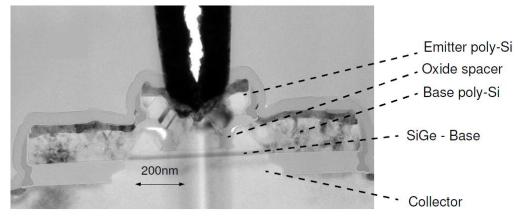

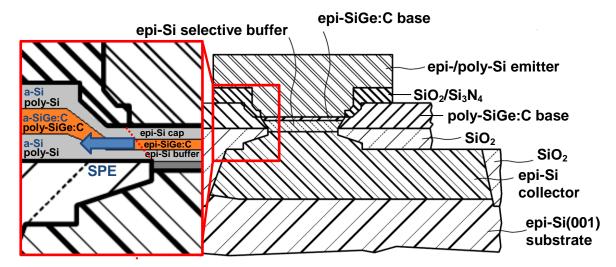

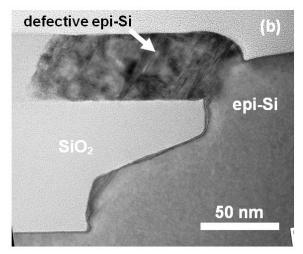

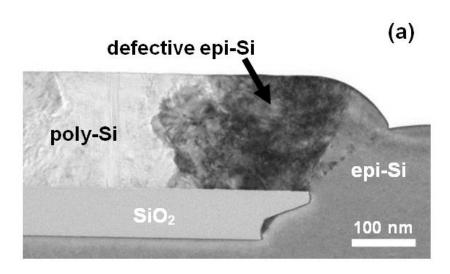

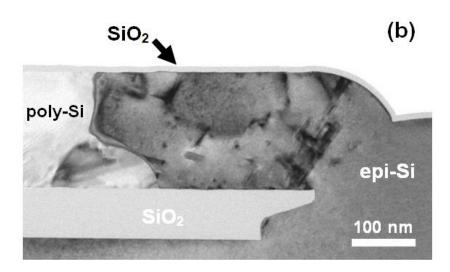

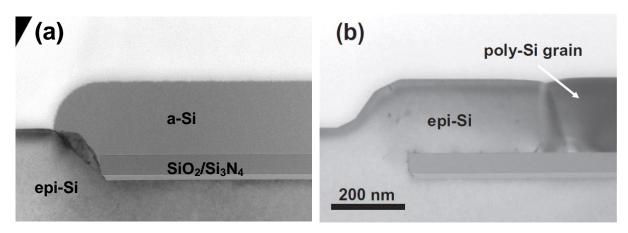

Solid-phase epitaxy (SPE) technique is used for local engineering of crystallinity in emitter and base layer of already established SiGe:C HBT device technology. Figure 15 shows a TEM micrograph of a current SiGe:C HBT device [25]. This approach offers an additional alternative to the above presented "scaling of emitter area" and "base optimization" approaches in order to improve HBT speed performance. By introducing disilane ( $Si_2H_6$ ) as new growth gas source with respect to standard used silane ( $SiH_4$ ) at IHP, it is possible to reduce the CVD growth temperature for Si, enabling in turn a differential growth of epitaxial-Si (epi-Si) on Si and amorphous Si (a-Si) (instead of poly-Si) on the SiO<sub>2</sub> and  $Si_3N_4$  masks. More basis background about the used SPE technique will be introduced directly in 3.1.1.

**Fig.15** TEM cross section of current SiGe:C HBT with  $f_T/f_{max}/V_{BCE0} = 300 \text{ GHz}/500 \text{ GHz}/1.6 \text{ V} [25]$

The so produced requirement for SPE treatments has been evaluated for two possible areas of application:

**Emitter region:** By changing the standard poly-Si emitter (see Fig. 15) to a fully epi-Si emitter using SPE techniques, the emitter contact resistance  $R_{Ec}$  and the bulk emitter resistance  $R_{Eb}$  can be reduced which results by the following relationship [81]

$$R_E = R_{EC} + R_{Eb} \tag{26}$$

in turn in a lower total emitter resistance  $R_E$ . A lower  $R_E$  concurrently increases  $I_E$ , improving (according to Kirchhoff's Law (remember equation (9)) in the end also  $I_C$ . Considering equation (18) and (19), increasing  $I_C$  will finally lead to higher  $f_T$  and  $f_{max}$  values.

**Base region:** By changing the standard poly-Si base link region on the mask (see Fig.15) to epi-Si using SPE techniques, the base contact resistance  $R_{Bc}$  and the external base link resistance  $R_{Be}$  following relationship [81, 133]

$$R_B = R_{BC} + R_{Be} + R_{Bi} (27)$$

can be reduced, resulting in turn in a lower  $R_B$ . Thereby,  $R_{Bi}$  is the internal base resistance under the emitter (pinched base). As already shown in equation (19), a reduction in  $R_B$  directly improves  $f_{max}$ .

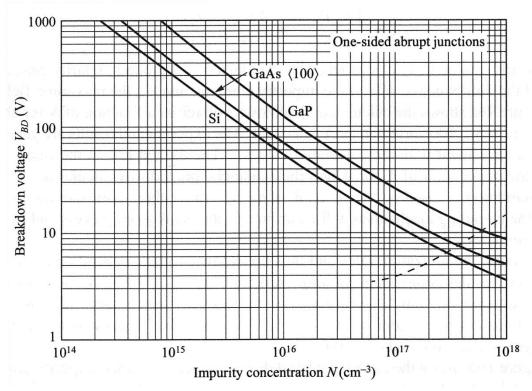

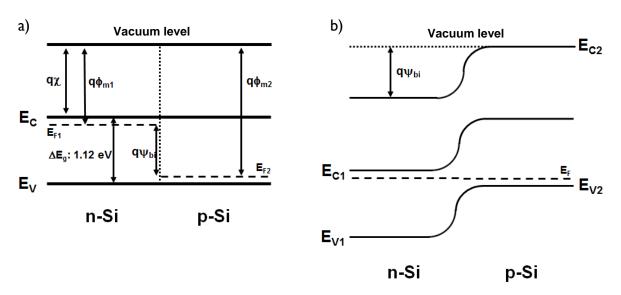

# 1.4.2 III-V/SiGe hybrid device: In<sub>1-x</sub>Ga<sub>x</sub>P collector

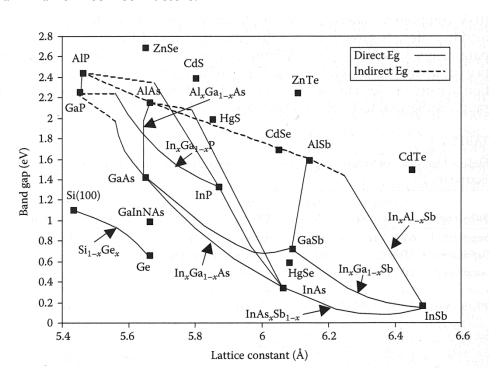

The ternary compound semiconductor Indium gallium phosphide ( $In_{1-x}Ga_xP$  [x = 0 - 1]) will be introduced as potential new collector material as part of an advanced III-V/SiGe

hybrid HBT device. Table I shows the main physical parameters of the binary materials Indium phosphide (InP) and Gallium phosphide (GaP) at 300 K, important for SiGe HBT speed and power performance increase, in comparison to Si [90]:

|                                                                      | Si                | InP                 | GaP             |

|----------------------------------------------------------------------|-------------------|---------------------|-----------------|

| Bandgap [eV]                                                         | 1.12              | 1.33                | 2.26            |

| Breakdown voltage [V cm <sup>-1</sup> ]                              | $3 \times 10^{5}$ | 5 × 10 <sup>5</sup> | $1 \times 10^6$ |

| Electron mobility [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | 1400              | 5400                | 250             |

| Saturation velocity [cm/s]                                           | $1 \times 10^7$   | $3 \times 10^7$     | $1 \times 10^7$ |

| Lattice constant [nm]                                                | 0.5431            | 0.5869              | 0.5451          |

**Tab.1** Important physical parameters of Si, InP and GaP (at 300 K) for SiGe HBT high frequency and power performance increase as well as heterostructure growth [90].

On the one hand, InP has a three times higher saturation velocity  $v_{sat}$  than Si [90], following the above presented "increasing saturation velocity  $v_{sat}$ " approach. On the other hand, the wide bandgap semiconductor GaP has a two times bigger bandgap than Si [90], which decreases impact ionisation rates in the collector [45, 46]. This offers a higher  $V_{BCE0}$  threshold and the possibility to run hence the HBT device under higher  $I_C$ , leading in the end to a higher power and speed performance (see equation (19)). In other words, ternary  $In_{I-x}Ga_xP$  systems as potential collector material provide the vision to adjust speed ( $f_T$ ;  $f_{max}$ ) and power ( $V_{BCE0}$ ;  $I_C$ ) of HBTs in a flexible way as a function of the  $In_{I-x}Ga_xP$  collector chemical composition x [90].

In the following, this Ph.D. thesis will evaluate the potential of these two new material approaches for next generations of future SiGe:C HBT BiCMOS technology.

#### 2. Experimental part

### 2.1. Thin film growth techniques

In this thesis, two different epitaxial growth techniques have been used and will be therefore briefly presented in the following:

Reduced pressure chemical vapor deposition: The reduced pressure chemical vapor deposition (RPCVD) is a subtype of the CVD growth technique, where the pressure of the reactor can be varied from atmospheric down to practically 10 Torr. Otherwise, RPCVD follows the known CVD process mechanism: Chemical precursors are transported in the vapor phase to a heated substrate and form there an overlayer by decomposition, adsorption and surface reaction. CVD has many noticeable advantages over physical vapor deposition techniques like e.g. molecular beam epitaxy (MBE) or sputtering. High throughput, purity, accurate and reproducible thin film deposition as well as low cost of operation are the main features. Another important and unique feature of CVD is the homogeneous thin film deposition on three-dimensional structures with high aspect ratio. All these advantages made by now CVD the major method of film deposition for the semiconductor industry, which certainly is a mass-production market. However, this growth technique has also some disadvantages in the way of in-situ monitoring of thin film growth and due to costs to develop the needed precursor chemistry. More details to this frequently developed growth technique can be found in various reviews in the literature [18, 38, 99, 100].

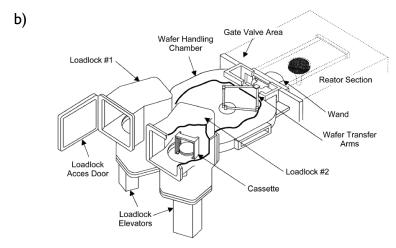

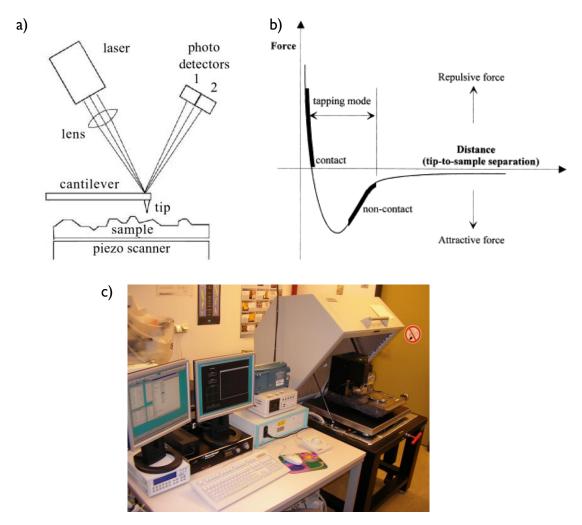

Figure 16 shows a cleanroom image (a) and a technical sketch (b) of the ASM Epsilon 2000<sup>™</sup> single wafer RPCVD reactor (similar to the one in IHP's cleanroom), which has been used in this thesis for Si/Ge growth and in-situ annealing experiments. This RPCVD model is designed for deposition on 200 mm (8 inch) Si wafers and consists of three main parts: The two load-locks, the wafer handling section and the process quartz chamber. The wafer handling section is equipped with a quartz wand Bernoulli arm to automatically transfer single wafers from the load-locks onto a silicon carbide coated graphite susceptor in the process chamber and vice versa. To avoid oxygen contamination during handling and storage, the two load locks and the wafer handling chamber are always purged with nitrogen (N₂) gas. Additionally, the two load locks can be pumped down and backfilled for entering and removing racks with 25 wafers. The susceptor itself consists of two parts: an outer fixed

Fig.16 Picture of an ASM Epsilon 2000<sup>™</sup> single wafer RPCVD reactor in a cleanroom (a) and the corresponding schematic illustration (b) [97].

body and an inner rotating plate, on which the wafer is positioned during the processing. The wafers have to be rotated during the CVD process to ensure a homogeneous deposition of material. Two sets of halogen tungsten lamps, located at top- and downside of the quartz glass chamber provide the susceptor with thermal radiation and enable growth and rapid thermal adjustments in the range of 300 - 1200 °C. Via pneumatic valves in the gate valve area, the following process gases can be injected into the reactor:  $SiH_4$ ,  $Si_2H_6$  and dichlorosilane ( $SiCl_2H_2$ ) as the Si sources, I.5% germane ( $GeH_4$ ) in hydrogen ( $H_2$ ) as Ge source and Simpsize Simp

both HCl and  $H_2$  gas pipes are equipped with an in-line purifier unit. The used gases during the process will be exhausted and neutralized in a scrubber and later disposed in a burner [97, 98].

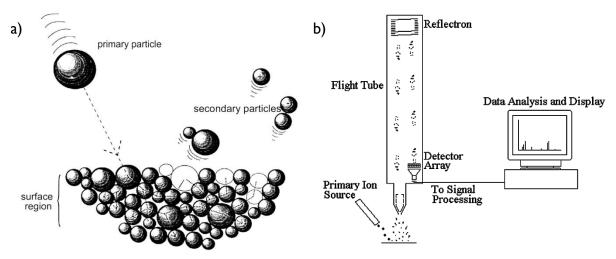

Gas-source molecular beam epitaxy: The gas-source molecular beam epitaxy (GSMBE) is a variation of the MBE growth technique, where gases instead of solid source materials are used in part or entirely as sources for growth materials typically in an ultrahigh vacuum (UHV). Otherwise, all MBE systems have the same underlying process mechanism: Molecular beams in form of fluxes of evaporated or cracked growth material and dopant species are directed on a heated substrate and react there towards an (e.g. epitaxial) overlayer. Compared to other growth techniques like e.g. CVD, MBE systems have the advantage to grow ultra-pure layers with atomic monolayer precision and to monitor the whole growth process in the same time in-situ by e.g. reflection high energy electron diffraction (RHEED). This fact makes MBE a favorite tool for versatile research efforts in the field of model system studies. Nevertheless, disadvantages also exist due to low throughputs and a limited three-dimensional coverage during the growth process. A lot of reviews in literature already refer to this growth technique, enabling better insight and more details [101, 102].

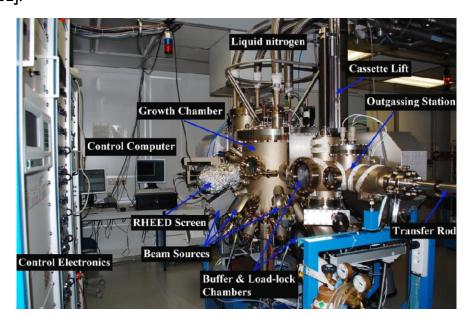

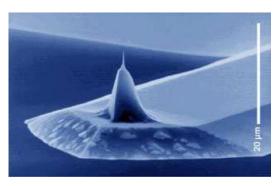

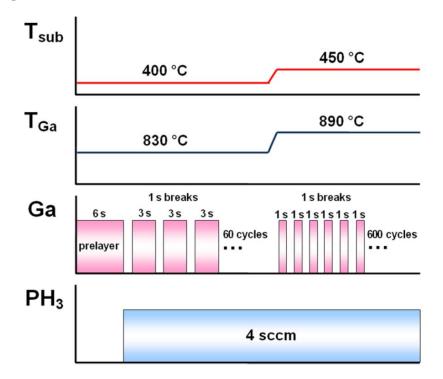

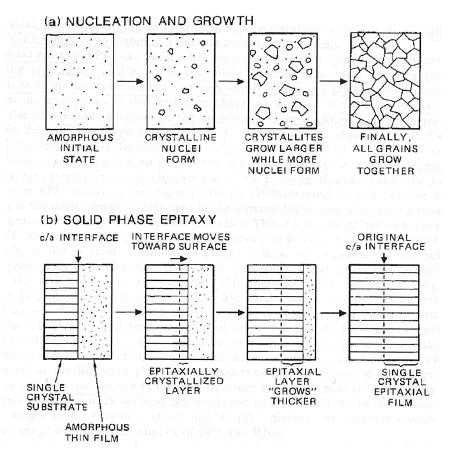

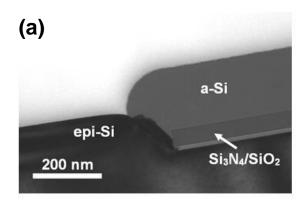

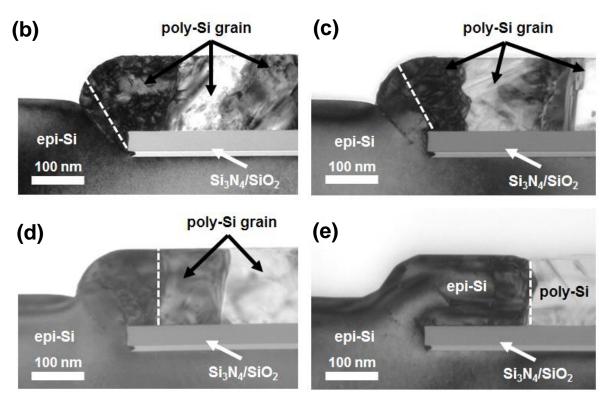

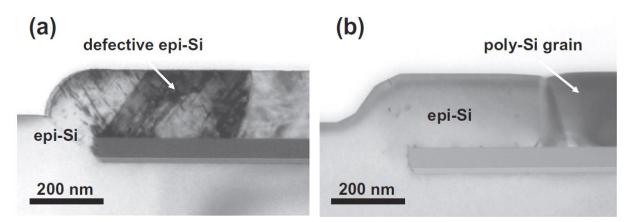

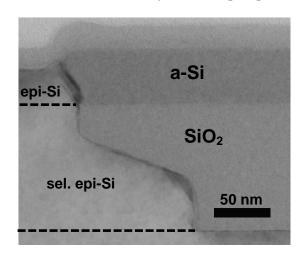

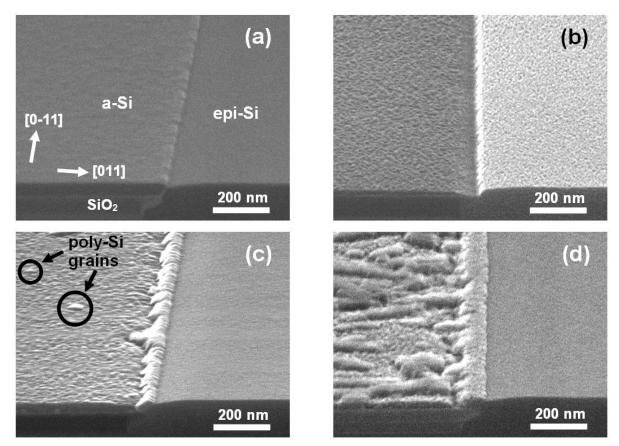

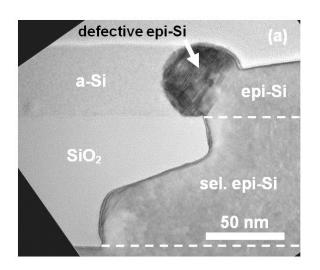

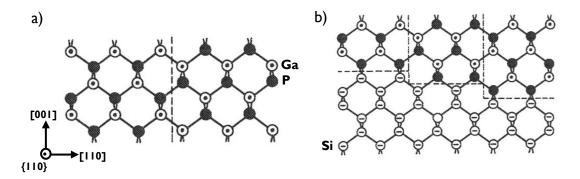

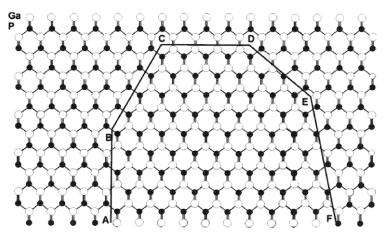

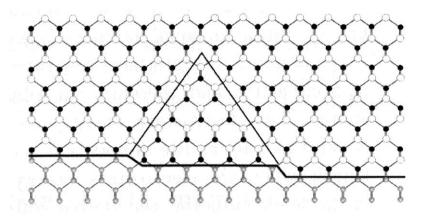

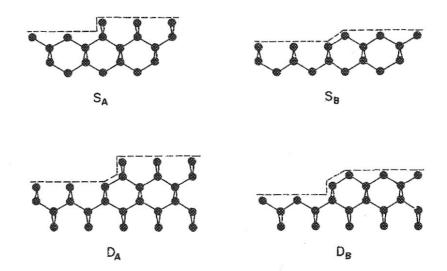

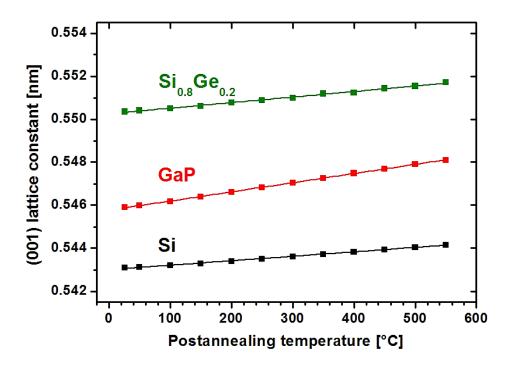

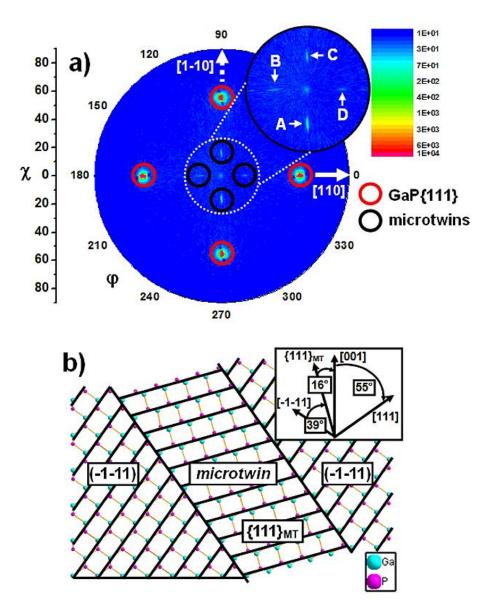

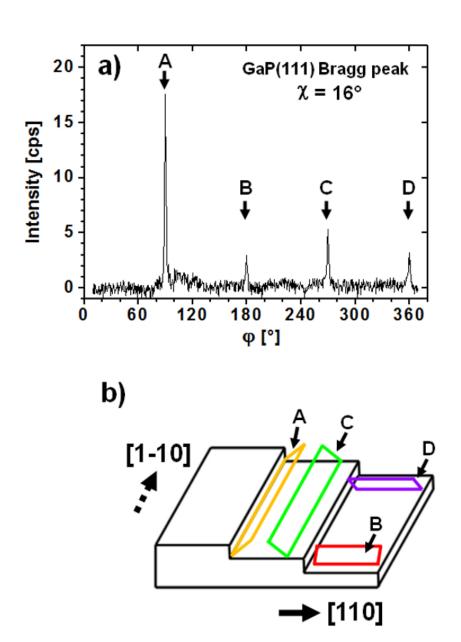

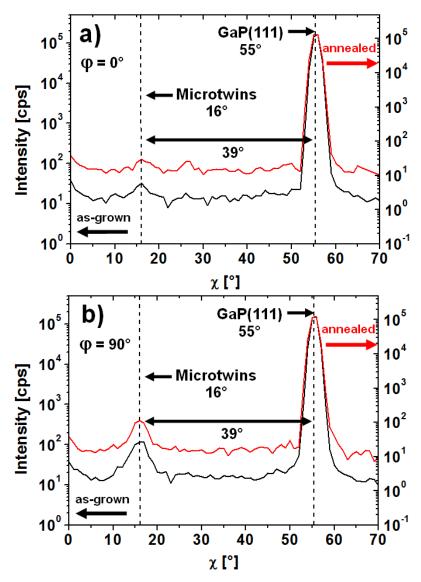

Fig.17 Picture of a Riber Compact 21T GSMBE reactor in a cleanroom [103].